1

Изобретение касается цифровой электроизмер.ителыной техники и .может найти широкое .применение при построении цифровых широкодиапазон1ных вольтметров ,и амперметров, действуюпдих значений периодических сигналов, .анализаторов гармоник, анализаторов частотных хара.ктеристик и т. д.

Известно устройство, содержащее блок упра.вления, .соединенный с управляющим входом первого вентиля, через -который генератор эталонной частоты .подключен к вычитающему счетчику, и с управляющим входом второго .вентиля, к сипнально.му входу «оторого подключен генератор эталонной частоты; сум.матор, выход которого через элемент задержки и элемент «ИЛИ .соедин ен с одним.и входами группы вентилей .переноса, другие входы которой соединены с выходами раз-рядов .вычитающего счетчика, дел.итель частоты с неременным коэффициентом деления.

Одна.ко для этого квантователя хара.ктерна невысокая точность, что обусловлено накопительны.м характером методической погрешности задания .моментов нреобразова.ния.

.Предложенный квантователь отличается тем, что для повышения его точности в него введен блок логических элементов «ИЛИ, одни входы которого соединены с выходом второго вентиля, другие входы - с соответствуюншми выходами группы вентилей переноса, а выходы подключены к соответствующим разрядам сумматора, выход которого соединен со входом делителя частоты с .неременньгм коэффициентом деления.

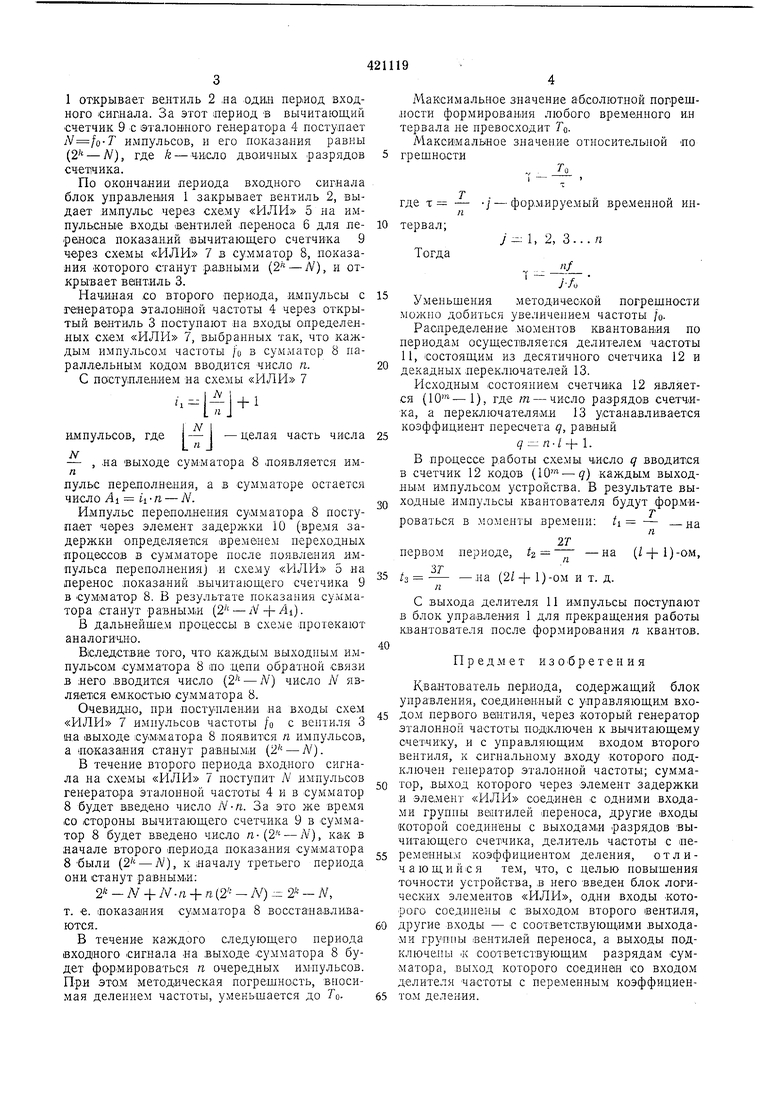

На чертеже представлена структурная схема .квантователя.

Квантователь содержит блок 1 управления, импульсно-потенциальные вентили 2, 3, генератор 4 эталонной частоты, эле.мент «ИЛИ 5,

группу вентилей б .переноса, группу логических элементов «ИЛИ 7, сумматор 8, вычитающий счетчик 9, элел1ент 10 задерж.ки и делитель 11 частоты с переменным коэффициентом деления.

Блок управления 1 служит для формирования импульсов, соответствующих началу и концу периода входного сигнала, и управления работой остальных элеме.нтов. Счетные входы триггеров сум.матора 8 через группу

элементов «ИЛИ 7 и группу вентилей переноса 6 поразрядно подключены к выхода1м триггера вычитающего счетчнка 9 так, чтобы из вычитающего счетчика 9 в сумматор 8 .переносился прямой код зап.исанного в нем числа при поступлении сигнала со схемы «ИЛИ 5 на импульсные входы вентилей нере.носа 6. В исходном положении вычитающий счетчик 9 и сум.матор 8 находятся в нулевом состоянии, импульсно-потенциальные вентили 2 и 3

закрыты. По сигналу пуска блок управленчя 1 открывает велтиль 2 ,на один период входного сигнала. За этот период -в вычитающий счетчик 9 с эталонного генератора 4 поступает импульсов, и его показа-ния равны (2 - Л), где k-число двоичных разрядов счетчика. По околчании периода входного сигнала блок управления 1 закрывает вентиль 2, выдает лмпульс через схему «ИЛИ 5 на импульсные входы вентилей лер;еноса 6 для пербноса показаний вычитающего счетчика 9 через схемы «ИЛИ 7 в сумматор 8, показания которого станут равными (2 - Л), и открывает вентиль 3. Начиная со второго периода, и.мпульсы с генератора эталонной частоты 4 через открытый вентиль 3 поступают на входы олределеллых схем «ИЛИ 7, выбранных так, что каждым импульсом частоты /о в сумматор 8 параллельным кодом вводится число п. с поступлением на схемы «ИЛИ 7 -т + шимпульсов, где |- | -целая часть числа - , л а выходе сумматора 8 лоявляется импульс переполлеиия, а в сумматоре остается число Ai ii-n - 7V. Импульс пераполлеаия сумматора 8 поступает через элемент задержки 10 (время задержки олределяется временем переходных процессов в сумматоре после поя,вле1ния импульса переполнелия) и схему «ИЛИ 5 на перенос локазалий вычитающего счетчика 9 в сум-матор 8. В результате показания сумматора станут равными (2 - ). В дальнейщем процессы в схеме лротекают аналогично. В|следствие того, что каждым выходным импульсом сумматора 8 по цепи обратной связи в лего вводится число (2 - N} число N является емкостью сумматора 8. Очевидно, при поступлении на входы схем «ИЛИ 7 и.мпульсов частоты /о с вентиля 3 иа .выходе :сум1матора 8 появится л импульсов, а локазалия сталут равными (2 - N). В течение второго периода входного сигнала на схемы «ИЛИ 7 поступит Л импульсов генератора эталонной частоты 4 и в сумматор 8 будет введено число N-n. За это же время со стороны вычитающего счетчика 9 в .сумматор 8 будет введено число п-(2 - N), как в начале второго -периода локазалия сумматора 8 были (2 - N), к лачалу третьего периода они станут равными: 2г - Л/ + /V-rt -f га(2 - АО - 2 - yV, т. е. локазания сумматора 8 восстанавливаются. В течение каждого следующего периода входного сигнала ла выходе сумматора 8 будет формироваться п очередных имлульсов. Пр.и этом методическая погрещность, ВЕЮСИмая делением частоты, уменьшается до То. Максимальное значение абсолютной погрешности формировал1ия любого временного ил тервала не превосходит Го. Максимальное значение относительной ло грешностл -, - JJL - / - формируемый временной ингде т - - тервал; J 1, 2, З...П Тогда т - У-/и Уменьшения методической погрещности можно добиться увеличением частоты /о. Распределение моментов квантовалия по периодам осуществляется делителем частоты 11, состоящим из десятичного счетчика 12 и декадных лереключателей 13. Исходным состоянием счетчика 12 является (Ю™-1), где т - число разрядов счетчика, а переключателями 13 усталавливается коэффициент пересчета q, равлый + l. В процессе р.аботы схемы число q вводится в счетчик 12 кодов (Ю™ - q} каждым выходным импульсом устройства. В результате выходные имлульсы квантователя будут формироваться в моменты времени: ti- - да п 2Т на (/ + 1)-ом, первом периоде, tz /3 (2/+1)-ом и т. д. С выхода делителя 11 импульсы поступают в блок упра1вления 1 для прекращения работы квантователя лосле формировалия п квантов. П р е д Д1 е т и з о б р е т е н и я Квантователь периода, содержащий блок управления, соединенный с управляющим входом первого вштиля, через который генератор эталонной частоты подключен к вычитающему счетчику, и с управляющим входом второго вентиля, к сигнальному входу которого подключен генератор эталонной частоты; сумматор, выход которого через элемент задержки а элемент «ИЛИ соединен с одними входами группы ве1нтилей лереноса, другие входы которой соединены с выходами разрядов вычитающего счетчика, делитель частоты с перемелныл коэффициентом деления, отличающийся тем, что, с целью повышения точности устройства, в него введен блок логических элементов «ИЛИ, одни входы которого соединены с выходом второго 1вентиля, другие входы - с соответствующими выходами группы вентилей переноса, а выходы подключены -к соответствующим разрядам сумматора, выход которого соединен со входом делителя ча-стоты с переменным коэффициелтом деления.

I„.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ФАЗА-ЧАСТОТА | 1972 |

|

SU420113A1 |

| УСТРОЙСТВО ФУНКЦИОНАЛЬНОЙ ВРЕМЕННОЙ ЗАДЕРЖКИ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 1971 |

|

SU310268A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Цифровой фазометр | 1976 |

|

SU597986A1 |

| УСТРОЙСТВО для ВЫЧИСЛЕНИЯ ДИСПЕРСИИ СЛУЧАЙНОГО ПРОЦЕССА | 1972 |

|

SU343273A1 |

| ЦИФРОВОЙ АНАЛИЗАТОР ЧАСТОТНЫХ ХАРАКТЕРИСТИК | 1969 |

|

SU238642A1 |

| ЦИФРОВОЙ РЕГИСТРИРУЮЩИЙ ДЕВИОМЕТР | 1973 |

|

SU374548A1 |

| УСТРОЙСТВО для ЗАДАНИЯ ТОЧЕК КВАНТОВАНИЯ ПЕРИОДИЧЕСКИХ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 1972 |

|

SU331316A1 |

| ИЗМЕРИТЕЛЬНЫЙ ПРЕОБР.ЛЗОВАТЕЛЬ Ч.ЛСТОТЫ | 1972 |

|

SU419799A1 |

| Статистический анализатор | 1973 |

|

SU478317A1 |

Даты

1974-03-25—Публикация

1972-05-03—Подача