Изобретение относится к радиотехнике и может быть использовано в из мерительных.информационных системах различного назначения.

Известен цифровой умножитель частоты следования импульсов, содержащий последовательно соединенные формирователь импульсов, блок управлени первый вентиль, первый делитель частоты выход которого подключен к второму входу блока управления, первый регистр памяти, первую схему переноса, второй делитель частоты и элемент И, к выходу которого/ являющемуся выходом цифрового умножителя частоты, подключен через элемент ИЛИ другой вход первого блока переноса, последовательно включенные между выходом первого и другим входом второго делителя частоты, второй регистр памяти, другой вход которого соедине с входом второго и выходом первого вентилей, второй блок переноса, другой вход которого соединен с выходом элемента И, параллельный сумматор, другой вход которого соединен с выходом третьего блока переноса, триггер задержки и третий вентиль, а также генератор импульсов эталонной частоты, выход которого соединен с вторыми входами триггера задержки, первого и третьего вентилей, при этом выход блока управления соединен с выходом третьей схемы переноса, с вторыми входами второго вентиля и элемента ИЛИ и третьим входом третьего вентиля |l3

Данный умножитель имеет невысокую точность умножения, работает только в стартстопнрм режиме,.т.е. не позволяет осуществлять непрерывное умножение меняющейся во времени частоты с заданной точностью/ обладает избыточным объемом используемого оборудования.

Наиболее близким по технической сущности к предлагаемому является

,цифровой умножитель частоты, содержащий последовательно соединенные формирователь импульсов, блок управления, первый вентиль, первый делитель частоты, первый счетчик импульсов, выход которого подключен к второму входу блока управления, первый регистр, первый блок.Переноса (блок элементов К), второй делитель частоты, второй счетчик импульсов и элемент И, к выходу которого являющемуся выходом цифрового умножителя частоты, подключен через эле|Мент ИЛИ другой вход первого блока шереноса, последовательно включенные между выходом первого и другим входом второго делителя частоты второй регистр памяти, другой вход которого соединен с входом второго и выходом первого вентилей, второй блок переноса Сйторой блок элементов к), другой вход которого соединен с выходом элемента И, параллельный сумматор, , другой вход которого соединен с выходом третьего блока переноса, триггер задержки и третий вентиль, а также генератор импульсов эталонной частоты ,о выход которого соединен с вторыми входами триггера задержки, первого и третьего вентилей, при этом выход блока управления соединен с входом третьего блока переноса, с вторыми входами второго вентиля и элемента ИЛИ и третьим входом третьего вентиля, между выходом второго вентиля и другим входом третьего блока переноса включены последовательно соединенные триггер и регистр сдвига, втоЕяле входы которых подключены к выходу блока управления, при этом третий вход блока управления соединен с выходом параллельного сумматора J

Известное устройство характеризуется недостаточно высокой точность умножения и сложностью.

Цель изобретения - повышение точности умножения при одновременном упрощении устройства.

Поставленная цель достигается тем, что в цифровой умножитель частоты следования импульсов, содержащий генератор опорной частоты, два счетчика импульсов, два регистра, первый формирователь импульсов, первый элемент ИЛИ, элемент задержки, три элемента И и первый и второй блоки элементов И, выходЬ которых подключены блоку элементов ИЛИ, выходы которого подключены к информационным входам сумматс а, введе- ны второй формирователь импульсов, третий счетчик импульсов и второй элемент ИЛИ, первый вход которого подключен к выходу первого элемента И, второй вход - к выходу генератора опорной частоты и сумкИрующему входу первого счетчика импульсов,выходы которого подключены к информационным входам первого регистра, а импульсный выход - к суммирующему входу второго счетчика импульсов, выходы которого подключены к . информационным входам второго регистра , выходы которого соединены с информационными входами третьего счетчика имйульсов, вычитающий Ьход которого соединен с выходом второго элемента ИЛИ, а суммирующий вход - с выходом второго элемента И, первый вход которого подключен к выходу второго формирователя импульсов и первому входу первого элемента И, второй вход которого подключен к входу переноса сумматора, нулевому выходу стариего разряда первого регистра и управляквдему входу-первого блока элементов И, информационные..входы которого соединены с нулевыми выходами остальных (младших ) .разрядов первого регистра, единичные выходы которых подключены к информационным входам второго блока элементов И, управляющий вход которого подкпю,чен к второму входу второго элемента И и единичному выходу старшего разряда первого регистра, управляющий вход первогю регистра соединен с управляю1цим вкодом второго регистра, первым управляющим входом сумматора, выходом первого формирователя импульсов, входом элемента задержки, выход которого подключен к установочным входам первог счетчика импульсов, второго счетчик импульсов и первому входу второго элемента ИЛИ, второй вход которого соединен с выходом тгретьего счетчик импульсов и первым входом третьего элемента И, а выход Ч с управляющим входом третьего счетчика импульсов и вторым управляющим входом сумматора |i выход которого подключен к входу второго формирователя импульсов, второй вход третьего элемента И подключен к шине блокировки, а выход является выxoдoJM устройства.

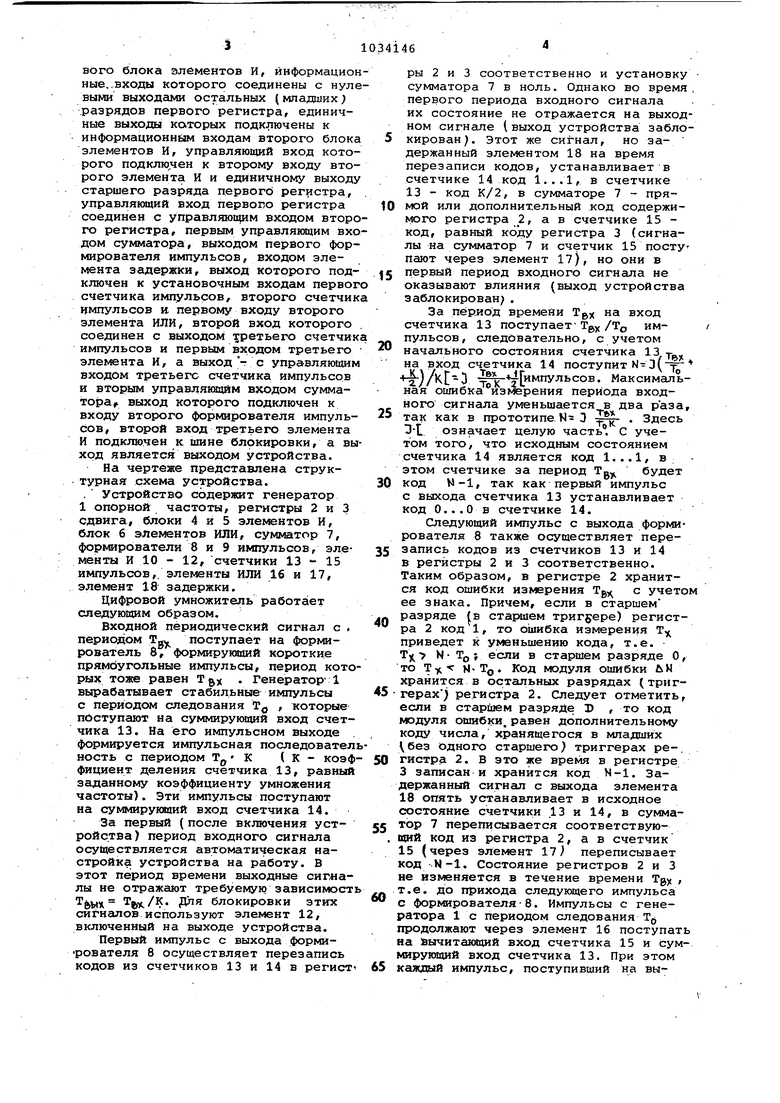

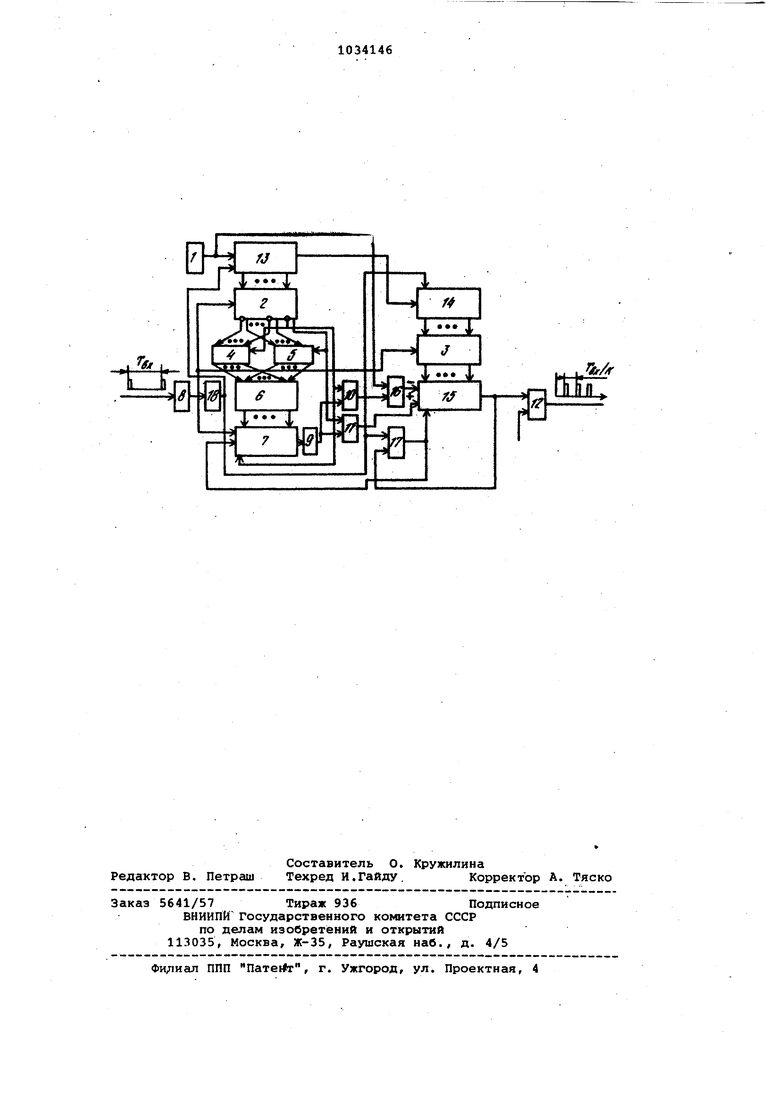

На чертеже представлена структурная схема устройства. . Устройство содержит генератор 1 опорной частоты, регистры 2 и 3 сдвига, блоки 4 и 5 элементов И, блок б элементов ИЛИ, сумматор 7, формирователи 8 и 9 импульсов, элементы И 10 - 12, счетчики 13 - 15 импульсов,, элементы ИЛИ 16 и 17, элемент 18 задержки.

Цифровой умножитель работает следующим образом.

Входной периодический сигнал с . периодом Tg поступает на Формирователь 8, формирукяяий короткие прямоугольные импульсы, период которых тоже равен Генератор 1 вырабатывает стабильные импульсы с периодом следования Т , которыепоступают на суммирукяций вход счетчика 13. На его импульсном выходе формируется импульсная последовательность с периодом Tjj К (К - коэффициент деления счетчика 13, равный заданному коэффициенту умножения частоты). Эти импульсы поступают на суммиругааий вход счетчика 14.

За первый (после включения устройства) период входного сигнала осуществляется автоматическая настройка устройства на работу. В этот период времени выходные сигяалы не отражают требуемую зависимость . ля блокировки этих сигналов используют элемент 12, включенный на выходе устройства.

Первый импульс с выхода формирователя 8 осуществляет перезапись кодов из счетчиков 13 и 14 в регист

ры 2 и 3 соответственно и установку сумматора 7 в ноль. Однако во время первого периода входного сигнала их состояние не отражается на выходном сигнале I выход устройства заблокирован). Этот же сигнал, но задержанный элементом 18 на время перезаписи кодов, устанавливает в счетчике 14 код 1...1, в счетчике 13 - код К/2, в сумматоре 7 - прямой или дополнительный код содержимого регистра 2, а в счетчике 15 код, равный коду регистра 3 (сигналы на сумматор 7 и счетчик 15 посту пают через элемент 17), но они в первый период входного сигнала не оказывают влияния (выход устройства заблокирован;.

За период времени на вход счетчика 13 поступает- Tgj( /Тд импульсов, следовательно, с учетом начального состояния счетчика 13 на вход счетчика 14 поступит М-3( + j/Kt-3 - у- Симпульсов. Максимальная оиюбка измерения периода входного сигнала уменьшается в два раза так как в прототипе N Э . Здесь 3, означает целую часть. С учетом того, что исходным состоянием счетчика 14 является код 1...1, в этом счетчике за период Tg будет код V1-1, так как первый импульс с выхода счетчика 13 устанавливает код 0...0 в счетчике 14.

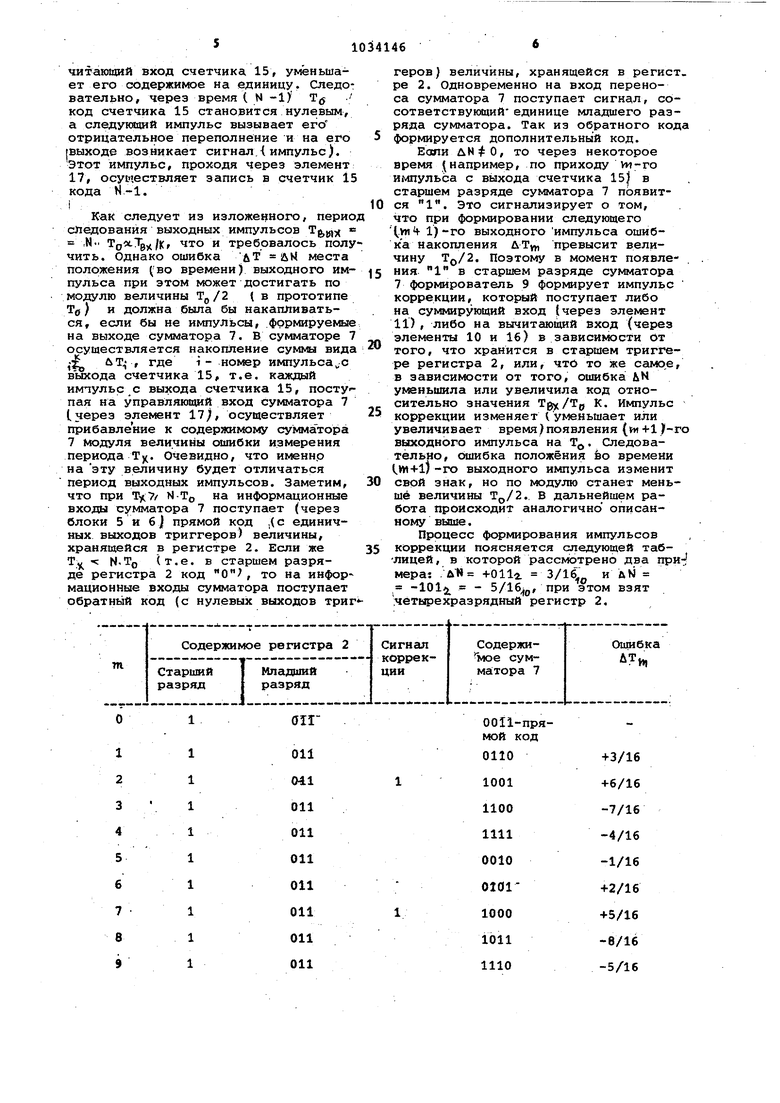

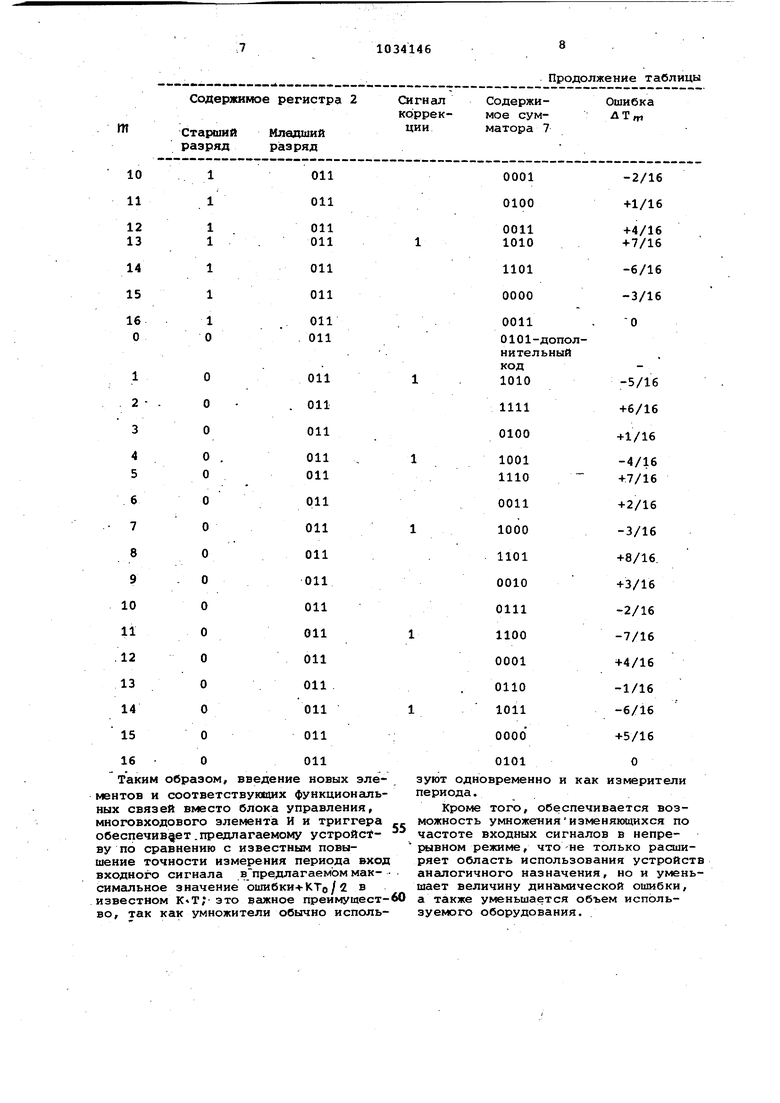

Следующий импульс с выхода формирователя 8 также осуществляет перезапись кодов из счетчиков 13 и 14 в регистры 2 и 3 соответственно. Таким образом, в регистре 2 хранится код ошибки измерения Tg с учето ее знака. Причем, если в старшем разряде {в ста1Ж1ем триггере) регистра 2 код 1, то ошибка измерения Т приведет к уменьшению кода, т.е. Tj( N TO ; если в старФаем разряде О, то N-TQ. Код модуля ошибки UN хранится в остальных разрядах (триггерах) регистра 2. Следует отметить, если в старшем разряде 3) , то код модуля ошибки, равен дополнительному коду числа, хранящегося в младших без одного старшего) триггерах ре-, гистра 2. В это же время в регистре 3 записан и хранится код N-1. Задержанный сигнал с выхода элемента 18 опять устанавливает в ис.ходное состояние счетчики 13 и 14, в сумматор 7 переписывается соответствующий код из регистра 2, а в счетчик 15 (через элемент 17) переписывает код N-1. Состояние регистров 2 и 3 не изменяется в течение времени Tgy , т.е. до прихода следующего импульса с формирователя8. Импульсы с генератора 1 с периодом следования Тд продолжают через элемент 16 поступат на йычитакяций вход счетчика 15 и суммирующий вход счетчика 13. При этом каждый импульс, поступивший на вычитающий вход счетчика, 15, уменьшает его содержимое на единицу. Следо вательно, через время ( N -1) f код счетчика 15 становится нулевым, а следуквдий импульс вызывает его отрицательное переполнение и на его Выходе возникает сигнал.{ импульс). Этот импульс, проходя через элемент 17, осуществляет запись в счетчик 1 кода ti -1. Г ; Как следует из изложенного, перио следования выходных импульсов Tg,y,x ,N.. ТрО-Тр /к, что и требовалось полу чить. Однако ошибка дТ uN места положения во времени) выходного импульса при этом может достигать по модулю величины Тд/2 (в прототипе TO) и должна была бы накапливаться, если бы не импульсы, формируемые на выходе сумматора 7. В сумматоре 7 осуществляется накопление сумкы вида i ЛТ , где 1- номер импульса с выхода счетчика 15, т.е. каждый импульс с выхода счетчика 15, поступая на управляющий вход сумматора 7 (.через элемент 17), осуществляет прибавление к содержимому сумматора 7 модуля величины ошибки измерения периода Тj(. Очевидно, что именнр наэту величину будет отличаться период выходных импульсов. Заметим, что при Тус7/ N-TO на информационные входы сумматора 7 поступает (через блоки 5 и 6 J прямой код ,(с единичных выходов триггеров) величины, хранящейся в регистре 2. Если же Т N-TO (т.е. в старшем разряде регистра 2 код 0, то на инфор мационные входы сумматора поступает обратный код (с нулевых выходов триг геров) величины, хранящейся в регист. ре 2. Одновременно на вход переноса сумматора 7 поступает сигнал, сосответствукиций единице младшего разряда сумматора. Так из обратного кода форкшруется дополнительный код. Еоли , то через некоторое время например, по приходу УМ-ГО импульса с выхода счетчика 15| в старшем разряде сумматора 7 появится 1. Это сигнализирует о том, что при формировании следующего УиЦ- 1)-го выходного импульса ошибка накопления ДТу превысит величину . Поэтому в момент появления 1 в старшем разряде сумматора 7 формирователь 9 формирует импульс коррекции, который поступает либо на суммирующий вход {через элемент 11), либо на вычитающий вход (через элементы 10 и 16) в зависимости От того, что хранится в старшем триггере регистра 2, или, что то же само,е, в зависимости от того, ошибка й,М уменьшила или увеличила код относительно значения Tgj(/Tp К. Импульс коррекции изменяет (уменьшает или увеличивает время) появления {w+l/-го выходного импульса на Т. Следовательно, сяиибка положения во времени l,W+l) -го выходного импульса изменит свой знак, но по модулю станет меньше величины Тр/2. В дальнейшем работа происходит аналогично описанному выше. Процесс формирования импульсов коррекции поясняется следующей таблицей, в которой рассмотрено два при мера: .л1« +011а 3/16 и AN -lOljj - , при этом взят четырехразрядный регистр 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ | 1979 |

|

SU826343A1 |

| Цифровой умножитель частоты | 1977 |

|

SU690609A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Умножитель частоты | 1978 |

|

SU765818A1 |

| Датчик углового положения,скорости и ускорения вращения вала | 1983 |

|

SU1101740A1 |

| Умножитель частоты | 1983 |

|

SU1151959A1 |

| Умножитель частоты | 1981 |

|

SU1058021A1 |

ЦИФРОВОЙ УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ, содержащий генератор опорной частоты, два счетчика импульсов, два регистра, первый формирователь импульсов, первый элемент ИЛИ, элемент Задержки, три элемента И и первый и второй блоки элементов и, выходы которых подключены к блоку элементов ИЛИ, выходы которого подключены к информационным входам сумматора., о т л и ч а гощ и и с я тем, что, с целью повышения точности умножения одновременном упрощении устройства, в него введены второй Лормирователь им: пульсов, третий счетчик импульсов и второй элемент ИЛИ, первый вход которого подключен к выходу первого элемента И, второй вход - к выходу генератора опорной частоты и суммируихцему входу первого счетчика импульсов, выходы которого подключены к информационным входам первого регистра, а импульсный выход к суммирующему входу второго счетчика импульсов, выходы которого подключены к информационным входам второго регистра, выходы которого соединены с информационными входами третьего счетчика импульсов, вычитающий вход которого соединен с выходом второго элемента ИЛИ, а суммирующий вход - с выходом второго элемента И, первый вход которого подключен к выходу второго формирователя импульсов .и первому входу первого элемента И, второй вход которого подключен к входу переноса, сумматора, нулевому выходу старшего раэряда первого регистра и управляющему ВХОДУ первого блока элементов И, информационные входы которого соединены с нулевыми выходами остальных разрядов первого регистра, единичные выходы которых подключеI ны к информационным входам второго блока элементов И, управляющий вход (/) которого подключен к второму входу второго элемента И и единичному выходу старшего разряда первого регистра, управляющий вход первого регистра соединен с управляющим входом второго регистра, первым управляющим входом сумматора, выходом первого формирователя импульсов, входом элемента задержки, выход которого подключен к установочным СО 4 входам первого и второго счетчиков импульсов и первому входу второго элемента ИЛИ, второй вход которого соединен с выходом третьего счетчика импульсов и первым входом третьего jSik элемента И, а выход - с управляю9: щим входом третьего счетчика и -:пульсов и вторым управляющим входом сумматора, выход которого подключен к входу второго формирователя имittyjibco t второй вход третьего элемента И подключен к шине блокировки, а выход является выходом устройства.

01Г

1

011

1 1 1 1 1 1 1 1 041 011 011 011 011 011 011 011

пряд

+3/16

+6/16

-7/16 -4/16

-1/16

+2/16 +5/16 -8/16 -5/16

15

Oil

16

Oil

Таким образом, введение новых элементов и соответствующих функциональных связей вместо блока управления, многовходового элемента И и триггера обеспечив ет.предлагаемому устройству по сравнению с известным повышение точности измерения периода вход входного сигнала в предлагаемЬм мак- симгшьное значение ошибки- -КТо/2 в известном К«т; это важное преимущест-60 во, так как умножители обычно испольПродолжение таблицы

+5/16

0000 0101

зуют одновременно и как измерители периода.

Кроме того, обеспечивается возможность умноженияизменяющихся по частоте входных сигналов в непрерывном режиме, что-не только расширяет область использования устройств аналогичного назначения, но и уменьшает величину динамической ошибки, а также уменьшается объем используемого оборудования.

Hrir Ili tin,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой умножитель частоты | 1976 |

|

SU663068A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-08-07—Публикация

1982-03-31—Подача