1

Изобретение относится к устройствам включения в заданную фазу в моделирующих установках.

Известное устройство, содержащее схему имитации короткого замыкания, подключенную к фазам моделирующей сети через коммутационные блоки, управляемые переключателем от блока задания фазы, командного блока и генератора импульсов через усилители мощности, не обладает достаточной точностью.

Предлагаемое устройство с целью повышения точности дополнительно снабжено командными переключателями, включенными между усилителями мощности и генератором импульсов, причем их управляющие входы подключены к переключателю через блок задержки включения и к командному блоку через блок задержки отключения.

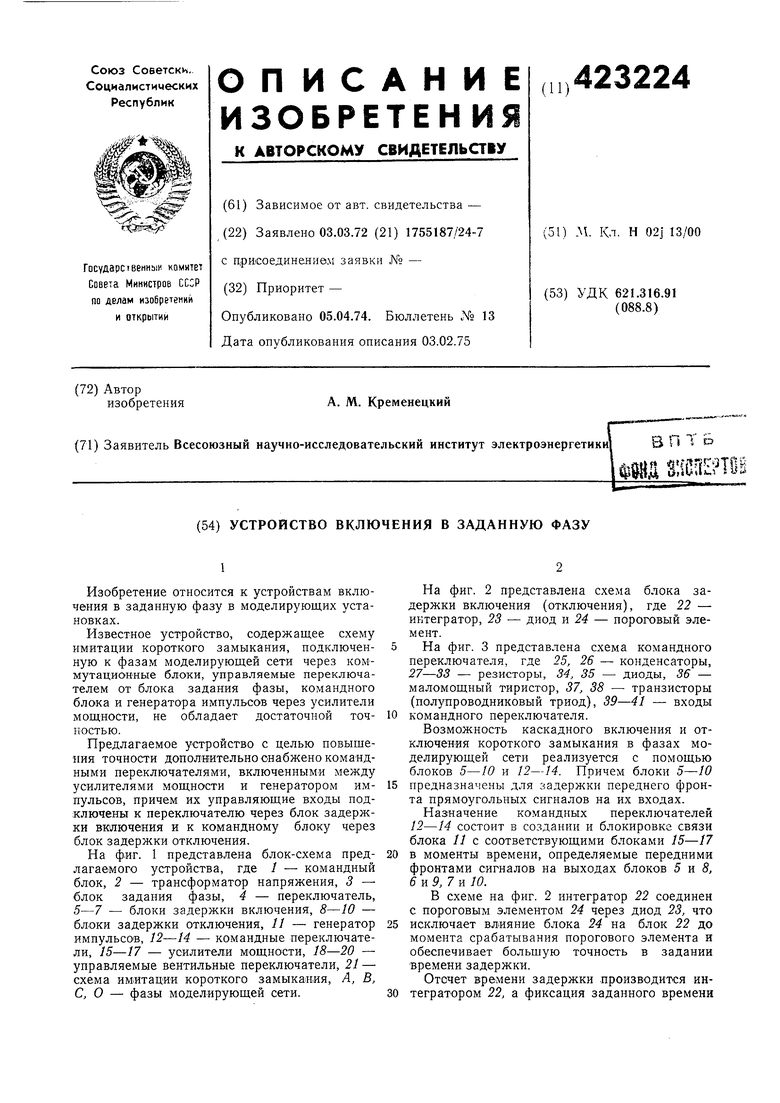

На фиг. 1 представлена блок-схема предлагаемого устройства, где / - командный блок, 2 - трансформатор напряжения, 5 - блок задания , 4 - переключатель, 5-7 - блоки задержки включения, 8-10 - блоки задержки отключения, 11 - генератор импульсов, 12-14 - командные переключатели, 15-17 - усилители мощности, 18-20 - управляемые вентильные переключатели, 21 - схема имитации короткого замыкания. А, В, С, О - фазы моделирующей сети.

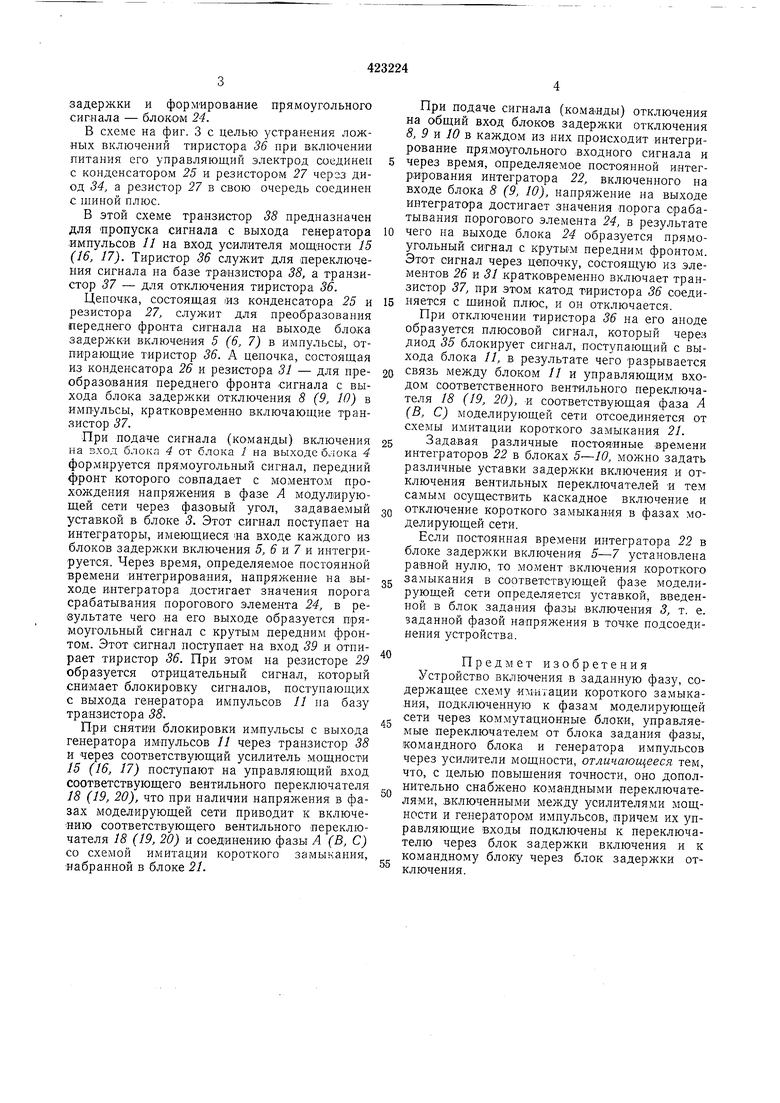

На фиг. 2 представлена схема блока задержки включения (отключения), где 22 - интегратор, 23 - диод т 24 - пороговый элемент.

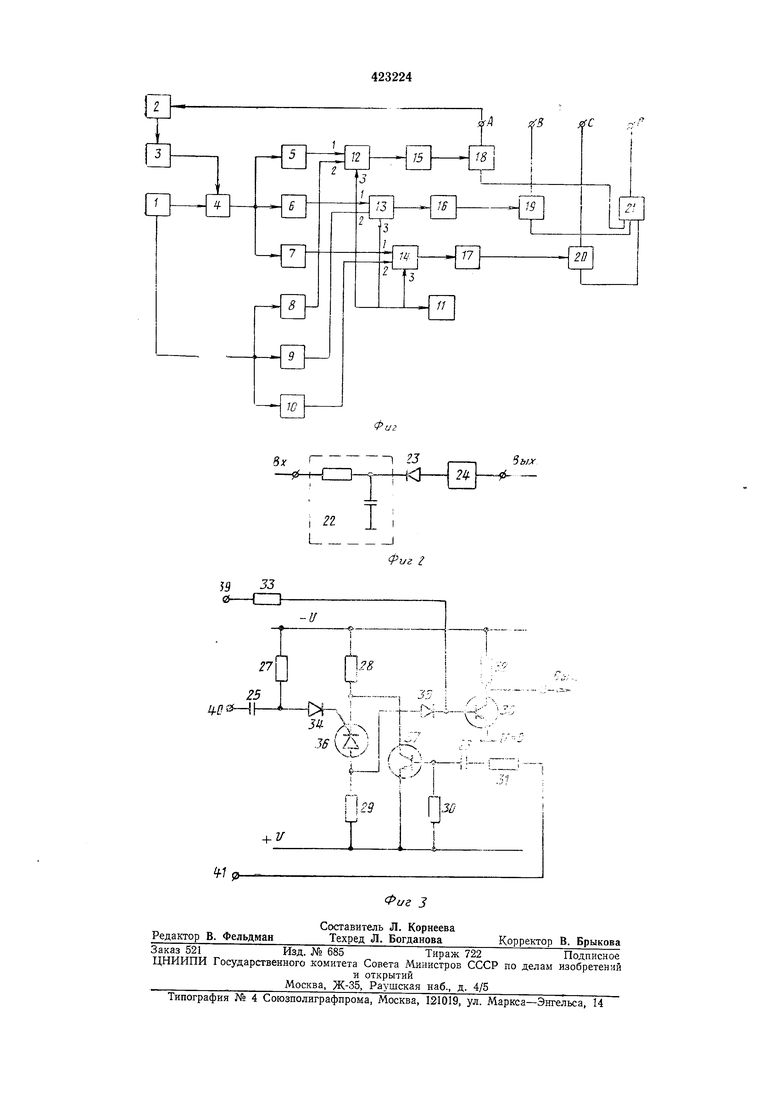

На фиг. 3 представлена схема командного переключателя, где 25, 26 - конденсаторы, 27-35 - резисторы, 34, 35 - диоды, 36 - маломощный тиристор, 37, 38 - транзисторы (полупроводниковый триод), 39-4} - входы

командного переключателя.

Возможность каскадного включения и отключения короткого замыкания в фазах моделирующей сети реализуется с помощью блоков 5-W и 12-14. Причем блоки 5-10

предназначены для задержки переднего фронта прямоугольных сигналов на их входах.

Назначение командных переключателей 12-14 состоит Б создании и блокировке связи блока 11 с соответствующими блоками 15-17

в моменты времени, определяемые передними фронтами сигналов на выходах блоков 5 и S, 6 к 9, 7 я 10.

В схеме на фиг. 2 интегратор 22 соединен с пороговым элементом 24 через диод 23, что

исключает влияние блока 24 на блок 22 до момента срабатывания порогового элемента и обеспечивает большую точность в задании времени задержки.

Отсчет времени задержки производится интегратором 22, а фиксация заданного времени

задержки и формирование прямоугольного сигнала - блоком 24.

В схеме на фиг. 3 с целью устранения ложных включений тиристора 36 при включении питания его управляющий электрод соединен с конденсатором 25 и резистором 27 черэз диод 34, а резистор 27 в свою очередь соединен с шиной плюс.

В этой схеме траизистор 38 предназначен для пропуска сигнала с выхода генератора импульсов 11 на вход усилителя мощности 15 (16, 17). Тиристор 36 служит для переключения сигнала на базе транзистора 38, а транзистор 37 - для отключения тиристора 36.

Цепочка, состоящая яз конденсатора 25 и резистора 27, служит для преобразования переднего фронта сигнала на выходе блока задержки включения 5 (6, 7) в импульсы, отпирающие тиристор 36. А цепочка, состоящая из конденсатора 26 и резистора 31 - для преобразо)вания переднего фронта сигнала с выхода блока задержки отключения 8 (9, 10) в импульсы, кратковременно включающие транзистор 37.

При подаче сигнала (команды) включения на вход блока 4 от блока / на выходе блока 4 формируется прямоугольный сигнал, передний фронт которого совпадает с моментом прохождения напряжения в фазе А модулирующей сети через фазовый угол, задаваемый уставкой в блоке 5. Этот сигнал поступает на интеграторы, имеющиеся «а входе кан :дого из блоков задержки включения 5, 6 и 7 и интегрируется. Через время, определяемое постоянной времени интегрир01вания, напряжение на выходе интегратора достигает значения порога срабатывания порогового элемента 24, в результате чего на его выходе образуется прямоугольный сигнал с крутым передним фронтом. Этот сигнал поступает на вход 39 и отпирает тиристор 36. При этом на резисторе 29 образуется отрицательный сигнал, который снимает блокировку сигналов, поступающих с выхода генератора импульсов 11 на базу транзистора 38.

При снятии блокировки импульсы с выхода генератора импульсов 11 через транзистор 38 и через соответствующий усилитель мощности 15 (16, 17) поступают на управляющий вход соответствующего вентильного переключателя 18 (19, 20), что при наличии напряжения в фазах моделирующей сети приводит к включению соответствующего вентильного переключателя 18 (19, 20) и соединению фазы Л (В, С) со схемой имитации короткого замыкапия, набранной в блоке 21.

При подаче сигнала (команды) отключения на общий вход блоков задержки отключения 8, 9 -я 10 в каждом из них происходит интегрирование прямоугольного входного сигнала и

через время, определяемое постоянной интегрирования интегратора 22, включенного на входе блока 8 (9, 10), напряжение на выходе интегратора достигает значения порога срабатывания порогового элемента 24, в результате

чего па выходе блока 24 образуется прямоугольный сигнал с крутым передним фронтом. Этот сигнал через цепочку, состоящую из элементов 26 и 31 кратковременно включает транзистор 37, при этом катод тиристора 36 соединяется с щиной плюс, и он отключается.

При отключении тиристора 36 на его аноде образуется плюсовой сигнал, который через диод 35 блокирует сигнал, поступающий с выхода блока //, в результате чего разрывается

связь между блоком 11 и управляющим входом соответственного вентильного переключателя 18 (19, 20), и соответствующая фаза А (В, С) моделирующей сети отсоединяется от схемы имитации короткого замыкания 21.

Задавая различные постоянные времени интеграторов 22 в блоках 5-10, можно задать различные уставки задержки включения и отключения вентильных переключателей -и тем са.мым осуществить каскадное включение и

отключение короткого замыкания в фазах моделирующей сети.

Если постоянная времепи интегратора 22 в блоке задержки включения 5-7 установлена равной нулю, то мо.мент включения короткого

замыкания в соответствующей фазе моделирующей сети определяется уставкой, введенной в блок задания фазы включения 3, т. е. заданной фазой напряжения в точке подсоединения устройства.

Предмет изобретения

Устройство включения в заданную фазу, содержащее схему иммтации короткого замыкания, подключенную к фазам моделирующей сети через коммутационные блоки, управляемые переключателем от блока задания фазы, командного блока и генератора импульсов через усилители мощности, отличающееся тем, что, с целью повыщения точности, оно дополнительно снабжено командными переключателями, включенными между усилителями мощности и генератором импульсов, причем их управляющие входы подключены к переключателю через блок задержки включения и к командному блоку через блок задержки отключения.

J5 33

0-CZIh

-If

-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления компенсированным выпрямительно-инверторным преобразователем электроподвижного состава | 1987 |

|

SU1468791A1 |

| Устройство для автоматического регулирования напряжения на электрофильтре | 1976 |

|

SU752274A1 |

| Устройство для контроля исправности силовых тиристоров вентильного преобразователя | 1989 |

|

SU1758760A1 |

| Устройство для оптимизации фотосинтеза растений | 1989 |

|

SU1690611A1 |

| Устройство для моделирования электромагнитных процессов в асинхронных машинах | 1988 |

|

SU1594569A1 |

| Широтно-импульсный регулятор для управления вентильным преобразователем | 1983 |

|

SU1181074A1 |

| Устройство управления дуговой сваркой | 1987 |

|

SU1505705A1 |

| УСТРОЙСТВО ФАЗОВОГО УПРАВЛЕНИЯ | 1971 |

|

SU310467A1 |

| Вентильный электродвигатель | 1984 |

|

SU1257770A1 |

| Устройство для защиты от повреждений электрической сети | 1984 |

|

SU1275624A1 |

25

-N

3B(:h

Vu

i--1x1- -., ,

Авторы

Даты

1974-04-05—Публикация

1972-03-03—Подача