1

Данный логический элемент предназначен для использования в быстродействуюпдих устройствах дискретной автоматики, вычислительной и измерительной техники, в частности при построении высокоскоростных реверсивных счетных и сдвиговых устройств.

Известны логические элементы «Запрет, содержащие иереключатель тока на транзисторе, база которого соединена с шиной потенциального сигнала, обращенный диод и накопительный диод, соединенный с шиной импульсного сигнала.

Предложенное устройство отличается от известных тем, что в него введены усилительдискриминатор на дополнительном транзисторе с туннельным диодом в эмиттере и транзистор обратной связи, у которого база подключена к эмиттеру дополнительного транзистора, а коллектор - к точке соединения накопительного диода, базы дополнительного транзистора и коллектора транзистора переключателя тока, эмиттер которого соединен через резистор с щиной питания и через обращенный диод, включенный в обратном направлении,- с общей шиной.

Эти отличия позволяют повысить быстродействие и надежность элемента.

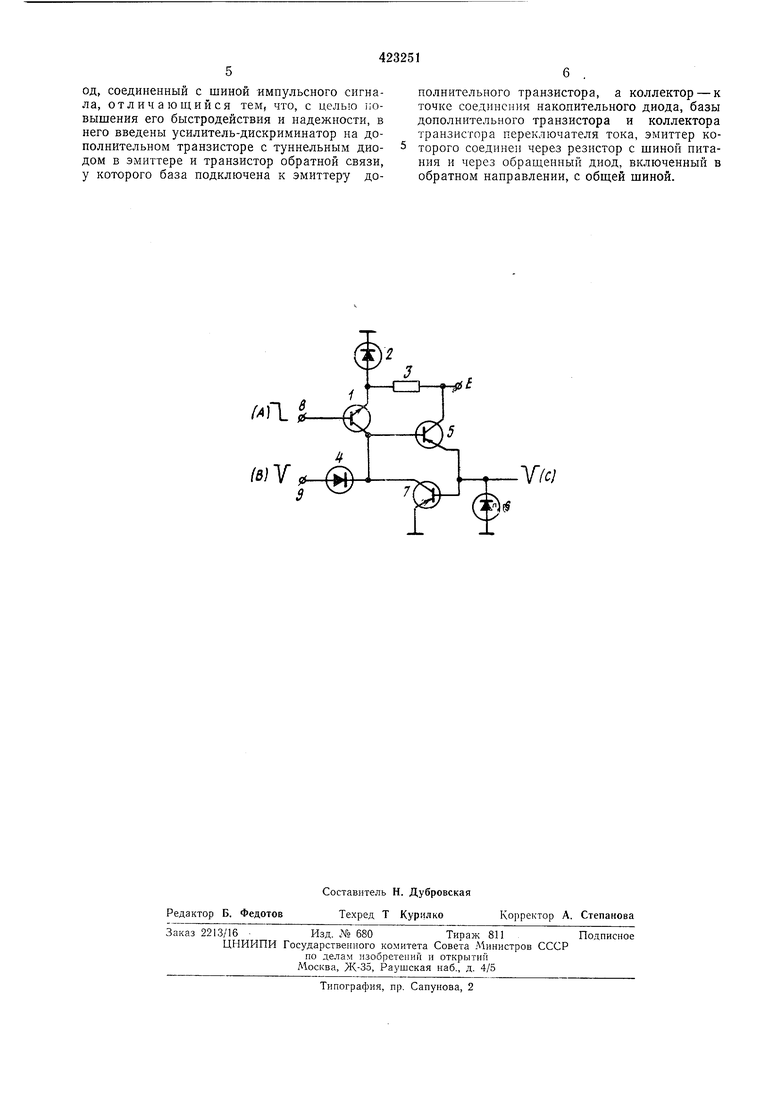

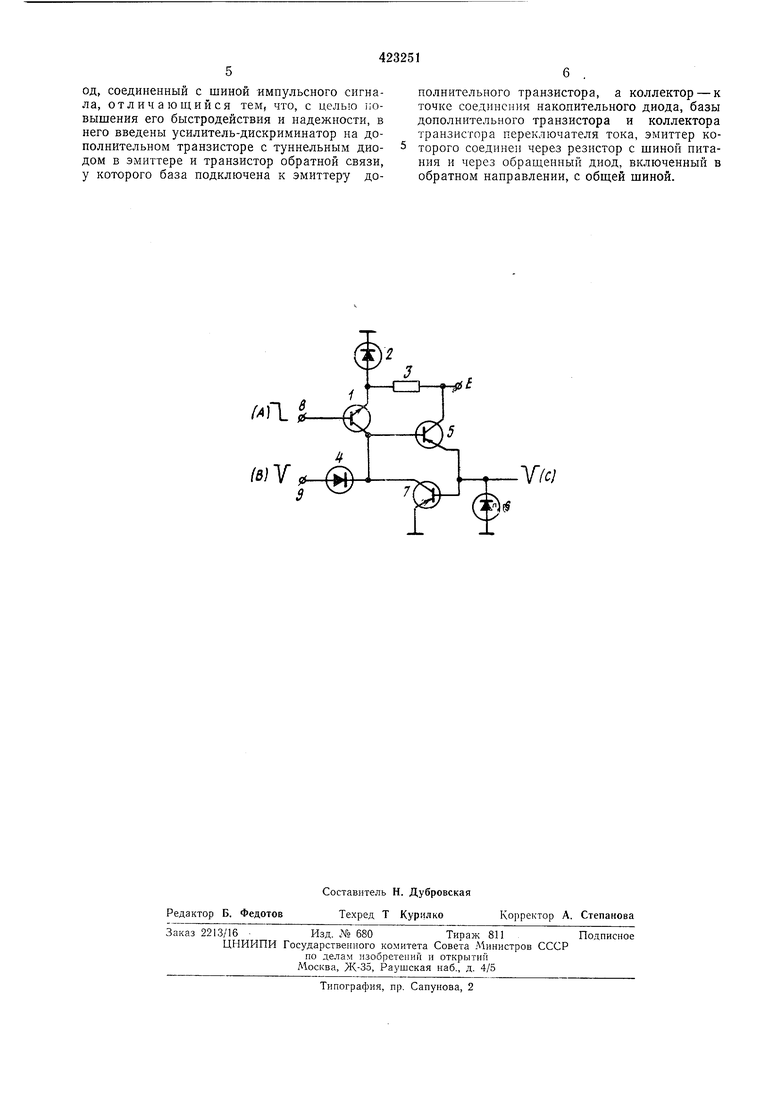

Приведенная на чертеже принципиальная схема логического элемента «Запрет предусматривает работу с отрицательными сигналами, однако при изменении полярности включения диодов и источника смещения, тинов проводимости транзисторов она быть использована в системах положительной логики.

Логический элемент «Запрет содерлшт быстродействующий переключатель тока на транзисторе 1, обращенный диод 2, резистор 3, накопительный диод 4, усилитель-дискриминатор на дополнительном транзисторе 5 и туннельном диоде 6, транзистор обратной связи 7. Управляется элемент по входным шинам 8 от источников напряжения с малым внутренним сопротивлением, причем уровню логического нуля соответствует нулевое напряжение входных сигналов, а уровню логическо единицы соответствует иекоторый отрицательный уровень напряжения.

При отсутствии на шине 8 запрещенного

потенциального сигнала отрицательной полярности (нулевое наиряжение) через резистор 3, транзистор 1 и накопительный диод 4 протекает ток от источника постоянного смещения Е. Базовым током транзистора 1 при достаточно бoльшo его коэффициенте усиления по току можно пренебречь. Вольт-амперную характеристику нрямой ветви обращенного диода 2 выбирают такой, чтобы ток, протекающий через этот диод при отсутствии запрещающего сигнала на шине 8, был пренебрежими мал по сравнению с током через траизиетор 1.

Падением напряжения на наконительпом диоде -i дополнительный транзистор о усилителя-дискриминатора смещается в активную ооласть раОоты, и его эмиттерный ток протекает через туннельный диод Ь. Ьазовым током транзистора о нры досгагочно оольшом его коэффициенте усиления по току можно пренеоречь.

Б результате протекания эмиттерного тола транзистора 5 через диод 6 норог срабатывания усилителя-дискриминатора снижается, т. е. создаются благоприятные условия для его срабатывания с весьма малой задержкой. Изменяя сопротивление резистора о и вольтамперную характеристику наконительного диода 4, можно варьировать величину порога усилителя-дискриминатора в широких пределах. Вместе с тем при заданной вольт-амперной характеристике диода 4, благодаря его стабилизирующим и термокомпенсирующим свойствам, обеспечивается неизменность выбранной величины порога срабатывапия усилителя-дискриминатора при значительных разбросах сопротивления резистора 3, значительных изменениях напряжения смещения Е и температуры.

Так как рабочая точка диода 6 находится на туннельной ветви его вольт-амперной характеристики, то напряжение на нем пренебрежимо мало, и транзистор обратной связи 7 закрыт.

Имеющийся на входной шине 9 отрицательный импульс запирает накопительный диод 4 и переключает ток в базу дополнительного транзистора 5, вызывая срабатывание туннельного диода 6 усилителя-дискриминатора. Благодаря рассасыванию заряда, пакоплепного за время протекания через диод 4 прямого тока, и уменьшенному порогу срабатывания усилителя-дискриминатора происходит ускоренное переключение диода 6 эмиттерным током транзистора 5. Вследствие этого выходной импульс на диоде 6 задерживается относительно импульса на входной шине 9 на доли наносекунды.

Величина накопленного заряда экспоненциально зависит от длительности протекания прямого тока и существенна при длительностях 3--5 нсек, что соответствует частоте работы логического элемента 300-200 Мгц.

За счет индуктивного характера изменения выходного сопротивления дополнительного транзистора 5 и благодаря наличию участка отрицательного сопротивления вольт-амперной характеристики туннельного диода 6 выходной импульс усиливается по напряжению. Нагрузочная способность логического элемента «Запрет, определяемая усилением по мощности транзистора 5, работающего в режиме эмиттерного повторителя, достаточно велика.

Запираемый накопительный диод 4 в цепи импульсного сигнала обеспечивает очень широкий диапазон изменения амплитуды импульсного сигнала, что новышает надежность устройства.

Выходной импульс на туннельном диоде 6 включает транзистор обратной связи 7, который с небольшой задержкой шунтирует накопительпый диод 4, вызывая ускоренное рассасывание заряда, наконленного в базе этого диода. Это дает возможность новысить частоту повторения имнульсного сигнала на шине 9

и, следовательно, повысить быстродействие. В результате шунтирования базы дополнительного транзистора 5 выходной импульс формируется по длительности. Кроме того, отрицательная обратная связь по напряжению

стабилизирует работу этого транзистора в переходном режиме.

Формирующие и усилительные свойства логического элемента «Запрет позволяют разбить его на практически неограниченное число

каскадов.

Легко видеть, таким образом, что при нулевом напряжении на шине 8 импульсный сигнал на шине 9 не занрещ ается, т. е. справедливо логическое соотношение для входных и

выходных сигналов .

При наличии на шине 8 потенциального запрещающего сигнала отрицательной полярности (единичный уровень напряжения) через резистор 3 и обращенный диод 2 протекает

ток. Остальные компоненты схемы обесточены. Амплитуда запрещающего сигнала может изменяться в очень широких пределах, причем от источника этого сигнала потребляется очень небольшая энергия, так как он запирает транзистор 1 переключателя тока и переключает ток транзистора 1 в цепь обращенного хг.иода 2. Наличие в цени переключения тока, задаваемого резистором 3, обращенного диода 2 позволяет повысить частоту смены

уровней потенциального запрещ ающего сигнала на шине 8. Кроме того, стибилизирующие свойства обращенного диода 2 обеспечивают некритичность к разбросам номинального сопротивления резистора 3, изменениям напряжения смещения и амплитуды потенциального сигнала на шине 8.

Поскольку при наличии на шине 8 запрещенного потенциального сигнала все компоненты схемы за исключением резистора 3 и

обращенного диода 2 обесточены, воздействие импульса па шине 9 не вызывает срабатывания неподготовленного усилителя-дискриминатора, порог срабатывания которого в данном случае велик и помеха за счет барьерной емкости накопительного диода 4 легко им дискриминируется. Очевидно, что и в этом случае для входных и выходных сигналов справедливо логическое соотношение .

П ip € д м е т и 3 о б р € т е и и я

Логический элемент «Запрет, содержащий переключательтока на транзисторе, база которого соединена с шиной потенциального сиг65 нала, обращенный диод и накопительный диод, соединенный с шиной импульсного сигнала, отличающийся тем, что, с целью повышения его быстродействия и надежности, в него введены усилитель-дискриминатор на дополнительном транзисторе с туннельным диодом в эмиттере и транзистор обратной связи, у которого база подключена к эмиттеру дополнительного транзистора, а коллектор - к точке соединения накопительного диода, базы дополнительного транзистора и коллектора транзистора переключателя тока, эмиттер которого соединен через резистор с шиной питания и через обращенный диод, включенный в обратном направлении, с общей шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1973 |

|

SU389548A1 |

| ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1970 |

|

SU269201A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «НЕ-ИЛИ» | 1971 |

|

SU305588A1 |

| ОДНОТАКТИЫЙ РЕГИСТР СДВИГА | 1971 |

|

SU291246A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "ИЛИ - НЕ" НА ТУННЕЛЬНЫХ ДИОДАХ | 1967 |

|

SU224579A1 |

| Пороговое устройство | 1975 |

|

SU790242A1 |

| АВТОМАТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ПОЭЛЕМЕНТНОГО КОНТРОЛЯ АККУМУЛЯТОРНОЙ БАТАРЕИ | 1971 |

|

SU319977A1 |

| Токовый источник питания | 1976 |

|

SU728202A1 |

| Электрометрический преобразователь заряда | 1986 |

|

SU1448292A1 |

| ДЕТЕКТОР ПРИРАЩЕНИЙ | 1971 |

|

SU296220A1 |

Авторы

Даты

1974-04-05—Публикация

1972-02-04—Подача