Устройство относится к области дискретной автоматики и вычислительной техники.

Быстродействуюи1ие логические элементы «НЕ-ИЛИ, содержащие входные диодные сборки, транзисторы, бистабильные ячейки на туннельных диодах и резисторах, обращенные и накопительные диоды, известны. Однако они мало чувствительны и относительно сложны из-за необходимости иметь два или более источника постоянного смещеНИН разной нолярности. В предлагаемом логическом элементе «НЕ-ИЛИ, с целью повышения чувствительности, быстродействия и упрощения схемы, база транзистора соединена с выходом бистабильной ячейкн, эм ггтер иодключен к точке соединения токозадающего резистора и обращенного диода, коллектор транзистора соединен с донолнительным туннельным диодом и диодом с накоплением заряда, а резистор бистабильной ячейки подключен к точке соединення эмиттера транзистора, обращенного диода и токозадающего резистора.

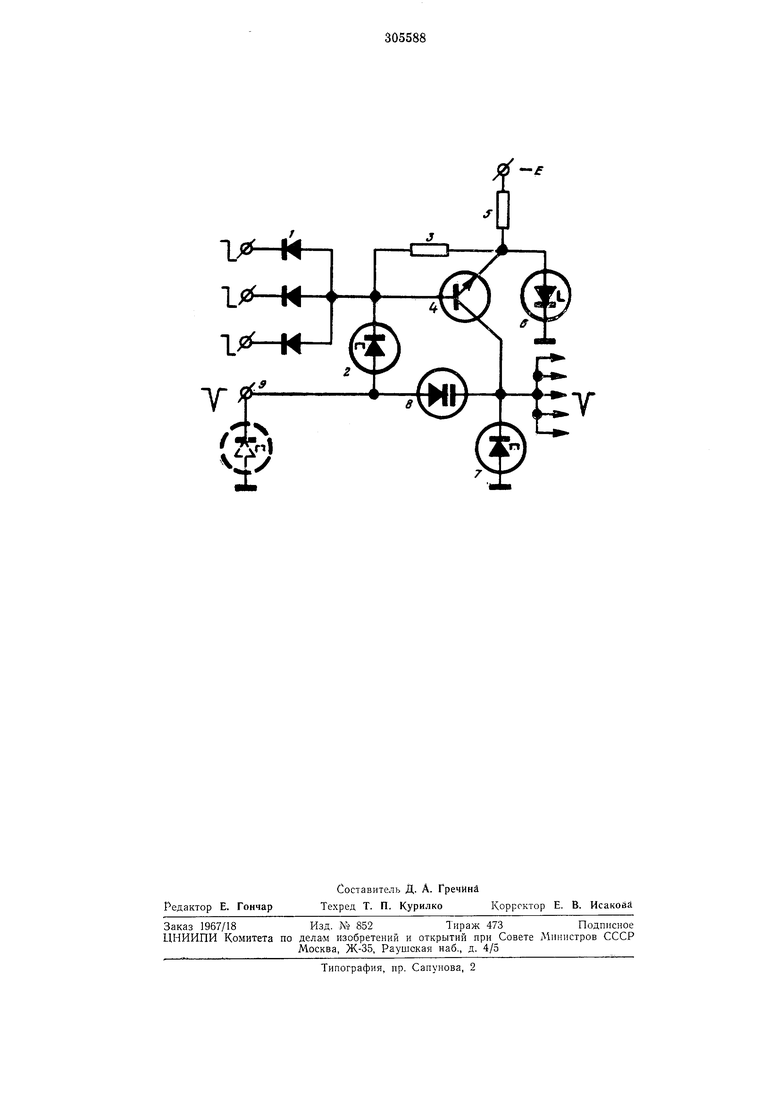

На чертеже приведена принципиальная схема элемента.

Схема логического элемента содержит входную диодную сборку 1, бистабильную ячейку иа туннельном диоде 2 и резисторе 3, транзистор 4, база которого соединена с выходом бистабильной ячейки, эмиттер иодключей в точку соединения токозадающего резистора 5 и обращенного диода 6, включенного в непроводящем нанравленни для источника смещения Е. В коллекторную цеиь транзистора включены в прямом направлении туннельный диод 7 и диод с накоплением заряда 8, иодключенный к источнику запирающих импульсов 9.

При отсутствии отрицательных сигналов на входах диодной сборки / туннельный диод 2 находится в низковольтном состоянии, через резисторы 3, 5 и транзистор 4 протекает ток. Через обращенный диод 6, включенный в направлении занирания для источника смещения Е, также протекает небольшой ток. Вольтамперная характеристика обращенного диода 6 выбирается таким образом, чтобы напряжение отпираиия обратной ветви ее было приблизительно равно сумме падения напряжения на эмиттернобазовом переходе транзистора и падения иапряжения на иереходе накоиительного диода 8.

Резистор 3 определяет двустабильиый режим работы туннельного диода 2.

Через выходной туннельный диод 7 и иаконительный диод 8 нротекает коллекторньи ток транзистора. Базовым током транзистора при досгаточно высоком коэфф1Н1иенте усиления по току молсно пренебречь. Поскольку туннельный днод 7 зашутирован накопительным диодом 8, а источник импульсов имеет малое внутреннее сопротивление, ианряжение на, выходе равно падению напряжения на переходе накопительного диода 8. Вольтамперная характеристика перехода накопительного диода выбирается такой, чтобы напряжение на выходе было бы несколько больше никового нанряжения туннельного диода 7.

Небольшой отрицательный потенциал на выходе схемы может быть использован для нодготовки, с целью увеличения быстродействия, различного рода усилителей и ряда других устройств.

Величина тока бистабильной схемы (резистор, диод 2) также стабилизируется за счет большой крутизны эмнттерно-базового перехода транзистора и характеристики обращенного диода. Благодаря этим факторам достигается неизменная чувствительность, и следовательно, надежная работа бистабильной схемы.

Нанряжение отнирания коллекторно-базового перехода транзистора всегда больше, чем падение нанряжения на накопительном диоде. Поэто.му режимы насыщения его исключаются, что обусловливает высокое быстродействие.

При.ходящнй по входу 9 отрицательный имнульс воздействует на базу транзистора, запирая его, и на наконительный диод, рассасывая накопленный в его базе заряд. Так как туннельный диод уже был выведен за область пика вольт-амперной характеристнки, а сопротивление наконительного диода нренебрежимо мало в момент рассасывания наконнтельного заряда, то задержка срабатывания выходного туннельного диода 7 является в нринцине минимально возможной для гибридных схе.м на туннельных диодах и диодах с накоплением заряда.

Транзистор в схеме фактически работает как запираемый эмнттерный новторитель, переключающий ток через обращенный диод. Применение обращенного диода ускоряет нроцесс нереключения тока. Запирание транзистора сопровождается уменьшением тока, нротекающего через наконительный днод и туннельный диод 7. Вследствие того, что инерционность транзистора несколько больше, чем задержка срабатывания туннельного диода 7, а крутизна снада коллекторного 1ока практически новторяет крутизну нереднего фронта нмнульсного сигна.та, то имеет место формирование спада отргщательного выходного нмнульса.

При воздействии отрицательного сигнала но одному из входов сборки или но всем ее входам туннельный диод 2 опрокидывается в высоковольтное состояние и запирает транзистор. Еслн нри этом одновременно воздействует и импульсиый сигнал но входу 9, то происходит срабатывание ту1Н1ельного диода 7 и затем работа схемы аналогична уже ранее описанной. Если имнульсный сигнал по входу 9 отсутствует, то срабатывания туннельного диода 7 не нроисходит, так как он защунтирован диодом 8. Транзистор заннрается, причем переключается ток его через обращенный диод 6. Ток коллекторной

цепи при этом становится меньше иикового тока туннельного диода 7. Накопительный диод 8 обесточивается и накопленный в нем заряд быстро стекает через очень малое соиротивление туннельной ветви диода 7.

Если тенерь, нри высоковольтном состоянии туннельного диода 2, приходит отрицательный имнульс на вход 9, то через диод 8 нроходит лишь помеха за счет его проходной емкости. Эта помеха легко дискриминнруется туннельным диодом 7, поскольку в

момент действия импульса ток, протекающий

через туннельный диод, значительно меньше

пикового.

Одновременно имнульс по входу 9 сбрасывает туннельный диод 2 в низковольтное состояние. Так как напряжение бистабильной схемы строго фиксировано, благодаря стабилизации нотенциала в точке нодключения эмиттера транзистора 4, обращенного диода 6 и токозадающего резистора 5, то сброс диода 2 надежно обеспечивается в широком дианазоне изменения амплитуд импульсов и величины нанряжения Е, нревышающем диапазон известных схем.

Время жизни неосновных носителей диодов сборки в нредлагаемом логическом элементе не играет существенной роли, так как время протекания нрямого тока через них определяется временем включения бистабильной

схемы, которое очень мало.

В отличие от большинства известных, нредлагаемый логический элеме1гг может работать как с нотенциальными, так и с импульсными сигналами но входам сборки.

Предмет изобретения

Быстродействующий логический элемент «НЕ-НЛН, содержащий входную диодную сборку, транзистор, бистабильпую ячейку на

туннельном диоде и резисторе, обращенный и наконительный диоды, отличающийся тем, что, с целью новышения чувствительности, быстродействия и унрощения схемы, база транзистора соединена с выходом бистабильной ячейки, эмиттер подключен к точке соедннення токозадающего резистора и обращенного диода, коллектор транзистора соединен с донолнительным туннельным диодом и диодом с накоплением заряда, а резистор бистабильной ячейки подключен к точке соединения эмиттера транзистора, обращенного диода и токозадающего резистора.

-

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСЕСОЮЗНАЯ ПЛТгеТ1Ш-ТГШ:^;Е;л?= | 1973 |

|

SU363194A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1973 |

|

SU389548A1 |

| РЕЛАКСАЦИОННЫЙ ГЕНЕРАТОР | 1970 |

|

SU273268A1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1973 |

|

SU374656A1 |

| УСТРОЙСТВО для ИМПУЛЬСНОЙ ЗАРЯДКИ | 1973 |

|

SU399617A1 |

| ФАЗОИМПУЛЬСНЫЙ МНОГОУСТОЙЧИВЫЙ ЭЛЕМЕНТ | 1970 |

|

SU273272A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «ЗАПРЕТ» | 1972 |

|

SU423251A1 |

| ПАТ?Ш'Ш-[1ХСГ'Е^:чДП | 1973 |

|

SU362487A1 |

| СЧЕТЧИК ЭНЕРГИИ ПОСТОЯННОГО ТОКАВСЕСОЮЗНАЯПАТЕНТНО-][ХНГ:^"КАЯБИБЛИОТЕКА | 1970 |

|

SU283394A1 |

| Логическая схема "или-и-не" | 1974 |

|

SU510784A1 |

Даты

1971-01-01—Публикация