Изобретение отпооится к области iiisoGipaтельных устройст в Н может быть дсиользова о в системах MaiccoBoro обслугЖйва.ния, в частности в а1вт0)мати1ческ;их телег раф/ных системах.

Известен распределитель вызовов, соде1р кащий блок подключения .распределителя, цеии преиьмущества и блОК ущ авл&нкя.

Однако (на выходах (распределителя ори Определеено/м сдвиге ,мо1Мвнтов лОЯвленмя (вызавсв 1на разных вхюдал ли(бо при олределе HQiM соот«0ше1нии Бремен«ых оар а метров входяи1,1И|Х в иего элементо в воз можио Появлаиме , что -npiHiBecT к «аправильн-ой работ-е авязаййых .с распределителем устройств.

С целью уменьшенйя помех 1на выходах распределителя и сокращение Времеии поиска вызьрвающего .входа в npyinine аднсшременио вызывающих вх0(дов в :првдла гаемо1М раадредел-ителе группы .И1нфор.ма1ци. и установочных выхходогв подмлючонн-я распределителя, закреплешные за каждой из коюрдиимт, подсоедИ|нены соответ етввндо к и/нформ-ац-иоиным .и уста1нав0141ньгм .входа1М доподнитешыио введенных блоков приема иифоримации первой и второй КООрдипат, «Нулевые выходы которых сосд|;,нены с соотпетстпующИ|МИ «лулевым п вмодамл цепей преимущества, «единичные в.ходы каждой из которых параллельно подключены к «едшнИчнЫМ выхода1М связанпого с дащной цепью лреи1м,ущестгва блока приСима, а к соответстэующей груапе информацпоиных входов блока управления и к первой группе информационных входов блока подключения распределителя, при этом цепи преимущества первой координаты соединены со второй группой информационных входов блока подключения, а выходы цепи преимущества второй координаты параллельно подключены к третьей грунпе ииформациостных входов блока .подключения и к Т1ретьей группе И1нфор1ма1Цио1Н:ных входов блока уюравления, защрещающий выход котор01-о соединен с запрещающим входом блока подключения распределителя, а каждый из двух разрешаюи11их выходов блока управления соединил с ра13рещающИ1М входом соответствующей цап.ц преИ|М|ущест1ва, . каждый из двух устанавочных 111 учрайляющ.их выходов Соёдимен с установочными и управляющими входами соответствующего блока приема; управляющие выходы блочка упра/влаиИЯ подключены к блоку подключения распределителя, куда TaiKKe подсоединены раэрешаюии1е выходы бло-ка х .праелен вя.

KpoiMe того, блок управлевия содарлуит дза .пороговых каскада, две пары выходных схем совпадения и узел формирования выходных еи(пнало)в, соединешные между собой такйам обр азо1М, что входы обои.х пороговых каскадо:в образуют первую и вторую прупны и.нфор мацискнных входов блока травления, шрямой и инверсный выходы каждого из пороговых «аакаД01В /связанны с первым БХОДОМ соответствующей выходной схемы совщаданвя, вторые вх-оды .юа Ж1Дой пары выхад1ных схем совпадения запараллелены и являются первым и вторым уиравляемыимл (входа1ми уиравлввия, выходы этих naip oi6ipa 3iyroT первые и вторые уцравляющяе выходы бло,к-а торавлваия; иулевой выход второго порогового каскада через выхадедую схему совпаде/ниЯ, связаииую с разрешающий выходам, соединен с первым входом узла фо1р1ми|роваиия выходных о№гиал|ОВ, первый выход кошорого является третьим управляющим выходом блока управления, BTi рой выход является аторым уста|НовоН1НЫ|М выходо1м блока уп1ра1Вле1НИ1Я, а также подключен к запрещающему входу схемы совпадения, другой вход которой овязам с пе1рвы м управляющим входом .блока у1П1равл ани Я, а выход схемы совпаяения является заирещающим выходом блока управлания и подключен к информац1ИО1Н1Н(01му входу схе1мы совпадеи-ия, выход которой является первым установочным выходом блока вдп|равле1Н1ия, а заирещаюЩИЙ вход которой через схему совпадения связан с ннве|р(с1ньш выходом napBoiro порогового каскада и с прямым выходом второго порогового каскада, при этом второй вход узла формирования выходных сигналов соединен с выходом схемы аоби1ра(НИ1Я, входы которой являются третьей грушпой ин1фор1мащиояных входов блока управления.

Цепи иреиакущества нарвой н второй координат выполнены в виде последовательного совпадения «г (,,2...) пар двухйходовых схем совпадения (из выходной и управляющей cxeiivi совладеНИй), имеющих общими вход, сзязайный с выходом /п редыдущей у.пр.а1вляющей cxeiMbi сови-адания, три этом .упраЕвляемый вход первой по порядку лары схем совпаде)НИй являет бя управляемым входом цепи 1преи1М;ущестгза, другие 1ВХ01ды всех п-выходных схем совпадений являются «единичными входами цепи Преимущества, а другие входы всех /г-1 уПравляющих схем совпадений являются «нулевыми входами цепи преимущества, а выходы всех выходных схем совпадений образуют выходы цепи преимущества.

Кал 1дый из блоков щрИема информации соСточит из пi (,2; п.,2,...) запоминающих ячеек 1И общей для -всех ячеек «-«Зходовой схемы юов падения, ярчетем И1нфо|рмац|Шнные входы входных и установочные входы установочных даухвходовых схем совпадении всех /г за|поминающих ячеек образуют соотйет отв.е1нйо -информавдиоиные -И усгганово-чные входы блока нрибма йнформадни, «едини 41ные и -януле1вые выходы йсех п-запоминающих ячеек образуют ооот1вет ствеено «единичные и «нулевые выходы блока приема инфор1мацйи, нрн этом «Н1уле1вые выходы параллелыно зашеданы таиасе на пчвх одовую схейу совеадемия, выход которой иараллелыно 1под1соедине1н к .инвертору и к другим входа м всех я-входных схем совии

дан-ий, а другие входы у1ста1ново1чных схвм оэВ1падвн.нй заю араллелены и образуют управляемый вход блока приема информации.

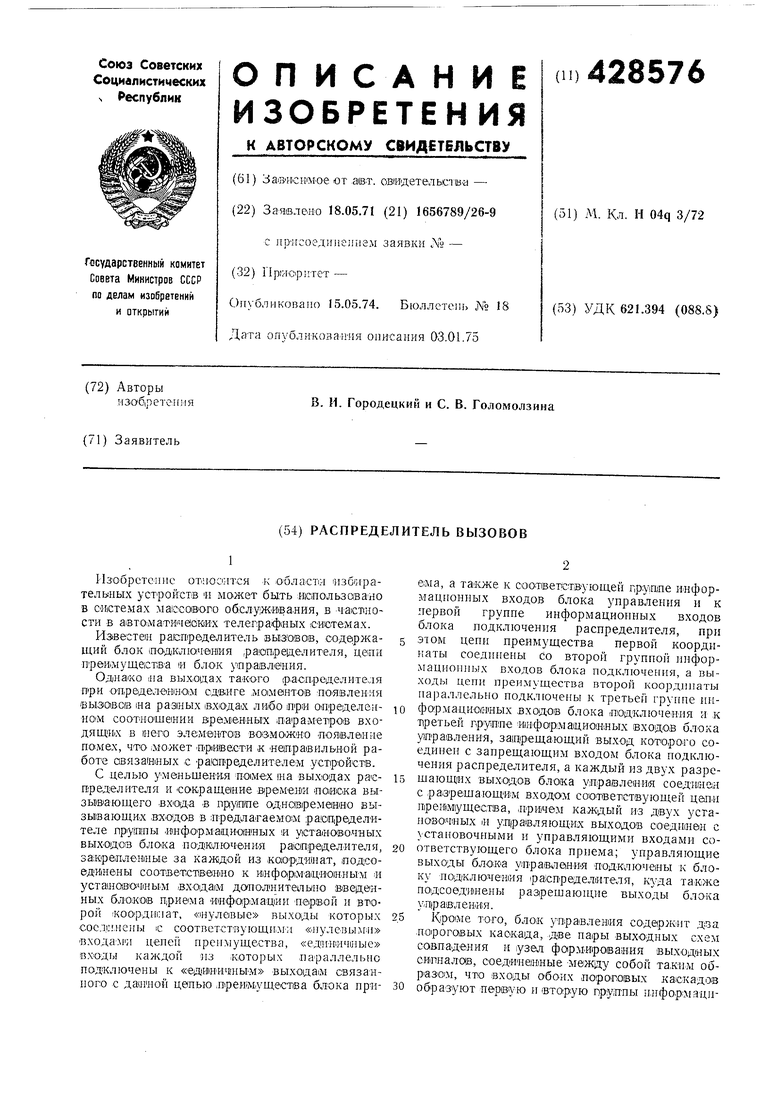

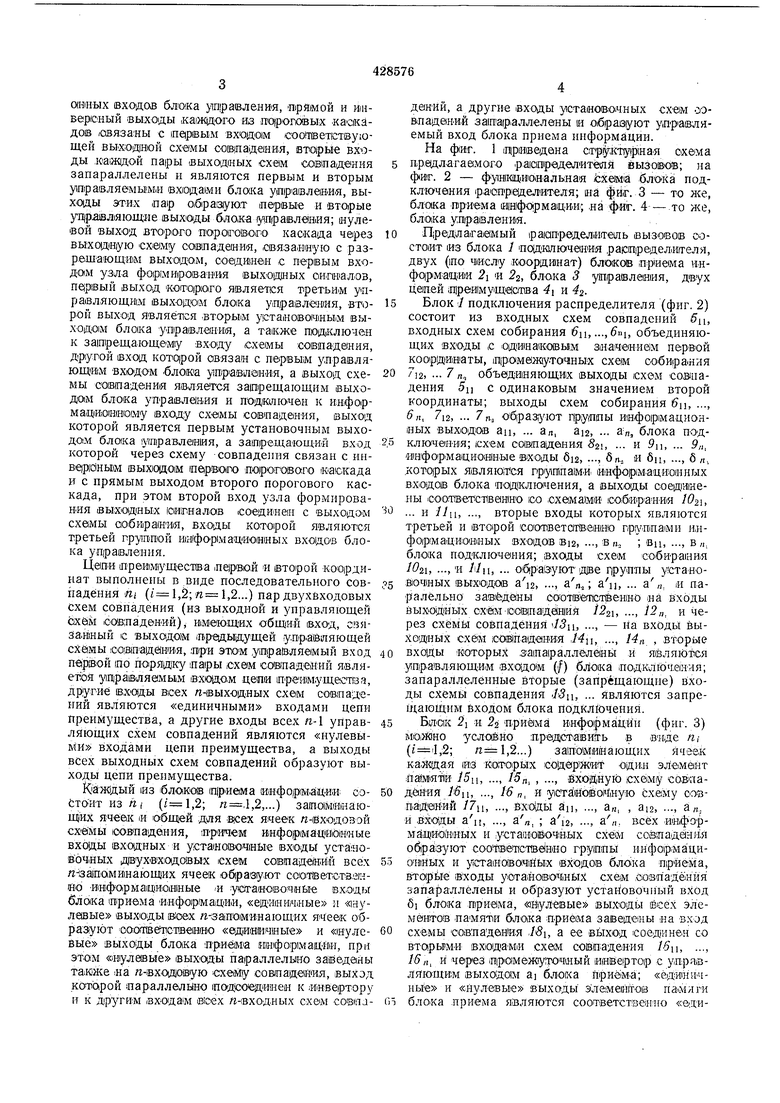

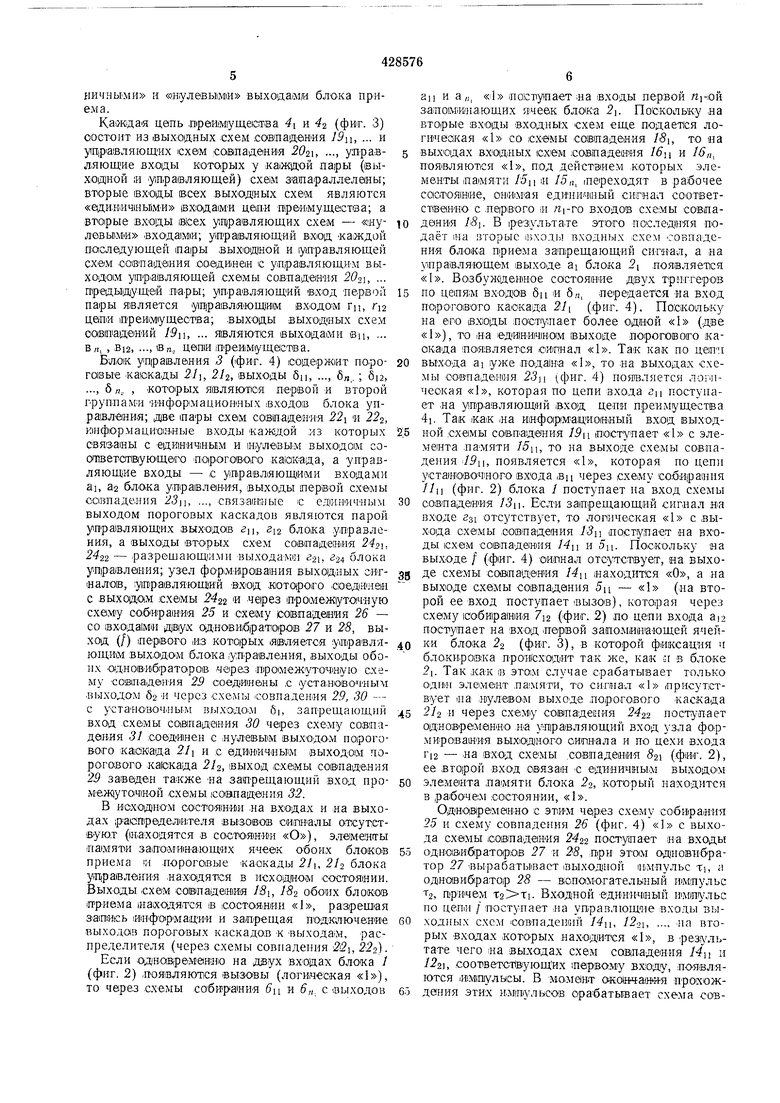

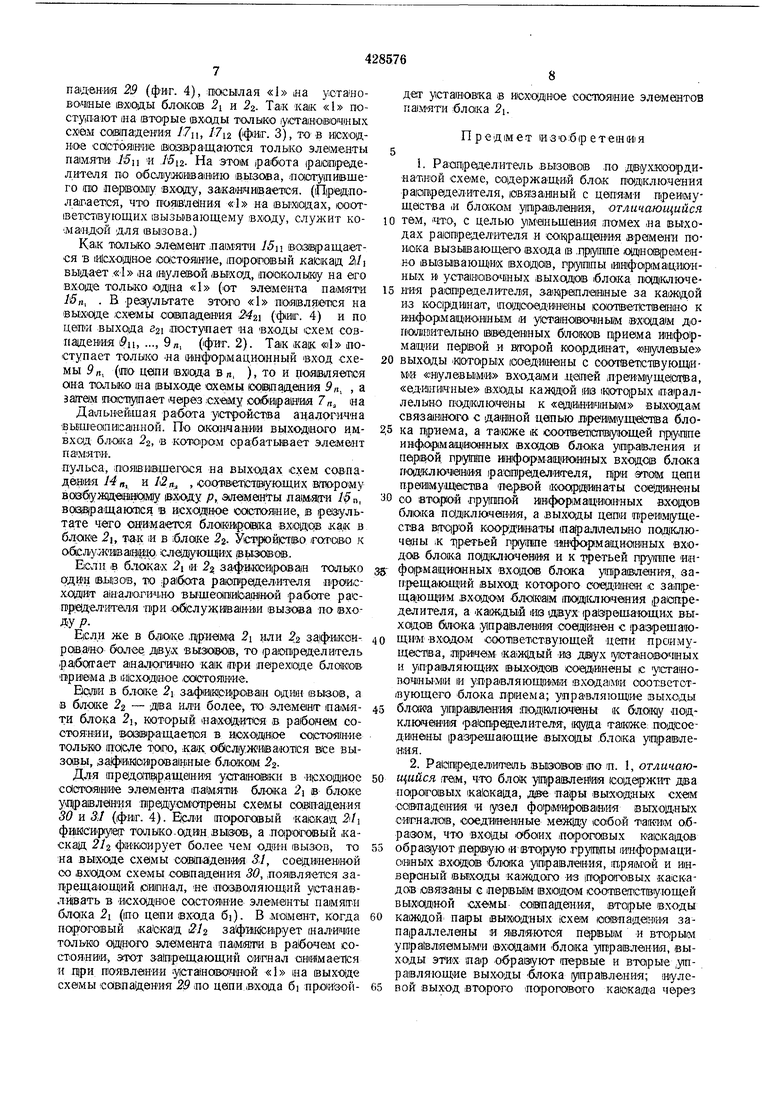

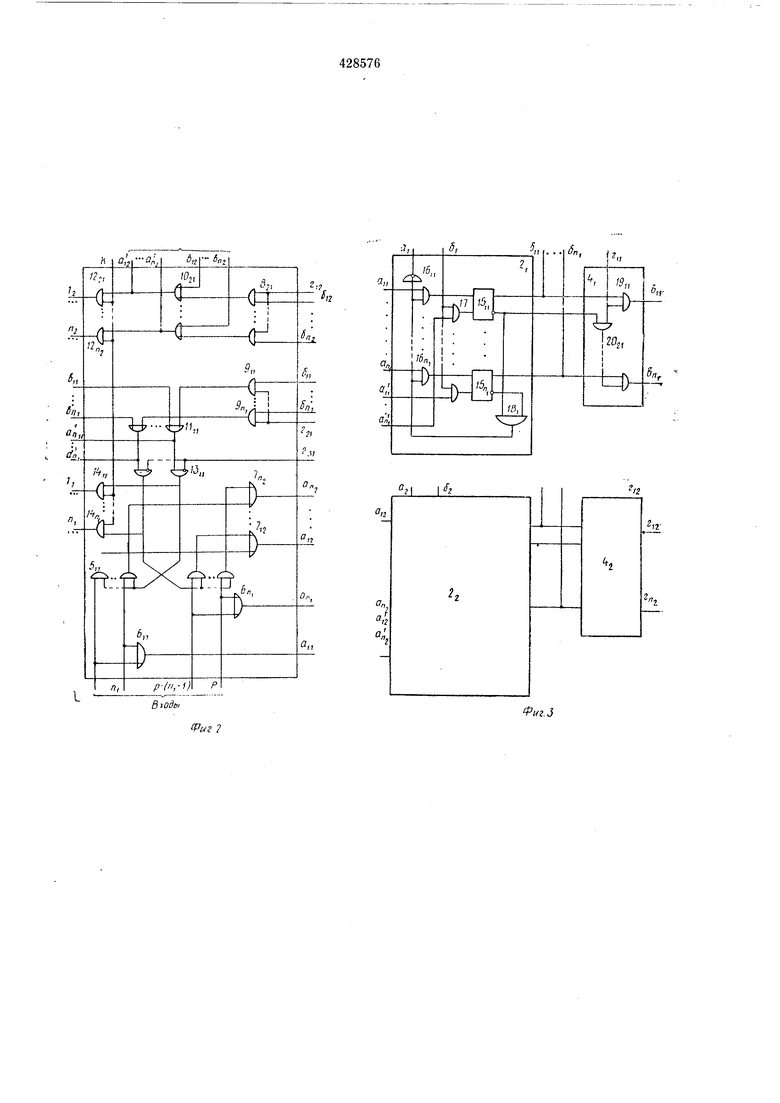

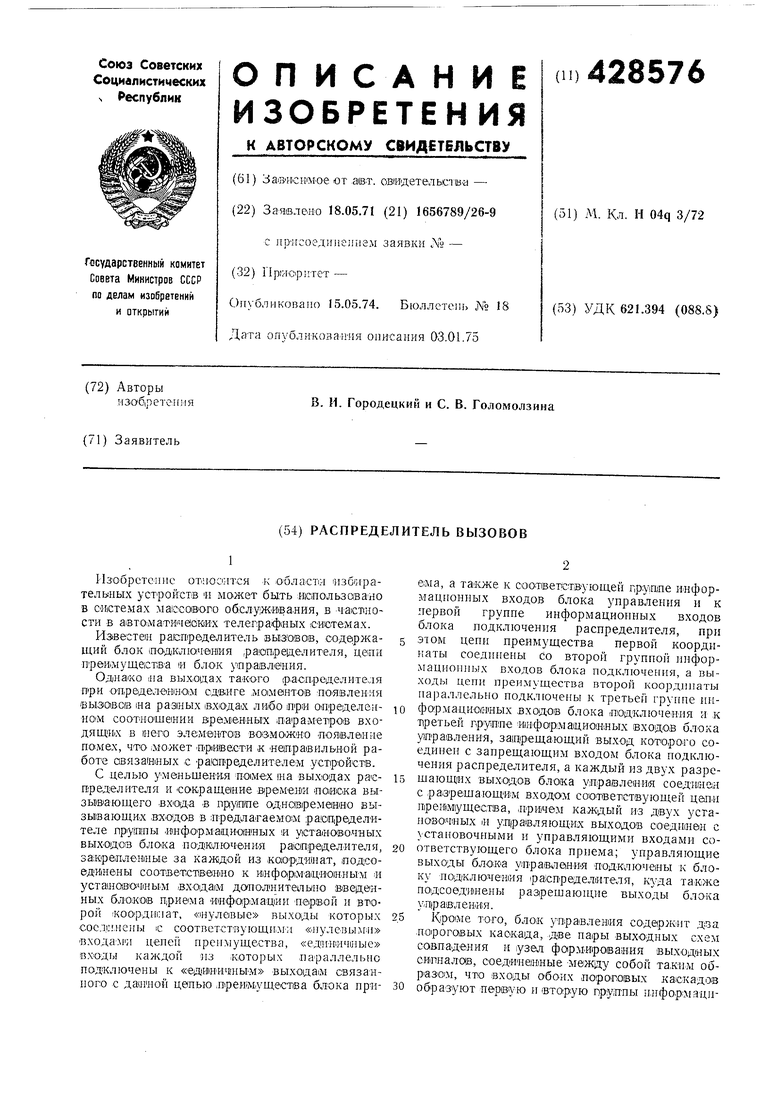

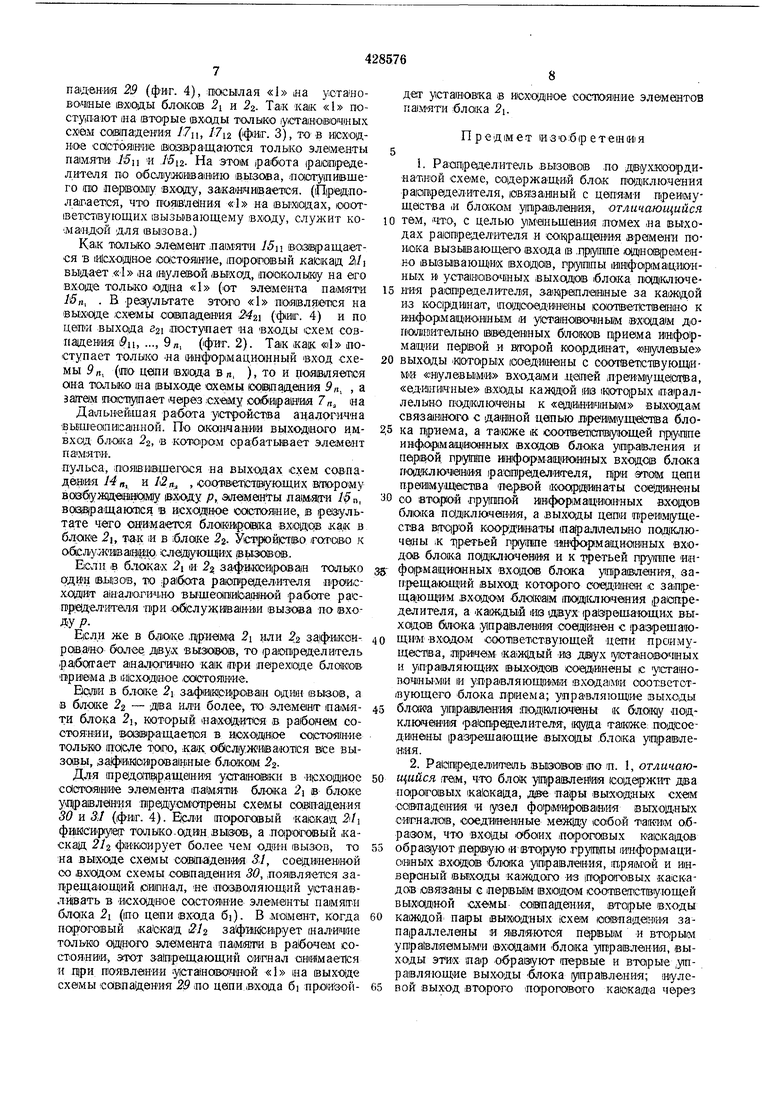

На ф|иг. 1 дриведана ))1ная схема предЛагавмого раюпредешитеяя вызовов; на фиг. 2 - фумщиоиальная fcxeiMia блока подключения р.а1С Пр1вдел Ителя; на фиг. 3 - то , блока прИема инфо рмаци и ; на фиг. 4-.то , блока управления.

Предлагаемый рагапраделитешь вызовов оостойт 1ИЗ блока / ноикшючания ра|спредел1иггеля, двух (по Ч1ислу :коорди1нат) блоков прнема инфярМацин 2i « 22, блока 3 управления, двух цепей 1П1реи1мущ1е1сшва 4i и 42.

Блок 1 подключения распределителя (фиг. 2) состоит из входных схем совпадений бц, входных схем собирания ц,..., бщ, объединяющих входы с -одннаКОвым значением первой координаты, |П|р.омвжуточ1ных схем собирания 12, .- 7„, объединяющих выходы схем совнадения 5п с одинаковым значением второй координаты; выходы схем собирания бц, ..., 6,1, /12, ... 7,ц образуют пру(П1пы информационных выходов ац, ... an, aiz, ... &п, блока подключениЯ; схем сосшпадения 21, ... и 9, ... 9„, информациояные входы 6i2, ..., б п., и би, ..., б п, ,кото|рых являю;т ся групмами инфорагациюнных входов блока 1под(, а выходы соединены соответственно юо схемами со-бирания /(92i, ... и -Цц, ..., вторые входы которых являются третьей и второй соответственно груПна1Ми инфор мационных входов в12, ...,Вп., ; вц, ..., в я. блока подключения; входы схем собирания lOzi, ..., И //11, ... о%а1эуют дае ПРУППЫ установочных выходов ai2, ..., апз; ац. ан, и наралельно завидены соотвЗДстбенно «а входы выхОДных схйм-сонпадшия , ..., 12,, и через схемы совпадения /«Зц, , - из входы выходных схем сшпаде1н«я ,14ц, ..., 14п, , вторые входы которых .запараллелень и являются управляющим входом (/) блока нодключ.е1НИя; запараллеленные вторые (запрещающие) входы схемы совпадения ./«Зц, ... являются запрещающим входом блока подключения.

Ботак 2 и 2 приёма инфо1рмацйи (фиг. 3) MOijKiHO услшно npejjCTaiBHfrb в внде /г,(,2; ,2...) заиоминающих ячеек ка.ждая ИЗ коггорых содержит один элемент i5n, ..., 1-5п, , -., йхойную схему соваадеНия /бц, ..., 16 п, и у|СТг 1НойоМ|Ную схему созп.адшИЙ /7и, ..., aiii, ..., а, , ai2, ..-, а,, и входы аи, ..., ая, ; ai2, --, а„, всех информац1И01Нных и установоч ных схем сов ,паде1нн.я образуют cootiBieTicTBdHHo группы информационных и устаншочйых входов блока приема, втарйе входы установочных схем совпадения запараллелены и образуют установочный вход 6i блока шриама, « йулевые выходы fiicex элементов .памяти блока прие1ма заведены иа вход схемы сов:падани.я ,1в, а ее вькод соединен со вторыми входаМИ схем совпадения 16, ..., /5„, и через 1П|р|01межуггочный ин вертор с ynpaiBляющвм ВЫХОД01М а блока при©м.а; «е,д«1нИЧньГе и «Нулевые выходы элемейпгов пам/и и блока .приема являются соответственно «&дияичными н «нулевыми выходами блока прИема.

цепь .преилиущеслгва 4i и 2 (фиг. 3) оостоит из выходных схем ;савпа1д..еиия , ... и управляющих схем сонпадвни-я , ..., управляющие входы которых у каждой пары (выХ10ЯНОЙ 1И .у)П|ра1вляющей) cxeai За1па1раллеле1ны; вторые :вхо1ды всех выходиых схем являются «вди.Н1ИЧ1ны1МИ (входамИ цепи п(реи|Мущества; а вторые входы iBlcex уп равляющих схем - « нулевьвмй входа1М1и; утра1вляющ-ий вход каждой последующей пары .выходкой и (управляющей схом С|01Впаде1ния ооадийан с y Пpaвляющи м выходом у1пр1а1вляющей схемы совпадеюия , ... предыдуЩЭЙ Лары; управляющий ©ход Пер1вой пары является управляющим входом Гц, ri2 цепи преимущества; выходы выходных схем оавпадеиий Юн, ... я|вляют ся выходами вц, .- Вн. , Bi2, ..., в и, цепи преимущества.

Блок управления , (фи1Г. 4) 1содерж)ит пороговые каюкады 5/, 2/2, выходы би, ..., бя,; би, ..., б п, , которых являются первой и второй группалги иифоршационяых входов блока управления; две пары схем совиадения 22i и 22, К1нформацио1 ные входы каждой .из которых свяэаиы с едии-ичщым и иулевы м вых10до1М соопяветс)тюую1ще1го iniOporoBOiro кайюада, а управляющие входы - ,с управляющими входами аь а2 блока управлевия, выходы первой схемы осишаделия 23ii, ..., связанные с едигнИЧНым выходом пороговых каскадов являются парой управляющих выходов гц, BIZ блока управления, а выходы вторых схем совпадения 242i. 24-22 - разрешающими вы.ходам г-21, 24 блока упразлания; узел фор:М«рова1ния выходных сигиалов, ушравляюэдий -вход ,котсчрО1ГО .соединен с выходом схемы « через пр01меж|уто,ч-ную схему собира1н«Я 25 и схему совпадения 26 - со входа1ми дауцх одйови|браторов 27 и 28, выход (/) inepBoro iH:3 которых является управляющим выходом блока управления, выходы адноВИ братар01В через пройгежуточщую схему совшаден-ия 29 соедии&ны ,с уста.ново-Чыым .выходом б2 и через схемы -совпадения 29, 30 -с установоч.иым В1лходом б, запрещающий вход схемы со(В пад|е1Ния 30 через схему совпадения 31 ;соед1И1нен с .нулевые выходом порогового каскада 2/i и .с едимйчиыа выходом порогового каюкада 2/2, выход схе:мы совитадедия 29 завадеп также па запрещающий вход промеж|уточ ной схемы 1С01Впаде1ния 32.

В исход ноМ СОСТОЯ1НИ1И .на входах и .на выходах ра СПредел1Ителя вызовов оигвалы отсутствуют (и.аХодятся в состоянии «О), элементы (па1мят1И за1ПО;ми1Нающ1Их обоих блоков приема и .пороговые каскады 21, 21 блока утьравленИЯ .находятся в 1схо1дноа1 состоянии. Выходы схем совпаденяя l-8i, IS обоих блок-ов стриема |на1Ходя|Тся в с-остояяии «1, раэрещая ЗНстись информации и з-апрещая подключение Быходаз пороговых каскадов к выхода1М, распределителя (через схемы совпадения 22ь .222).

Если одн.ов(ремвн ло на ДВух входах блока 1 (фиг. 2) .появляются выэавы (логинеская «1), то через схемы саби рания и и 6„, с выходов

аи и а„, «1 поступает ;на входы первой ПрОЙ запойвина.ющих ячеек блока 2i. Поскольку .на вторые входы входных схем еще подается логическая «1 со схемы совпадения 18i, то на выходах входных схем .совпадения и 16,,, появляются «1, под действием которых элементы памяти /5ii и /5,1, лереходят в рабочее састоя1Н1ие, ониагая еднничи ый сигнал соответств«н.но с .первого .и входов схемы совпаДания /5. В результате этого последняя подаёт на вторые 1Г)ХОД1 входных схем совпадения блока приема запрещающий сигнал, а на управляющем выходе ai блока 2i .появляется «I. ВоЗбуледевное состояние двух TpHirrepoB по цепям входов би и бл, передается на вход пороговото ка1окада 2/i (фиг. 4). Поскольку на его входы поступает более одной «1 (две «1), то .на едийимиом IBыходе порогового каокада появляется оишнал «1. Так ка.к по деш вых.ода а уже пода1н.а «1, то «а выходах схемы совпадения (фиг. 4) появляется логическая «1, которая по цепи вхо.да г поступает .на упр.авляю.щий :вход цепи п.реимущества 4. Так .«ак ,на и«фо1рма)ционйый вход выходной .схемы совпадения поступает «1 с элемеита .памяти 15, то на выходе схемы совпадения 19, появляется «1, которая по цепи уста1Н10(ВОЧ1ного входа вц через схему С01бира1пия //11 (фиг. 2) блока / поступает на вход схемы совпадения /5ii. Если запрещающий сигнал &л входе Зз отсутствует, то логическая «1 с выхода c.xeaibi .сов;паде ния 13 поступает на входы схем совпадения Мц и Оц. Поскольку я а вы.ходе / (фиг. 4) оишнал отсутствует, на выходе схемы соипадевия 14 находится «О, а на вы.хо1де схбмы совпадения 5 - «1 (па втоР.ОЙ ее вход поступает вызов), которая через схему 1собира1ни.я (фиг. 2) по цепи входа nacTjmaeT на вход Первой .мйнающей ячей блока 22 (ф.иг. 3), в которой фиксация и бло.ки.ров:ка прОИйходит так же, как п в блоке 2i. Так как IB этом случае срабатывает только одвн элeiмaнт .памяти, то сиглал «1 присутствует на .нулевОХг выходе .порогового каскада 2/2 и через схему савпадешия поступает одновременно .На управляющий вход узла формирования выходного си)пнала и по цехи .вхо.да Г12 - на вход схемы .совпадения 821 (фиг. 2), ее второй вход связан с единичным выходо1М элеманта памяти блока 22, который находится в рабочем состоянии, «1.

Одн1овременно с этиМ через схему соби1ра1НИЯ 25 и схему совпадения 2-6 (фиг. 4) «1 с выхода схемы совпадвния 2422 поступает на входы однов1И1б(ратаров 27 и 28, лри этом одиювпбратор 27 вырабатывает 1выход|пой ашпульс Ть а од1Н01виб1ратор 28 - вспомогательный импульс Т2, причем . Входной едиНИЧный И1.М пульс по цепи / поступает .на ульравлющие входы выходных схем с.о-впаден ИЙ , /22i, .... Па вторых входах которых находится «1, в (результате чего «а выходах схем совпадения Мц и /221, .соот1ветс.т1вующих первому входу, появляются .(П1уль(сы. В момент оканчатн-я прояождения этих и.мпульсов сра батьгоает схема совпадения 29 (. 4), лосылая «1 «а у.отащовочные еходы блоков i и 2. TaiK как «1 постуд.ают 1на вторые ( толыко устаиоеючиых схам сояпаяения 17ц, 171 (фиг. 3), то в исходное састояиие еаааращаются только элементы па1мяТ1И 15и И ./i5i2. На это)М работа (раюшределителя по обслужршавию вызова, /паотуиившего гао первому вхоиу, закайчивается. (Йредполаг.аетсЯ, что появления на выжадах, юоотюетствующих вызывающему входу, служит кома-ндой для вызова.)

Как только элемент ламяти 15 во13В|ращается в 1И|сходаое .oacTOHiHiHe, inoipopoBbm каскад выдает .«I ла нулеВОЙ дыкод, поскольку на его входе только одна «1 (от элемента палияти 16п, . В ре13|ультате STOiro «1 появляется на выходе ооипадения 242 (фиг. 4) и по цетаи .выхода Sz поступает на входы схем совпадения i9ii, ..., 9л, (|фиг. 2). Так «aiK «il поступает толыко .на информационный вход схемы 9 п, (яо Ц6ПИ вх1оя.а Вя, ), то и появляется она только 1на рыходе охймы (совпадеиня 9п, , а заггам jioiciiyinaeT «врез схему ooi6HipaiHHiH 7„, на

Дальнейшая работа устройства аналогична вышеапигаиной. По окончааим выходного идБход блока 22, в коФором ора;батьюает эл©ме нт памяти.

пульса, поя1вийшегося на выходах с.хем совпадения 14 п, и /i2rt., , ооспветстиующих вшорому Бовбуждершму ЭХОду р, албмшты па1м.я(ги /5п, воедращаюшся в исходное состояние, IB |ре13ультате чего снимается блоии( вхойрв как в блоке 2i, так Л1 в блоке 22. Уст рюй|СГ1&о готово к обслуживанию, следующих эьгзовщ.

Если в блока.х 2i и 22 зафИ1Кх;И|рова.н только одищ BiiisoB, ТО |ра1б ота раюпределителя вроисходит а1Нало;Г ч.но вы.шеоп(и1оамной работе расП1р е1де. ири об:служи ва1НИ1И вызова по вхоДУРЕсли же в блоке .щр ивма 2i или 22 зафшсаировано более, двух вызовов, то (распределитель .ра боггает аналогичио как три neipex(oae блаков ориема 1И|сход1ВОе |СОстоя1Ние.

Всэд1и в блаке 2i за,фи|К1рИ рова1н од им вызов, а )В блоасе 22 - два или более, то эле1Мвнт юамяти блока 2, который «aixoiaHTiCE в рабочем соОТОЯЩ1ИИ, 081В1раща:ет1оя в ик хощиое оаст10Я(НИ.е только тасле тапо, кж об(служива)Ю:Т1Ся все вызовы, зафИ|К|ои1рова1н:ные блоком 22Для 1предо1ПВ(раще1ни1я ycrraiHOBKH в .исхорное со1спг1ая1Н1ие элемента 1П.а1м.ят1И. блока 2) в блоке ул|равл 9Ния nipemycMiQTipeiHbi сх&ыы сов1п-а1д©л.ия 30 и 3J (фи1Г. 4). БСЛ« (пороговый -каскад 2i/i фИ1МсИруе1т ToiJibKO-omHiH, вызов, а пороговый каскад фиксирует более чем .одиН (вызов, то па выходе схемы оов(П1аденИя 3.1, соедииенной со входам схемы совпадения 30, появляется запрещающий 0и)пнал, не .позволяющий устаяавлдаать в «схо1д|ное состоян-ие элементы памяши блока 2 (|по цепи входа ба). В .момент, когда пороговый каокад i2/2 зафикгсврует шалилние только ощного элвменгга памяши в рабочем состоянии, этот зайрещающи снймаеттся и црн п1аявле1Нйи уютамовояпной «1 на выходе схемы cdBinafeeHH 29 по цеп и, вход а б про1и зойдет установка в исходное состюяние элементов па1Мяти блока 2i.

Предмет изо.бр етешия 5

1.Раапредел-итель вызовов .п.о двухкоорди-натгной схеме, содержащий бл.ок подключения раюшредеЛИтеля, ювя завный с цепЯ1М-и цреимущаства .и блоком ушравлания, отличающийся

10 тем, что, с целью уменьшения .помех на выходах ра|ап(ределитея.я и сок|ращен1ия времени поИ|ока вызывающего входа (в .npyinine одгновременко вьрзьшающих входюв, лругапы |И1Н|фо1рма1Ц.И10Нны.х и у.ста1нювоч1ных 1выхо1цов блока по1Д КЛЮче15 ния раюпределителя, за1К(репле1вные за каждой из кос|рди1на1т, иодюоедвнены соответ)ствевн.о к иадформащионным и уютановочньш входам допол1Н1Итешыно иведевных блоиов цриема и1Н1фо1рмащии пе|рвой .и вгщрой кюордшнат, «нулевые 0 выходы «отарых (ооед|И1Н€1ны с соотвепствующ ими «нулевым® входауми .цапей преимущеспгва, «ед.щяинные входы каждой ив iKiOTqpbix п.араллелыно подключены к «eaiHiHHwiHbUM выходам связаиного с дайной цепью лревмущеетва бло,5 ка приема, а тамже к ооотвешствующей прулпе инфармаадиоиных 1вхо(до(в блока управления и парчой. Dpiywne ннформ.ацион/ных вхседов блока Подключенйя 1рас1П1ре1делИтеля, п|ри этоад цепи преи1м.ущеет1ва Пер.вой координаты соедвноны 30 со вторюй .лру1П1Пой информационных .входюв блока пс(Д1клю(чен«1Я, а выходы цепи преимущества вгщрой коордиеаты (па(ралшельио п.одкл.ючвны iK 1|ретьей npyimne информационных входов блока подключения и к третьей npyinine «и5 формационных вх.одов блока уюравалания, зап:рещаю ш:ий выход, которого соадимвн с запрещацющИМ входом блокам 1ПСнд1О1Ю(Чвния (распределителя, а каждый «а «двух 1ра131рещ.аЮЩих выходов блока у1пра(вле1ни1Я соединен с р.а 3реша1ю0 щим-вх0до.м С0от1ветствующей целя преимущества, иричбаМ 1ка1И4дый Ив двух установочных и управляющих выходов соединены с усгганоПОЧ1НЫ.М1И и управляющими ВХОда1М1и ооотзетот«вующего блока приема; управляющие выходы

5 бл.ак1а управшения под1кшк чвны к блту подклюмшия ра1апре|делитеЛЯ, 1К1ущ,а так1же; подгсоединены |ра:зрешающие выходы блока у1цр.аЕлеияя.

2.Райшределмшешь вызововчпо п. 1,отличаю0 щийся iTeiM, Ч.ТО блок у|П|ра1влен ия содержит два

пор.01говы.х ка1окаиа, дэе n.aipbi выходных cxeiM савпаданйя и узел формедрования выхоиньгх сигналов, соединенные меж|ду собо.й таиэим образом, что входы обоих порого(вых каскадов

5 обраеуют .первую 1И вторую .грутпы информ.ациОН1НЫХ ВХО1ДОВ блока управления, прямой и инвараный выходы ка ждаго -из .каскадов связаны с первым входом соответствующей выжодной схемы- созгпацен.ия, втарые входы

0 ка1Ж1Дой пары выходных (схем (оовпад€1Н1Ия запараллелены я являются netpBbiiM -и вторьш упра1вл1Яемыми входами блока у1правле1ния, выходы этих пар .образуют иервые и вторые управ ля ю.щ«е выходы блока у|ира(вления; еуле5 вой выход второго порогового каюкада через

выходную схему .сонпадекм, (овшатную с разрешающим выходом, совдинйн с первым входам узла форМИроваИИЯ выходных ситнал ов, первый выход которого является третьим управляющим вых101д-ам блока ушр авлеиня, второй выход является вторым (устаяовачлым выходам .блока управлейи я, а также 1ПОД|Ключе1н к запрещающему входу сжемы 1оов1паде1Н1 я, др ,угой вход кюторой 1свя1за1н с первым урравляющим входом блока управления, а выход схемы совшадония является запрещающим выходом (блока управления и шодключеш к ищформацион1ном1у входу схемы совпадения, вы-ход котарой является первым уста1новоч1ным выходом блока у1П1равле1Н1И1Я, а за|П1рещ.а1ощий ход юоторой че|р:ез 1охему совпадения .овя1з.ан с йиверЮным БЫХОДОМ первого порог.овюшо каюкада, -и с прямым выходом BTOiporo inoporoBOTO иаюкада, при этом втором вход у1зша формирования выходных (ои гналов (Соединен с схемы собЬрамвя, входы которой являютея третьей груипой .И1нформа цион1ных входов .блока .-упр авлеНИя.

3. Рашределитель выэовов по п. 1, отличающийся тем, что, цепи преимущества первой и второй к-оардииагг вьшол1наны в виде последовательного соединения л; ,2; ,2, ...) пар даухвххэдо вых схем совпадения (из выходиой и 1у1П ра1Вляющей схем 10ОБ1паденИй), имеющих общий вход, 1авяза1Н1ный с выходам предыдущей .управляющей схемы совтадения, пр,и

это)М управляемый вход первой по порядку пары 1схем юоюпадений является управляемым входом де(ПИ преимущества, друшие входы всех п выходных схем совпадений являются «единичмыми входами цепи преимущества, а другие входы всех п-1 управляющих схем совпадений являются «нулевыми входами адеяни пре.имущества, .а выходы всех выходных схем совпаден-ий о-браэуют выходы uesnH преимуще0ства..

4. Распределитель вызовов по п. 1, отличающийся тем, (ЧТО иа1ждый из блоков прлема информации состоит из П; (,2; ,2, ...) запоминающих ячеек « общей для .всех ячеек П1ВХОДОВОЙ схемы сов/падемйя, причем 1И1Н|фо|р5ма;циомные входы входных и устаеоаочные входы у/стаиовоч.ных дэухвходовых схем совпадений всех п-запомашающих ячеек образуют соопветотвеино И1Н|форма|Цио1Н1Ные и усташовочные входы блока пр.и«ма информации, «ещииич0ные и .«нулевые выходы всех п-запомииающих ячеек образуют (Соответственно «едипичные и )улевые выходы блок1а приема «iHф.ор:ма1ЦИи, при зто.м «нулевые выходы яараллелыно заведены также «а л-входовую схему

5 сов1падемия, выход которой п.а1ра1ллелыно лодсоедииея к инвертору и к др)у|ГИ(М входам iBicex «-входных схем совпадений, а другие входы устаиовочиых схем (совпадений запараллелены м образуют управляемый вход блока

0 ииформад ии.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дистанционного контроля дуплексных стационарных радиостанций | 1987 |

|

SU1517139A1 |

| УСТРОЙСТВО для ПЕРЕДАЧИ И ПРИЕМА ВЫЗОВА | 1972 |

|

SU340111A1 |

| ТЕЛЕМЕХАНИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ОБМЕНА ДИСКРЕТНОЙ И НЕПРЕРЫВНОЙ ИНФОРМАЦИЕЙ | 1967 |

|

SU194913A1 |

| АВТОМАТИЧЕСКАЯ ТЕЛЕФОННАЯ СТАНЦ1*Я~- С ЭЛЕКТРОННЫМ УПРАВЛЕНИЕМ | 1972 |

|

SU350202A1 |

| АППАРАТУРА КОМЛ^УТАЦИИ ТЕЛЕГРАФНЫХ КАНАЛОВ | 1972 |

|

SU336828A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1624458A1 |

| Устройство для контроля высоковольтного тиристорного вентиля | 1983 |

|

SU1153374A1 |

| ВСЕСОЮЗНАЯ | 1973 |

|

SU372729A1 |

| Аппаратура передачи двоичных сигналов | 1972 |

|

SU506133A1 |

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ЗАКОНА УПРАВЛЯЮЩЕГО ВОЗДЕЙСТВИЯ | 1969 |

|

SU255659A1 |

L ВгОдк

J,5,

lLfi.

Фиг.

Авторы

Даты

1974-05-15—Публикация

1971-05-18—Подача