ляющих и один информационньш входы, дополнительным кодирующим -сумматором дополнительным счетчиком, дополнителнъы элементом И-ИЖ, коммутатором, блоком элементов И-ИЛИ-НЕ, имеющим три управляющих и один информационный входы и информационный выход, а также блоком выбора по большинству, причем информационный вход блока счетчиков подключен к выходу селектора, два управляющих входа - к выходам сигналов проверки каналов обработки информации блока распределения сигналов, а инфо)мационные выходы - к первому входу блока элементов ИЛИ и к входу дополнительного кодирукщего сумматора, выход которого через дополнительный счетчик соединен с информационным входом блока сравнения, управляющие входы дополнительного счетчика и блока сравнения соединены соответственно с выходами сигналов разрешения записи и сравнения информации блока распределения сигналов, вход возврата в исходное состояние которого подключен к выходу блока сравнения, блок выбора по большинству через когв утатор подключен к выходу блока памяти, управляющий вход блока выбора по большинству подключен к выходу сигналов разрешения голосования блока распределения сигналов, позиционный выход - к второму входу первого элемента сложения по модулю два, являющемуся позиционным входом блока контроля управления, а выход - к информационному входу блока элементов И-ИЛИ-НЕ, первый вход которого соединен с адресным входом коммутатора и с выходом сигналов адресов считывания, блока распределения сигналов, второй управляющий вход --с выходом сигналов на разрешение вьщачи информации блока распределения сигна лов, третий управляющий вход - с выходом первого элемента сложения по модулю два, являкщимся соответствующим выходом блока контроля управлени а информационный выход соединен с входами блока вьщачи результата и блока индикации, управляющие входы которых подключены к выходу сигналив разрешения записи выходной информаци блока распределения сигналов, а их дополнительные выходы через дополнительный элемент И-ИЛИ соединены с входом контроля выходной информации блока распределения сигналов, выходы блока контроля записи и блока срайнения и обнуления подключены соответственно к входам сигналов обнуления и повторения записи выходной инфор-мации блока распределения сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля тиристоров высоковольтного вентиля | 1980 |

|

SU1108554A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для считывания и отображения графической информации | 1986 |

|

SU1506459A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

| Запоминающее устройство | 1985 |

|

SU1305772A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| Устройство для диагностирования периферийных устройств | 1990 |

|

SU1716518A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

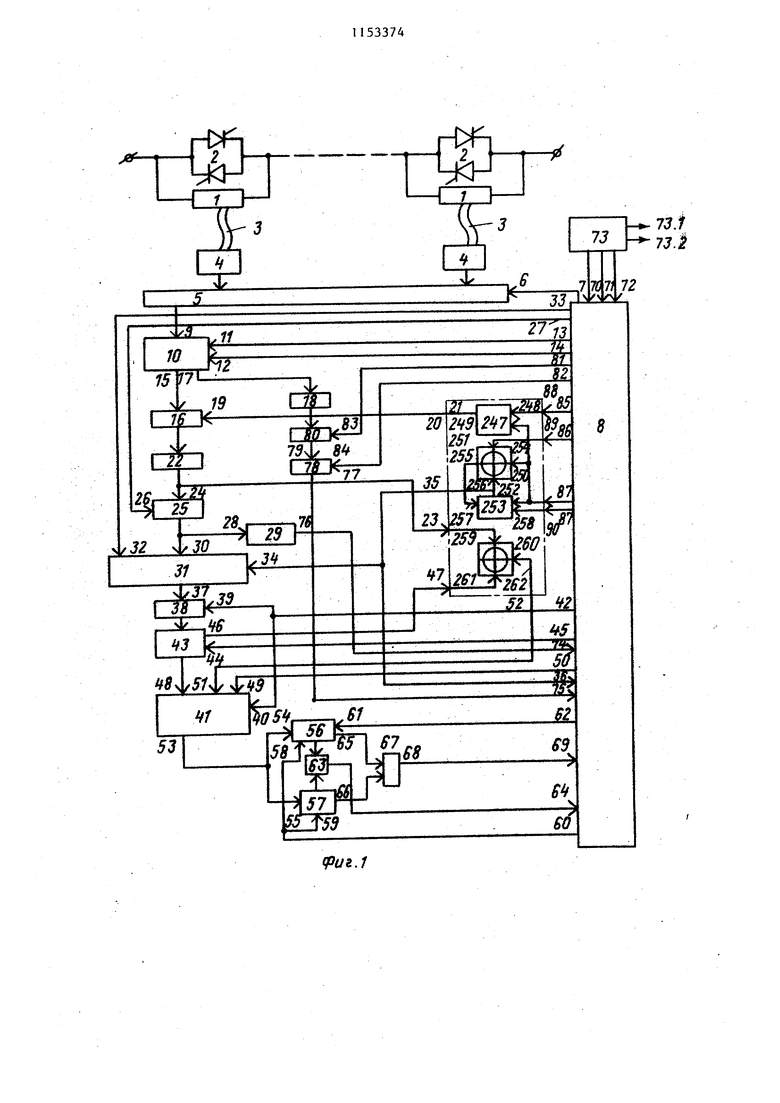

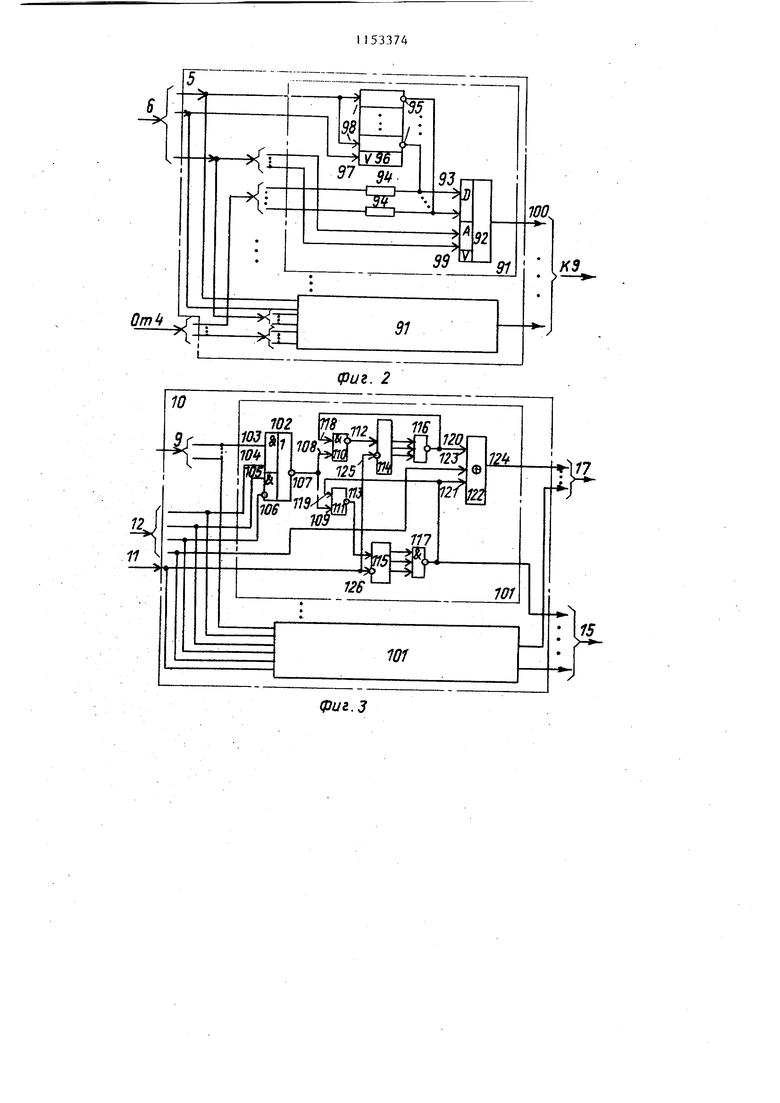

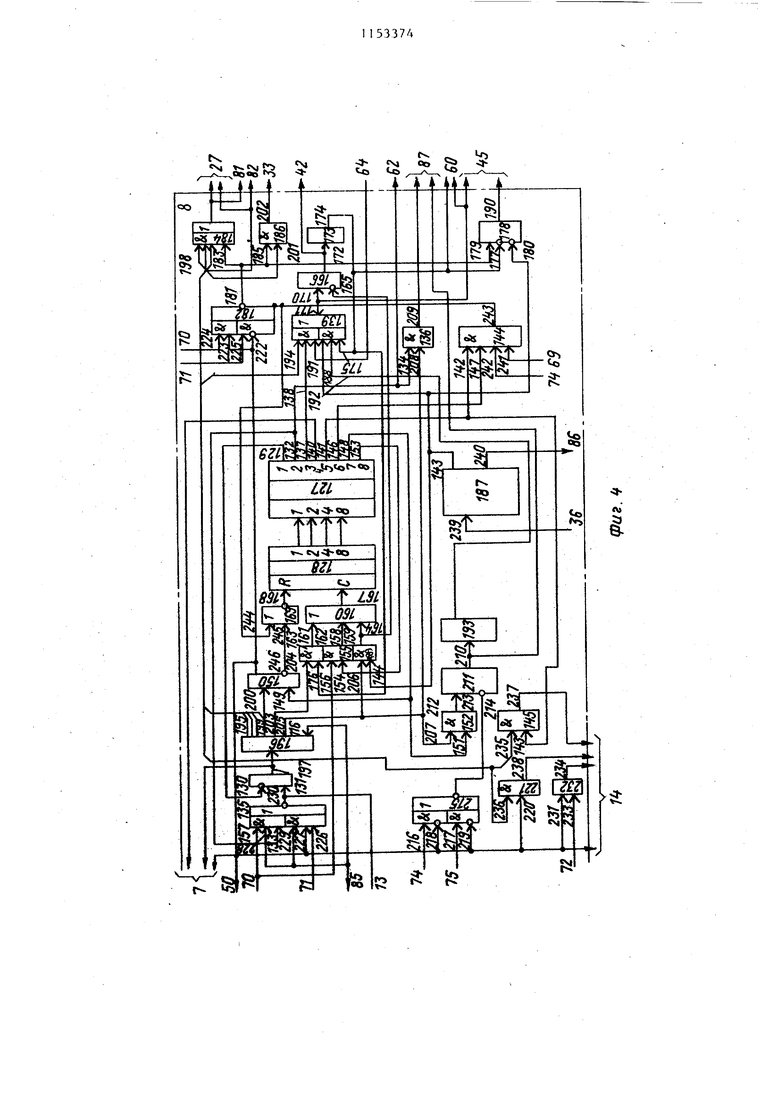

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ВЫСОКОВОЛЬТНОГО ТИРИСТОРНОГО ВЕНТИЛЯ, содержащее датчики напряжения по числу тиристоров в вентиле, подключенные входами к соответствукщим тиристорам, а выходами - через световоды к соответствующим детекторам, селектор,-ВХОДЫ которого соединены с выходами соответствующих детекторов, блок контроля управления, включающий в себя первый элемент сложения по модулю два, второй элемент сложения по модулю два с управляющим входом, оперативньш счетчик и дешифратор сдвига, блок распределения сигналов, выход сигналов, определяющих интервалы прохождения информации от группы тиристоров, которого подключен к входу управления селектора, выходы сигналов управления дещифратрра сдвига, управления вторым элементом сложения по модулю два, управления оперативного счетчика подключены к соответствующим входам блока контроля управления, блок эле-. ментов ШШ, одним входом связанный с выходом селектора, а вторым - с выходом дешифратора сдвига, являющимся информационным выходом блока контроля управления, информационный вход которого, являющийся первым входом первого элемента сложения по модулю два, подключен к выходу кодирующего сумматора, входом соединенного с выходом блока элементов ИЛИ, счетчик, управляющий вход которого подключен к выходу сигналов разрешения записи информации блока распределения сигналов, информационный вход - к выходу кодирующего сумматора, а выход - к входу блока сравнения и обнуления и к информацион(Л ному входу блока памяти, управляющий вход которого подключен к выходу сигналов разрешения перезаписи информации блока распределения сигналов, адресный вход - к вьосоду оперативного счетчика, являющемуся соответствующим выходом блока контроля управления, к адресному входу блока распределения сигналов, а выход свяел зан с блоком выдачи результата и с 00 блоком индикации, выходами подключенсо ными к блоку контроля записи, вход запрета блока выдачи результата под4;а ключен к выходу сигналов запрета блока распределения сигналов, блок тактовых импульсов, содержащий п каскадов деления частоты импульсов, выходы которых являются выходами , блока и подключены к входам тактовы:4 импульсов блока распределения сигналов, и блок сравнения, отличающееся тем, что, с целью повышения надежности, оно снабжено блоком счетчиков, имеющим два управ

Изобретение относится к высоковольтной преобразовательной технике, а именно к системе контроля узлов высоковольтного тиристорного вентиля (ВТВ).

Известно устройство, содержащее ряд последовательно соединенных тиристоров, каждый из которых имеет ячейку управления, управляемую общей схемой регулирования вентиля. В каждой ячейке имеется датчик пороговых импульсов.. Импульсы поступают на детекторы и регистрируются селектором, который по каналу передает их на вычислительное устройство. Между детекторами и селектором могут быть установлены запоминающие элементы для накопления импульсов иЗ.

Однако отсутствие контроля в приемной системе ВТВ снижает надежность устройства и достоверность принимаемой информации.

Известно также устройство, содер.жащее управляющий канал, обратньй канал и мультиплексор, посредством которых осуществляется передача и прием данных, фотоусилители, подключенные к элементам памяти для последующей последовательной обработки данных и накопления С2.

Недостатком данного устройства является собственно синхронная обработка данных, влекущая за собой перегрузку управляющего канала ВТБ, усложнение логической части на потенциале каждой ячейки и, соответственно, в системе управления ВТВ. При этом отсутствие контроля в устройстве снижает его надежность. I Наиболее близким к предлагаемому по технической сущности является устройство для контроля высоковольтного тиристорного вентиля, содержащее датчики напряжения по числу тиристоров в вентиле, входами предназначенные для подключения к соответствующим тиристорам, а выходами через световоды подключенные к соответ ствующим детекторам, селектор, входы которого соединены с выходами соответствующих детекторов, блок контроля управления, включающий в себя первый элемент сложения по модулю два, второй элемент сложения по моду лю два, оперативный счетчик и дешифратор сдвига, блок распределения сиг налов, выход сигналов, определяющих интервалы прохождения информации от группы тиристоров, которого подключен к входу управления селектора, выходы сигналов управления дешифратора сдвига, управления вторым элементом сложения по модулю два, управления оперативного счетчика подключены к соответствующим входам блока контроля управления, блок элементов ИЛИ, одним входом связанный с выходом селектора, а вторым - с выхо дом дешифратора сдвига, являющимся информационным выходом блока контрол управления, информационный вход Которого, являющийся первым входом пер вого элемента сложения по модулю два подключен к выходу кодирующего сумматора, входом соединенного с выходом блока элементов ИЛИ, счетчик, управлякшцсй вход которого подключен к выходу сигналов разрешения записи информации блока распределения сигналов, информационный вход - к выходу кодирующего сумматора, а выход - к входу блока сравнения и обнуления и к информационному входу блока памяти, управляющий вход которого подключен к выходу сигналов раз решения перезаписи информации блока распределения сигналов, адресный вход - к выходу оперативного счетчика, являющемуся соответствующим выходом блока контроля управления, и к адресному входу блока распределения сигналов, а выход связан с блоком вьихачн результата и с блоком индикации, вьосодами подключенными к блоку контроля записи, вход запрета блока выдачи результата подключен к выходу с;игналов запрета блока распределения сигналов, блок тактовых импульсов, содержапцад п каскадов деления частоты импульсов, выходы которых являются выходами блока и подключены к входам тактовых импульсов блока распределения сигналов, и блок сравнения L3 J. Однако при работе вентиля в статическом компенсаторе реактивной мощности возможна вьщача ложной информации об отказе тиристорных ячеек. Уменьшить вероятность вьвдачи ложной информации об отказе тиристоров мож;но путем ограничения угла регулирования. Этот общепринятый способ не обеспечивает правильную работу известных устройств, например, из-за ошибок фазирования или параметрических отказов элементов фазосдвигающих цепей. Целью изобретения является повьщ1ение надежности. Поставленная цель достигается тем, что устройство для контроля высоковольтного тиристорного вентиля, содержащее датчики напряжения по числу тиристоров в вентиле, подключенные входами к соответствующим тиристорам, а выходами - через световоды к соответствующим детекторам, селектор, входы которого соединены с выходами соответствующих детекторов, блок контроля управления, включающий в себя первый элемент сложения по модулю два, второй элемент сложения по модулю два с управлякидим входом, оперативный счетчик и дешифратор сдвига, блок распределения сигналов, выход сигналов, определяющих интервалы прохождения информации от группы тиристоров , которого подключен к входу управления селектора, выходы сигналов управления дешифратора сдвига, управления вторым элементом сложения по модулю два, управления оперативного счетчика подключены к соответствующим входам блока контроля управления, блок элементов ИЛИ, одним входом связанный с выходом селектора, а вторым - с выходом дешифратора сдвига, являющимся информационнымч выходом блока контроля управ ления, информационный вход которого, являкщийся первым входом первого элемента сложения по модулю два, подключен к выходу кодирующего сум матора, входом соединенного с выходом блока элементов ШШ, счетчик, управляющий вход которого, подключен к выходу сигналов разрешения запис информации блока распределения сигналов, информационный вход - к выходу кодирующего сумматора, а выход к входу блока сравнения и обнуления и к информационному входу блока памяти, управляющий вход которого подключен к выходу сигналов разрешения перезаписи информации блока распределения сигналов, адресный вход - к выходу оперативного счетчи ка, являющемуся соответствукщим выходом блока контроля управления, и к адресному входу блока распределения сигналов, а выход связан с бл ком выдачи результата и с,блоком индикации, выходами подключенными к блоку контроля записи, вход запре та блока вьщачи результата подключе к выходу сигналов запрета блока рас пределения сигналов, блок тактовых импульсов, содержавши п каскадов деления Ч:астоты импульсов, выходы которых являются выходами блока и подключены к входам тактовых импуль сов блока распределения сигналов, и блок сравнения, снабжено блоком счетчиковi имеющим два управляющих и один информационный входы, дополнительным кодирукяцим сумматором, дополнительным счетчиком, дополнительным элементом И-ИЛИ, коммутатором, блоком элементов И-ИЛИ-НЕ, име ющим три управляющих и один информа ционньй входы и информационный выход, а также блоком выбора по большинству, причем информационный вход блока счетчиков подключен к выходу селектора, два yпipaвляюlциx входа к выходам сигналов проверки каналов обработки информа101И блока распределения сигналов, а информационные выходы - к первому входу блока элементов ИЛИ и к входу дополнительного кодирующего сумматора, выход которого через дополнительный счетчик- соединен с информационным входом блока сравнения, управляющие входы дополнительного счетчика и сравнения соединены соответственно с выходами сигналов разреше нйя записи и сравнения информации блока распределения сигналов, вход возврата в исходное состояние котор го подключен к выходу блока сравне3746ния, блок выбора по большинству через коммутатор подключен к выходу блока памяти, управляющий вход блока выбора по большинству подключен к выходу сигналов разрешения голосования блока распределения сигналов, позиционный выход - к второму входу первого элемента сложения по модулю два, являющемуся позиционным входом блока контроля управления, а , выход - к информационному входу блока элементов И-ИЛИ-НЕ, первый вход которого соединен с адресным входом коммутатора и с выходом сигналов адресов считывания, блока распределения сигналов , второй управляющий вход - с выходом сигналов на разрешение вьщачи информации блока; распределения сигналов, третий управляющий вход - с выходом первого элемента сложения по модулю два, являющимся соответствующим выходом блока контроля управления, а информационный выход соединен с входами блока вцдачи результата и блока индикации, управляющие входы которых подключены к выходу сигналов разрешения записи выходной информации блока распределения сигналов, а их дополнительные выходы через дополни тельный элемент И-ШШ соединены с входом контроля выходной информации блока распределения сигналов, выходы блока контроля записи и блока сравнения и обнуления подключены соответ.ственно к входам сигналов обнуления и повторения записи выходной информации блока распределения сигналов. В предлагаемом устройстве косвенно оценивается длительность приложения напряжения к вентилю, формируется дополнительный сигнал блокировки команд защиты и сигнализации при уменьшении длительности указанного напряжения сверх определенной величины, например 100 мкм. Поскольку эта величина соизмерима с длительностью фронта приложенного напряжения, пробои тиристоров здесь маловероятны. Если длительность приложенного напряжения превьипает 100 мкс, все тиристоры вентиля контролируются. Датчики напряжения вырабатывают последовательности импульсов. Каждому датчику соответствуют два счетчика импульсов, установленные на потенциале земли. Один счетчик считает до двух, другой до четырех. Если оба счетчика дoc гитaли до двух и четырех, то это означает, что напряжение на тиристорной ячейке имеет достаточную амплитуду и длительность- тиристоры не пробиты. Если оба счетчика не досчитали до двух и до четырех, то это означает, что напряжение на тиристорной ячейке отсутствует (либо снято напряжение с вентиля, либо тиристоры пробиты ) или отказал информационный канал. При снятом напряжеции ложная работа устройства предотвращается известными способами Если один счетчик досчитал до двух, а другой не досчитал до четырех, то это означает, что датчики не вырабатывают последовательности импульсов напряжение на вентиле имеет малые дл тельности и амплитуду (амплитуда мал ввиду малой величины скорости нарастания напряжения, определяемой пара метрами демпфирующих цепей вентиля) При такой работе одного, двух или более информационных каналов должен быть вьщан запрет на срабатывание цепей защиты и сигнализации тем самым предотвращается ложная работа системы контроля тиристорнык ячеек вентиля при уменьшении угла управления вентилей. На фиг. представлена функциональная схема устройства для контро ля ВТВ; на фиг. 2 и 3 - селектор и блок счетчиков соответственно; на фиг. 4 - блок распределения сигналов; на фиг. - соответственно блок выбора по больш1шству, блок элементов И-ИЛИ-НЕ и блок выдачи результата; на фиг. 3 - схема сложения по модулю два с управлением. Устройство контроля высоковольтного тиристорного вентиля имеет датчики 1 напряжения по числу тиристоров 2, подключенные входами к соответствующим тиристорам 2. В качестве датчиков используется простейший релаксатор со свето диодом в цепи нагрузки. Выходы датчиков I подключены через световоды 3 к соответствующим детекторам А, лреобразукицие световые сигналы в электрические и выходы которых подключены к соответствующим входам се лектора 5. Управляющие входы 6 подсоединены к выходу 7 сигналов, определяющих интервалы прохождения информации от группы тиристоров бло ка 8 распределения сигналов. Селектор 5 может содержать дополнительные входы для контроля иных последовательностей импульсов, кроме последовательностей импульсов от датчиков контроля тиристоров. Выход селектора 5 подключен к информационному входу 9 блока 10 счетчиков, первый II и второй 12 управляющие входы которого подключены соответственно к выходам 13 и 14 сигналов проверки каналов обработки информации блока 8 распределения сигналов. Первый информационный вьиод 15 блока 10 счетчиков, являющийся также первым информационньм выходом устройства.подключен к первому входу блока 16 элементов ИЛИ. Второй информационный выход 17 блока 10 счетчиков подключен к дополнительному кодирующему сумматору 18. Кодирукяций сумматор 18 содержит группы одноразрядных двоичных сумматоров, причем одноразрядные двоичные сумматоры каждой группы образуют пирамиду одноразрядных двоичных сумматоров, входы одноразрядных двоичных сумматоров первой группы соединены с шинами первого входа и шиной низшего разряда второго входа кодирующего сумматора. Входь одноразрядных сумматоров каждой последующей группы соединены с выходами переноса одноразрядных двоичных сумматоров предьщущей группы и шиной соответствующего разряда второго входа кодирующего сумматора, выходы каждой группы одноразрядных двоичных сумматоров соединены с соответствующими -шинами выхода кодирующего сумматора. Блок 16 элементов ИЛИ вторым входом 19 подключен к ииформациониому выходу 20 блока 21 контроля упра вления, а выходом подключен через кодирующий сумматор 22 к информационному входу 23 блока 2 контроля управлеиия и к информационному входу 24 счетчика 25. В данном устройстве кодирукхциЙ сумматор 22 выполнен так же, как и сумматор 18. Блок 21 контроля управления выполнен на базе микросхем серии К155. Управлякиций вход 26 счетчика 25 , присоединен к выходу 27 сигналов разрешения записи информации блока 8 распределения сигналов, выход счетчика 25 подключен к входу 28 блока 29 сравнения и обнуления и к информаци онному входу 30 блока 31 памяти. Счетчик 25 содержит преобразователь двоичного кода в двоично-десятичный и счетчик, либо просто счетчик, если информация записывается в двоичном коде. Выходы разрядов счетчика, соединенные с вторым входом кодирующего сумматора (на фиг, 1 связи не показш ы), являются выходом счетчика. В качестве блока 3I памяти использована микросхема К155РУ2. Управлянщий вход 32 блока 31 памяти присоединен к вь1ходу 33 сигналов разрешения перезаписи информации блока 8 распределения сигналов, адре ньй вход 34 подключен к соответствующему выходу 35 блока 21 контроля управления и к адресному входу 36 блока 8 распределения сигналов, а выход 37 блока 31 памяти подключен к входу коммутатора 38, в качестве которого использована микросхема К155КП7, адресный вход 39 которого подключен к первому 40 управляющему входу блока 4I элементов И-ИЛИ-НЕ и к выходу 42 сигналов адресов считывания блока 8 распределения сигналов, а выход коммутатора 38 присоед нен к блоку 43 выбора по большинству. Блок 43 выбора по большинству уп равляющим входом 44 подключен к вых ду 45 сигналов разрешения голосования блока 8 распределения сигналов, позиционный выход 46 подключен к входу 47 блока 21 контроля управления. Выход блока 43 выбора по большинству присоединен к информационно му входу 48 блока 41 элементов И-ИЛИ-НЕ, второй управляюп й вход 49 которого подключен к выходу 50 сигналов на разрешение вьщачи инфор мации блока 8 распределения сигналов, Третий управляющий вход 51 блока 41 элементов И-ИЛИ-НЕ подключен ко вто рому 52 выходу блока 2I контроля управления, выход 53 блока 41 элеме тов И-ИЛИ-НЕ, подключен к входам 54 и 55 соответственно блока 56 вьщачи результата и блока 57 индикации, управляющие входы 58 и 59 которых присоединены к выходу 60 сигналов разрешения записи выходной информации блока 8 распределения сигналов, I . В данном устройстве блок 57 индикации выполнен так же, как -и блок 56 выдачи результата (см, фиг, 7/, за исключением того, что на выходе блока установлен индикатор вместо реле. Вход 61 запрета блока 56 выдачи результата присоединен к выходу 62 сигналов запрета блока 8 распределения сигналов. Выходы блока 56 выдачи результата и блока 57 индикации подсоединены к входам блока 63 контроля записи, выход которого присоединен к входу 64 сигналов обнуления блока 8 распределения сигналов, Информационный выход блока 56 выдачи результата является вторым информационным выходом устройства. Блок 63 контроля записи представляет собой (см, фиг, 8 ) элементную схему Сложения по модулю два, четыре выхода которой объединены с помощью элемента ИЛИ, Соответствующие дополнительные выходы 65 и 66 блоков 56 и 57 выдачи результата и индикации подключены к элементу 67 И-ИЛИ, выход 68 которого подключен к входу 69 контроля выходной информации блока 8, Блок 8 распределения сигналов своими входами 70, 71 и 72 тактовых импульсов подключен к соответствующим выходам блока 73 тактовьк импульсов (выход 73 которого является выходом устройства с адреса-, ми контролируемых цепей, а выход 732 является вторым управЛякщим выходом устройства), а входами 74 повторной записи выходной информации и 75 возврата в исходное состояние присоединен соответственно к выходу 76 блока 29 сравнения и обнуления и к выходу 77 блока 78 сравнения, который информационным входом 79 подключен через дополнительный .счетчик 80 к выходу дополнительного кодирующего сумматора 18, В данном устройстве блок 73 тактовых импульсов вьшолнен в виде формирователя тактовых импульсов четырех опорных частот. Выходы 81 - сигналов разрещения записи и 82 - сравнения информации блока 8 распределения сигналов присоединены соответственно к управляющим входам 83 и 84 дополнительного счетчика 80 и блока 78 сравнения. Выходы 85, 86 и 87 сигналов управления дешифратора сдвига, управления вторым элементом сложения по модулю два и управления оперативного счетчика блока 8 распределения си1 налов подключены соответственно к входам 88, 89 н 90 блока 21 контроля управления. Выход 85 сигналов управления дешифратора сдвига блока 8 является первым выходом управления устройства Целесообразно, чтобы в устройстве датчик 1 последовательности импульсо содержал через резистор включенный вьтрямитель с накопительным конденсатором, которьш через электронный ключ связан с малоикерционным светоизлучающим прибором. Запасенная энергия, при превышении напряжения на конденсаторе определенной величины, является источником генерации световых импульсов, а частота следования импульсов используется в опред ленных пределах в качестве меры вели чины запирающего напряжения. Полезно, чтобы селектор 5 имел мультиплексоры 91, каждьй из которых содержал бы коммутатор 92 каналов 8x1 например ИС К155КП7, число кот рых определяется количеством контролируемых тиристоров. Входы 93 даннък коммутатора 92 подключены через развязывающие резисторы 94 к соответ ствунщим информационным входам селек тора, подключенным к соответствующим выходам детекторов 4 и к соотвующим выходам 95 трехстабильных элементов 96, например ИС 155ЛН6, содер жащих элемент управления с входом 97 присоединенным к одному из разрядов управляющего входа 6 селектора 5. Другие, входы 98 подключены к другому разряду управляющего входа 6 селектора 5. Адресные входы 99 коммутатора 92 подключены к разрядам адресного управляющего входа 6 селектора 5, авыход 100 коммутатора 92 является информационным выходом селектора 5. В частном случае блок 10 счетчико имеет группу счетчиков 101, каждый из которых .содержит элемент 102.коммутации, например, ИС К155ЛРТ-2И-ИПИ НЕ, первый .вход 103 которого является входом 9 соответствующего разряда блока 10 счетчика. Второй вход 104 элемента 102 коммутации является пер вым разрядом второго управляняцего входа 12 блока 10. Входы третий 105 и четвертый 106 являются соответственно вторым и третьим разрядом второго управляющего входа 12 блока 10. Выход 107 элемента 102 коммутации подключен к первым входам 108 и 109 элементов ПО и 1М И-НЕ блокировки, выходами 112 и 113 подключенных соответственно через синхронный и асинхронный счетчики 114 и 115 и пороговые элементы И 116 и 117 к входам 118 и 119 элементов 110 и 111 И-НЕ блокировки и к первому 120, второму 121 входам элемента 122 сравнения по модулю два. Второй вход 121 элемента сравнения по модулю два является одним из разрядов первого информационного выхода 15. Третий вход 123 элемента 122 сравнения по моду- лю два служит четвертым разрвдом вто-. рого управляющего входа 12 блока 10, а выход 124 является одним изразрядов второго информационного выхода 17 блока 10. Входы 125 и 126 обнуления счетчиков 114 и 115 служат первым управляюн1им входом 1 1 блока 10. Уставка порогового элемента И 116 много больше, чем уставка второго порогового элемента И 117, что обеспечивает условное разделение информации на синхронную и асинхронную. Целесообразно, чтобы блок 8 распределения сигналов содержал распределитель 127, соответствующими входами подключенный к выходам программного счетчпка 128, первым выходом 129 подключенный к установочному входу 130 первого счетчика 131. Второй 132 выход распределителя 127 подключен к первым 133, 134 входам первых элементов 2И-ИЛИ-НЕ 135 и И 136 и служит выходом 62 сигналов запрета блока 8. Выход 137 распределителя 127 присоединен к входу 138 первого ключа 139, а выход 140 подключен к соответствующему разряду выхода 7 блока 8. Выход 141 распределителя 127 присоединен к входам 142 и 143 соответственно элементов И 144 и 145, Выход 146 распределителя 127 под ключен к входу 147 элемента И 144, а выход 148 присоединен к входу 149 триггера 150 и к входу 15 элемента И 152. Выход 153 подключен к входу 154 элемента И 155, второй вход которого подключен к входу 70 блока 8 и к входу 157 первого коммутатора элемента 2И-ЙЛИ-НЕ 135. Выход 158 элемента И 155 подключен к первому 159 входу элемента ИЛИ 1бО, второй 161вход которого подключен к выходу 162элемента И 163. Третий вход 164 элемента ИЛИ 160 присоединен к установочному входу 165 второго счетчнка 166. Выход элемента ШШ 160 подключен к счетному входу 167 программного счетчика 128, установочный вход 168. которого подключен к выходу второго 1.69 элемента ИЛИ. Счетный вход 170 счетчика 166 присоединен к выходу 171 первого ключа 139, к одному из разрядов выхода 45 и выходу 60 блока В, а выход 172 счетчика 166 подключен к выходу 42 блока 8 и входу распределителя 173, выход 174 которого подключен к входу 175 ключа 139, к входу 176 элемента И 163, к входу 177 элемента 178 запрета, второй 179 и третий 180 входы которого присоединены соответственно к выходу 181 ключа 182 к входу 183 элемента И-ИЛИ 184, к входу 183 элемента 186 совпадения и к выходу 143 распределителя 187, к входу 188 ключа 139, к входу 144 элемента И 189. Выход 190 элемента запрета 178 служит .одним из разрядов выхода 45 блока 8. Вход 191 ключа 139 служит входом 64 блока 8, а вход 192 присоединеи к выходу распределителя 193. Вход 194 ключа 139 под ключен к соответст вующим трем адресным выходам 195 распределителя 196, вход которого подключен к выходу 197 первого счетчика 131 и к адресным разрядам выхода 7 блока 8. Адресные выходы 195 распределителя 196, соответствующие рабочим адресам селектор 5, подключены к входам 198 элемента 184, выход которого присоедине к одному из разрядов выхода 27 и выходу 81 сигналов разрешения записи блока 8. Младший адресный выход 199 распределителя 196 подключен к входу 200 триггера 150, к другому разряду выхода 27 и выходу 82 сравнения информации блока 8. Выход 195 последне го рабочего адреса распределителя 196 присоединен к входу 201 элемента совпадения 186, выход 202 которого служит выходом 33 сигнала разрешения перезаписи информации блока 8. Адресный выход 203 распределителя 196 подключен к входу 204 элемента И 163. Адресный выход 205 распредели. теля 196 присоединен к входу 206 элемента И 189, к входу 207 элемента И 152 и входу 208 элемента И 136. . Выход 209 последнего подключен к одному из разрядов выхода 87 блока 8, другие адресные разряды которого подключены к выходу 210 счетчика 211 и к входу распределителя 193, Счетный вход 212 счетчика 211 подключен к выходу 213 элемента И 152, а его 11 414 установочный вход 214 присоединен к выходу коммутатора элемента И-11ПИНЕ 215. Вход 216 элемента И-ИЛИ-НЕ 215 служит входом 74 повторной записи выходной информации блока 8. Второй вход 217 упомянутого элемента 215 служит входом 75 возврата в исходное состояние блока 8, а третий и ;четвертый 218 и 219 входы подключены к выходу 50 сигналов на разрешение вьщачи информации блока 8 и к первому входу 220 элемента И 221. Входы 222 к.223 ключа также подключены к первому выходу триггера 150 и к выходу 50 блока 8. Входы 224 и 225 ключа 182 присоединены соответственно к входам 70 и 71 блока 8 и входам 157 и 226 коммутатора 135 элемента 2И-ИЛИ-НЕ. Вход 227 элемента 2И-ИЛИ-НЕ 135 связан с выходом 50 блока 8, входы 228 и 229 подключены к входу 116 распределителя 196 и выходу 85 блока 8. Выход 230 элемента 2И-ИЛИ-НЕ 135 подключен к счетному входу счетчика 131 и к выходу 13 блока 8. Выход 50 блока связан также с входом 231 элемента И 232, второй вход 233 которого служит входом 72 блока 8, а выход 234 первым разрядом выхода 14 блока 8. Входы 235 и 236 элементов И 145 и 221 соответственно подключены к одному из разрядов адресного выхода 195 распределителя 196, а их выходы 237 и 238 служат соответственно четвертым и третьим разрядами выхода 14 блока 8. Вход 239 распределителя 187 служит адресным входом 36 блока 8, а его вькод 240 подключен к выходу 86 блока 8. Входы 241 и 242 элемента И I44 подключены соответственно к входам 69 и 74 блока 8, а его выход 243 - к входу 244 элемента ИЛИ 169, второй вход 245 которого - подключен к выходу 246 триггера 150. В приведенном варианте блок 21 контроля содержит дешифратор 247 сдвига (.микросхема К155РЕЗ, являкицаяся программируемой ПЗУ; программа дешиф- ратора сдвига на ГЕЗ приведена в таблице, разрешающий вход 248 которого служит вторым входом 88 блока 2J, а выход 249 служит информационным выходом 20 блока 21. Адресньй вход дешифратора сдвига 247 подключен к первому входу 250 элемента 251 сравнения по модулю два, к адресному вхоЬу 252 оперативного счетчика 253 и к адресным разрядам входа 90 блока 21. Управляющий вход 254 элемента 251 сравнения по модулю два служит входом 89 блока 21, второй адресный вход 255 которого подключен к выходу 256 оперативного счетчика 253 и к. соответствующим выходам 35 блока 21, а выходом присоединен к установочному входу 257 оперативного счетчика 253, счетный вход 258 которого является вторым разрядом входа. 90 блока 21. Информационный вход 259 элемента 260 сравнения по модулю два (микросхемы К155ЛРЗ и К155ЛП5 без использования управляющего входа ) служит информационным входом 23 блока 21, второй вход 261 которого служит входом 47 блока 21, а его выход 262 под ключен к выходу 52 блока 21, Коммутатор 38 содержит, например, коммутатор каналов 8х1.ИС К155КП7, ад ресные входы которого служат адресны входом 39 коммутатора, информационный вход подключеный к выходу 37 бло ка 31 памяти и выход присоединенньш к информационному входу блока 43 выбора по большинству. Блок 43 выбора по большинству содержит счетчик 263, установочный вход 264 которого слзгжит одним из разрядов входа 44 блока 43, управляю щим входом 265 подключенного к выходу 266 элемента И 267 соответствующи входы которого служат соответственно другому управляющему разряду входа 44 и информационным входам-блока 43, а соответствующие выходы подключены к соответствующим входам элемента 268 сравнения, выполненном на элемен те ЗИ-ИЛИ-НЕ (на фиг. 5 показан пример выполнения голосования 5 из 8 ), и к позиционному выходу 46 блока 43 Выход 269 элемента 268 сравнения является информационным выходом блока 43.. Полезно, чтобы блок 41 элементов И-ИЛИ-НЕ содержал коммутатор 270, выполненный, например, на элементе 2И-ИПИ-НЕ, первьп 271 вход которого служит информационным входом 48 блока 41, второй и третий 272 и 273 входы служат вторым управлякщим входом 49 блока, а четвертый вход 274 является третьим 51 входом блока 41, выходом подключенньп через элемент НЕ 275 к первым 276 входам элемента И 277, вторые входы 278 ко торого подключены к соответствующим разрядам адресного первого 40 управ 15 ляющего входа блока 41. Выходы 279 элементов И служат выходом 53 блока 41. Блок 41 элементов И-ИЛИ-НЕ и коммутатор 38 обеспечивают и ортогональ ное преобразование информации на выходе блока 31 памяти, а блок 43 выбора по большинству выполняет голосование по элементам кода. Блок 56 вьщачи результатов содержит первый регистр 280, установочный вход 281 и информационный вход 282 которого служат соответственно одним из разрядов управлякмцего входа 58 и информационным входом 54 блока 56, а прямой выход 283 подключен через первый 284 элемент И к одному разряду дополнительного выхода 65 и к информационному входу 285 второго регистра 286, инверсным выходом 287 подключенного через элемент И 288 к другому разряду дополнительного выхода 65. Управляющий вход 289 регистра 286 служит другим разрядным управляющим входом 58 блока 56, выход 290 присоединен через пороговый элемент 291 к первому входу 292 элемента 293 И и к выходу 63 блока 56. Вход 294 элемента 293 И служит входом 61 запрета блока 56, выход 295 подключен к исполнительному элементу 296 (реле). Выход 295 является также выходом цепи контроля устройства. Блок 57 индикации выполнен аналогично блоку 56 вьздачи результата, за исключением того, что нагрузкой второго регистра 286 является дешифратор К 514ИД1 с цифровым индикатором АЛС-324Б.; . . . Работу устройства рассмотрим по следующим этапам. Работа устройства по приему и обработке основного потока информации. Световые импульсы, следующие с . заданной частотой заполнения от дат- . чиков 1 контроля тиристоров 2 по световодам 3, поступают к детекторам 4, преобразующим световые сигналы в электрические. Отсутствие сигнала на выходе детектора 4 свидетельствует о пробое соответствующего тиристора или отказе датчика, световода или детектора. Сигналы от детекторов 4 поступают через- селектор 5 на информационный вход 9 блока 10 счетчиков. В блоке счетчиков фиксируется количество поступивших сигналов. От блока 10 счетчиков через блок 16 элементов ИЛИ информация поступает на вход кодирующего сумматора 22. Коди рующий сумматор 22 предназначен для преобразования информации непозицион ного кода в позиционный (двоичный ) код. Информация в памяти, блока 10 счетчиков постоянно обновляется, бла годаря сигналам, поступакш1им с выход 13 блока 8 распределения сигналов на управляющий вход 11 блока 10 счетчи ков. Синхронность смены информации обеспечивают адресные сигналы, пост пающие с выхода 7 блока 8 распредел теля сигналов на управляющие входы селектора 5. Условно названная асинхронная информация в виде более двух импульсов заданной последовательности записыва ется в счетчике 25. Счетные импульсы поступающие, с выхода 27 блока 8 распределения сигналов на управляющий вход 26 счетчика 25, обеспечивают запоминание многократных показаний кодирующего сумматора 22 ( за время одного цикла опроса всех тиристоров Для обеспечения заданной достоверности принятой информации в блок 10 счетчиков введены кроме условно названных асинхронных счетчиков 115 условно названные Синхронные счетчики 114 с разными уставками пороговых элементов И 117 и 116, подключенные к входам 120 и 121 элементов 122 сравнения по модулю два, которые обе спечивают верную информацию в случае, когда тиристорная ячейка действительно вышла из строя. Синхронные счетчики 114 с пороговым элементом 116 обеспечивают выработку условно названнойсинхронной информации, говорящей 6 тЬм, что тиристорная ячейка выработала заданную последова тельность частоты импульсов, а следовательно, режим работы контролируемого устройства (СТКМ ) достаточно устойчивый. Синхронная информация, поступающая со второго информационного выхода 17 через дополнительный кодирующий сумматор 18 и дополни тельный счетчик 80 на информационный вход 79 блока 78 сравнения, обеспечивает вьфаботку управляющего сигнала --поступающего с выхода 77 блока 78 сравнения на вход 75 блока 8. Этр сигнал обеспечивает обнуление всего устройства в случае превышения уставки блока 78 сравнения. Сигналы, поступающие с выходов 81 и 82 блока 8 на соответствующие управляющие входы 83 и 84 дополнительного счетчика 80 и блока 78 сравнения, обеспечивают запоминание многократных показаний дополнительного кодируклцего сумматора 18 ( за время одного цикла опроса всех тиристоров ). Защитные функции от ложной работы устройства выполняет также блок 29 сравнения и обнуления. Величина уставки в блоке 29 сравнения и обнуления выбирается, из условия глубокой посадки напряжения на контролируемом вентиле. Выработка сигнала, который с выхода 76 блока 29 сравнения и обнуления, поступает на вход 74 блока 8 распределения сигналов, приведет к сбросу памяти всего устройства. Результат опроса, полученный в течение одного цикла, записьгоается в регистр блока 31 памяти по информационному входу 30. Номер регистра определяют сигналы, поступакицие на адресные входы 34 блока 31 памяти, с соответствующего выхода 35 блока 21 контроля управления. Управляющнй вход 32 блока 31 памяти подключенный k выходу 33 блока 8 распределения сигналов обеспечивает передачу сигналов , которые синхронизируют моменты запоминания информации, в регистрах.блока 31 памяти, поступающей со счетчика 25. Число регистров равно числу циклов опроса и выбирается из .условий повьшения достоверности и по мехоустойчивости, снижения вероятности вьиачи ложной информации в аварийных .режимах. Число разрядов выбирается на основании выбранного кода обработки информации. Далее задача состоит в том, чтобы осуществить принцип выбора записанной в регистрах информации по больщинству. В данном устройстве осуществляется голосование по каждому разряду регистров блока 31 памяти. Для этого используется коммутатор 38. Выбранные разряды регистров блока 31 памяти с помощью коммутатора 38 подключаются к блоку 43 выбора по большинству, содержащему, например, счетчик 263 и элемент 268 сравнения; вьпюлненные на элементах ЗИ-ИЛИ-НЕ, управление счетчика 263 осуществляется по mtoie, связывающей управляющий вход 44 блока 43 выбора по большинству с выходом 45 блока 8 распределения сигналов. Выход блока 43 выбора по большинству подключен к информационному входу Ь блока 4I элементов И-ИЛИ-НЕ, кото рый обеспечивает преобразование посл довательного кода в параллельньш и через информационный выход 53 обеспе чивает передачу информации в дублированные каналы блоков 56 и 57. Если отсутствует равенство информации дуб лированных каналов, блок 63 контроля записи разрешает повторение передачи информации от блока 31 памяти, благо даря сигналу, поступающему с выхода блока 63 контроля записи на вход 64 блока 8 распределения сигналов. Многократное повторение будет длиться до тех пор, пока не установи ся однозначное соответствие дублированных каналов в блоках 56 и 57, в противном случае через некоторый момент времени будет вьщан сигнал о неисправности оборудования. Работа устройства по приему и обработке асинхронной контрольной информации. После записи результата опроса всего вентиля в один из регистров блока 31 памяти, младший адрес селек тора 5, формирующийся в блоке 8 распределения сигналов, например, с помощью счетчика 131 поступает с выхода 199 распределителя 196 на вход 200. Сигнал с выхода 246 триггера 150 переводит устройство в режим распределения сигналов. Блок распределения сигналов содержит две подпрограммы, включающие в себя проверку поиска статических отказов типа О и 1, причем условием перехода к выполнени следующей подпрограммы является осве домительный сигнал и, вырабатывающийся дополнительным элементом 67 И-ИЛИ. Осведомительный сигнал с выхода дополнительного элемента 67 И-ИЛИ поступает на пятый вход 69 бло ка 8 .распределения сигналов. Если в устройстве отказ устойчивый, то с выхода 62 блока 8 распределения сигналов поступает сигнал на вход 61 запрета блока 56 вьщачи результата. Имитация контрольной цифры осуществляется в момент теста для под-программы О и 1 благодаря подаче сигнала 1 с выхода 140 распределителя 127 программного счетчика 128, входящего в один из разрядов выхода 7 блока 8. Этот сигнал, например, через трехстабильные элемс;нты 96 поступает на вход 93 селектора 5 и блокирует основную информацию, поступающую с ВТВ. На выходе селектора 5 появляются единичные сигналы для всех команд, воздействующие на управляющие входы 6 селектора 5. Эти сигналы поступают на информационHbte вход 9 блока 10 счетчиков, С выхода 132 распределителя 127 приходит сигнал на вход 133 элемента 2И-Ш1И-НЕ 135. Этот сигнал разрешает прохождение более высокой управляющей частоты, поступающей на вход 70 блока 8 распределителя сигналов, подключенный к соответствующему выходу блока 73 тактовых импульсов. Одновременно тестовьй сигнал запрещает прохождение рабочей частоты, поступающей на вход 71 блока 8 распределения сигналов, подключенного к соответствующему второму выходу блока 73 тактовых импульсов. Управляющие сигналы с выхода 230 элемента 2И-ИЛИ-НЕ 135 воздействуют на счетньпЧ вход счетчика 131 и на выход 13 блока 8 распределения сигналов, обеспечивая смену адресов селектора 5 и соответственно синхронизацию счетчиков 114 и 115 блока 10 счетчиков. По выполнении первой подпрограммы управляющие сигналы снимаются благодаря сигналу последнего адреса, действующему на соответствующем выходе распределителя 196, который, поступая на входы 229 и 228 элемента 2И-Ш1И-НЕ 135 блокирует входные сигналы блока 73 тактовых импульсов. Одновременно тестовый сигнал запрещает прохождение рабочей частоты, поступающей на вход 71 блока 8 распределения сигналов, подключенного к соответству-,, ющему второму выходу блока 73 тактовых импульсов. Управление счетчиком 131, а следовательно, и распределителем 196, вырабатывающим управляющие сигналы для селектора 5, осуществляется сигналом, поступающим с выхода 129 распределителя 127 на установочный вход 130 счетчика 131 блока 8 распределения сигналов. Накопление контрольной информации, поступающей с первого информационного выхода 15 блока 10 счетчиков через блок 16 элементов ИЛИ. и кодирующий сумматор 22 на информационный вход 24 счетчика 25, а затем в блок 31 памяти, осуществляется с помощью сигнало по управляющим входам 26 и 32, подключенньм соответственно к выходам 27 и 33 блока 8 распределения сигналов. Синхронизацию обеспечивают элемент И-ИЛИ 184 и элемент 186 сов-падения. На другой вход 201 элемента 186 совпадения поступает сигнал команды записи в блок 31 памяти, подюгюченный к соответствующему выходу 195 распределителя 196, Ключом 182 управляет тестовый сигнал по входам 222 и 223, обеспечивая прохож дение в тесте более высокой частоты управляющих сигналов, поступающих на входы 224 и 225, Перед переходом устройства в тест сигнал предпоследнего адреса с выхода 205 распределителя 196 через элемент И 152 поступает на счетный вход 212 счетчика 211 и переводит его в следующий адрес Через асинхронную цепь связи, выполненную в виде опера тивного счетчика 253 и элемента 251 сравнения по модулю два,обеспечивается передача адресных сигналов на вхо 34 блока 31 памяти и к блоку 8 распределения сигналов (вход 36), Управ ляющие сигналы, определяющие адрес следующего регистра в блоке 31 памяти также поступают на вход 239 распреде лителя 187. Последний адрес распреде лителя 187 с соответствующего выхода 240 поступает через выход 86 блока 8 распределения сигналов и третий вход 89 блока 21 контроля управления на управляющий вход 254 элемента 251 сравнения по модулю два, выход которого подключен к установочному входу 257 счетчика 253, Такая связь обеспечивает возможность после прохождения подпрограмм теста всякий раз вно возвращаться к исходному, рабочему адресу регистра в блоке 31 памяти. Роль активного управления записью контрольной информации в последующие регистры блока 31 памяти берет тест благодаря сигналам, следующим с выхо да 132 распределителя 127 и соответствующего выхода 205 (предпоследний адрес ) распределителя 196 через элемент И 136, один из разрядов выхода 87 и вход 90 блока 2 контроля управ ления на счетный вход 258 оперативно го счетчика 253, который обеспечивает подклю 1ение следующих регистров в блоке 31 памяти при заполнении их ко трольной информацией, поступающей из счетчика 25. При заполнении последнего регистра в блоке памяти распределитель 187 вырабатывает предпоследний адрес, который с выхода 143 поступает на первьш вход 144 элемента И 189, а на второй вход 206 поступает предпоследний адрес селектора 5 с выхода 205 распределителя 196, Отселектированный сигнал с выхода элемента И 189 поступает на установочньй вход 165 счетчика 166, выходом 172 подключенного к распределителю 173 и через выход 42 блока 8 распределения сигналов к управляющим (адресным J входам 39 и 40 коммутатора 38 и блок 4I элементов И-ИЛИ-НЕ, Одновременно этот сигнал через элемент ИЛИ 160 поступает на счетный вход 164 подпрограммаого счетчика, которьй обеспечивает переход к выполнению следующей команды, связанной с выборкой контрольной информации из блока 31 памяти. Эта команда с выхода 137 распределителя 127 разрешает прохождение управляющего сигнала с выхода распределителя 187 через ключ 139 на счетный вход 170 счетчика 166, Ключ 139 обеспечивает прохождение управляющих сигналов в тесте и в рабочем режиме устройст-ва, благодаря сигналу, поступающему с выхода распределителя 193 на вход 192 ключа 139,. В моменты считывания информации блока 31 памяти происходит сравнение кодовьк комбинаций. Именно с этой целью введены блок 56 элементов ИЛИ 16 и блок 41 элементов И-ИЛИНЕ. Первая кодовая комбинация появляется в момент поступления последнего адресного сигнала с выхода распределителя 196 через выход 85 блока 8 распределения сигналов и вход 88 блока 21 контроля управления на разре1иающий вход 248 дещифратора 247 сдвига, адресные входы которого подключены к входу 90 блока 21 контроля управления, В соответствии с адресными сигналами вырабатывается на выходе 249 дешифратора 247 сдвига код, соответствующий числу незаполненных регистров в блоке 31 памяти в рабо чем режиме, Для дополнительной проверки кодирующего сумматора 22 выходная комбинация .дешифратора 247 сдвига представлена в виде непозиционного кода, Вторая кодовая комбинация ПОЯВЛЯЕТСЯ в момент считывания контрольной информации с блока 31 памяти через (коммутатор 38, блок 43 выбора по большинству (позиционный выход 46J, вход 47 блока 21 контроля управления на входе 261 элемента 260 сравнения по модулю два, которая вырабатывает сигнал совпадения для каждого разряда регистров блока 31 памяти. По окончании команды считывания с блока 31 памяти распределитель 173 заблокируется последним адресным выходом 174 и одновременно дает разрешение по входу 176 элемента И 163 прохождению по его второму входу 204командного сигнала с выхода 203 распределителя 196 через, элемент ИЛИ 160 на вход 167 программного счетчика 128, который вырабаты вает сигнал о переходе к следующей команде - оценке ситуации правильной или ложной работы устройства. Эта ко манда с выхода 146 распределителя 127 программного счетчика 128 поступ ет на второй вход 147 элемента И 144 В случае неисправности устройства, с выхода 243 элемента И 144 сигнал поступает через элемент ИЛИ 169 на .установочный вход 168 программного счетчика 128, в результате программный счетчик вернется в исходное состояние и если неисправность длитель ная (статический отказ 1 или О) .то сигнал с выхода 62 блока 8 распределения сигналов будет сигнализировать об отказе устройства. В случае исправности устройства выполнение подпрограммы 1 заканчивается, и программньй счетчик 128 пе реходит к выполнению второй части подпрограммы - проверке отказов О, благодаря управляющей частоте, поступающей с входа 70 блока .8 распре деления сигналов через вход 156 элемента И 155 и элемент 160 ИЛИ - на счетный вход 167 упомянутого счетчика. Подпрограмма полностью повторяет ся за исключением того, что на управ ляющий вход 6 селектора 5 с первого выхода 7 блока 8 распределения сигна лов поступает сигнал О (на входы 9 трехстабильных элементов 96 и селект ра 5 ). По вьлполнении тестовой программы сигнал с выхода 153 распределителя 127 программного счетчика 128 бло- кирует по входу 154 элемента И 155 . прохождение управляющей частоты с вх 115 24 а 70 блока 8 распределения сигналов. Одновременно с выхода 148 распределителя 127 приходит команда на второй вход 149 триггера 150 и переводит его в рабочий режим. Работа устройства по приему синхронной контрольной информации. Параллельно с поиском неисправностей в устройстве в тесте и выработкой осведомительных сигналов И в подпрограммах теста О и 1 вырабатьюается дополнительный осведомительный сигнал, связанный с исправностью аппаратуры с синхронной информацией. Это достигается тем, что ключ 102 в блоке 10 счетчиков модулирует входной сигнал, поступающий по информационному входу 9, благодаря дополнительным входам 104 и 105, подключенным к второму и первому разрядам управляющего входа 12 блока 10 счетчиков, выход 107 ключа 102 подключен через элементы 111 и 110 И-НЕ блокировки к асинхронному и синхронному счетчикам 115 и 114. Сигналы теста и модулирующей частоты поступают на дополнительные входы 105 и 104 ключа 102 через управлякяций вход 12 блока 10 счетчиков, выход 14 блока 8 распределения сигналов - к второму и первому разрядам шины, присоединенной к выходу 50 блока 8 распределения сигналов и выходу 234 элемента И 232, первый вход 231 которого подключен к выходу 50 блока 8 распределения сигналов, а второй вход 233 через вход 72 блока 8 распределения сигналов 8 - к соответствующему выходу блока 73 тактовых импульсов. Частотный контрольный сигнал, считанный синхронным и асинхронным счетчиками 114 и 115, ограничивается соответственно пороговыми элементами 116 и 117, затем поступает на входы 120 и 121 элемента 122 сравнения по модулю два, выход 124 подключен через второй информационнъй выход I7 блока 10 счетчиков, дополнительный кодирующий сумматор 22, дополнительный счетчик 80 к информационному входу 79 блока 78 сравнения. Для имитации контрольных двух смежных пороговых чисел для первой и второй подпрограмм теста ключ 102 и элемент 122 сравнения по модулю два в блоке 10 счетчиков снабжены управляющими входами. Ш6 и 123, подключенными через третий и четвертый разряды управляющего входа 12 блока 10 счетчиков, выход 14 блока 8 распределения сигналов к соответствующим выходам 238 и 237 элементов И 221 и 145. Накопление синхронной информации происходит в дополнительном блоке счетчика 80, с выхода которого она поступает через информационный вход 79 в блок 78 сравнения. Управление блоков 80 и 78 синхронизовано благодаря сигналам, поступающим на управ ляющие входы 83 и 84 через соответствующие выходы 81 и 82 блока 8 распределения сигналов с выходов элемента И-ИЛИ 184 и выхода 195 распределителя 196 адресных сигналов селектора 5. Для двух смежных Пороговых чисел на выходе 77 блока 78 сравнения появляется дополнительный осведомительный сигнал ( если все исправно ) О и для соответствующих подпрограмм теста. Этот сигнал поступает на вход 75 блока 8 распределения сигналов, подключенного к входу 242 элемента И 144, на входы 42 и 147 которого приходит информация б состоянии подпрограмм -теста с вькодов 141 и 146 распредели теля 127 программного счетчика 128. В случае отказа оборудования с выход 243 элемента И 144 поступит команда через элемент ИЛИ I69 на установочны вход 168 программного счетчика 128. Далее все повторится аналогично, как и для случая отказа в тестовых подпрограммах при работе устройства по приему и обработке асинхронной контрольной информации. Блок 43 выбора по большинству управляется только в момент считывания информации с блока 31 памяти. Это обеспечивается подключением установо ного входа 264 и через элемент 267 И управляющего входом 265 счетчика 263 через соответствующие разряды управл ющего входа 44, блока 43 выбора по большинству, выход 45 блока 8 распре ления сигналов к выходам 171 ключа 139 и 190 элемента 178 запрета. Второй вход 179 элемента 178 запрета по ключен к тактирующему входу 181 втор го ключа 182, а входы 177 и 180 прис единены к выходу 174 и первому выход Соответственно командным адресам рас пределителей 173 и 187 , которые запрещают прохождение сигнала на второ управляющий вход 265 счетчика 263 в 1153 26 блоке 43 выбора по большинству, так как в эти моменты времени происходит запись информации в блок 56 вьщачи результата и блок 57 индикации. Управление сбросом ложной информации происходит только в рабочем режиме благодаря сигналу, поступающему либо с входа 74, либо с входа 75 блока 8 распределения сигналов на входы 216 и 217 элемента И-ИЛИ-НЕ 215, 1шверсныю входами 218 и 219 подключенного к выходу 50, а выходом присоединенного к установочному входу 214 счетчика 211. В результате счетчик 211 обнулится и опрос начнется с первого регистра блока 31 памяти. Разработка вентильных устройств для статических компенсаторов могцюсти является новой областью преобразовательной техники. Данных о новых разработках публикуется мало. В известных из научно-технической литературы зарубежных преобразователях для регулирования реактивной мощности контроль тиристоров вентилей предполагается осуществить также с помощью оптоволоконной системы. Однако технического описания системы контроля в патентной литературе не имеется. Для предотвращения ложного срабатывания контроля тиристоров обеспечивают бесперебойную работу датчи-г ков. С этой целью ограничивают угол регулирования, например, величиной 2 эл. град. Как уже говорилось из-за ошибок фазирования или параметрических отказов элементов фазосдвигающих цепей угол регулирования может быть мень-. ше указанной величины. При этом будет вьадана ложная команда на отключение преобразователя. Оценить вероят ность этого очень трудно. Еще труднее подсчитать убытки из-за ненадежности известных устройств контроля высоковольтных, тиристорных вентилей. Однако можно подсчитать убытки из-за ограничения угла регулирования, например, до 2 эл.град. При этом диапа ЗОИ регулирования уменьшиться на 4%. Ориентировочная экономическая эффективность одного вентиля в установке 160 МВАр составляет не менее 500 тыс. рубл Она снизится на 20 тыс. руб. в то время как при применении предлагаемого изобретения снижения экономической эффективности не будет. 27 .Таким образом, вьшгрыш от нения настоящего изобретения

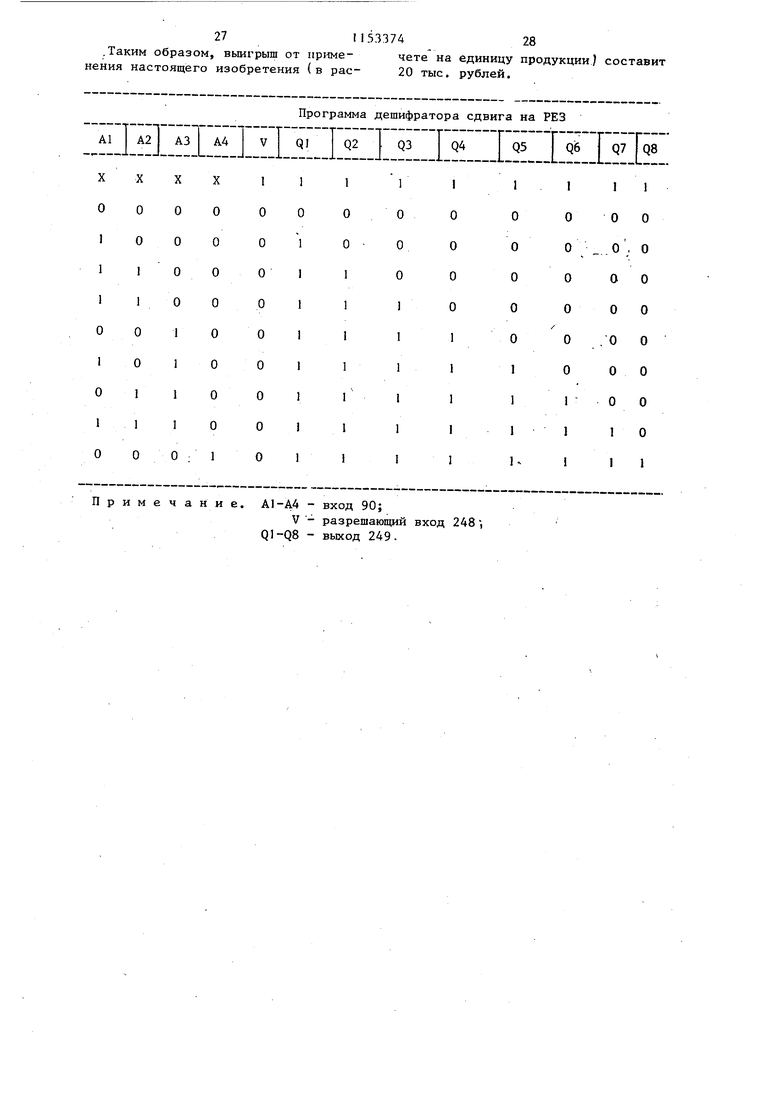

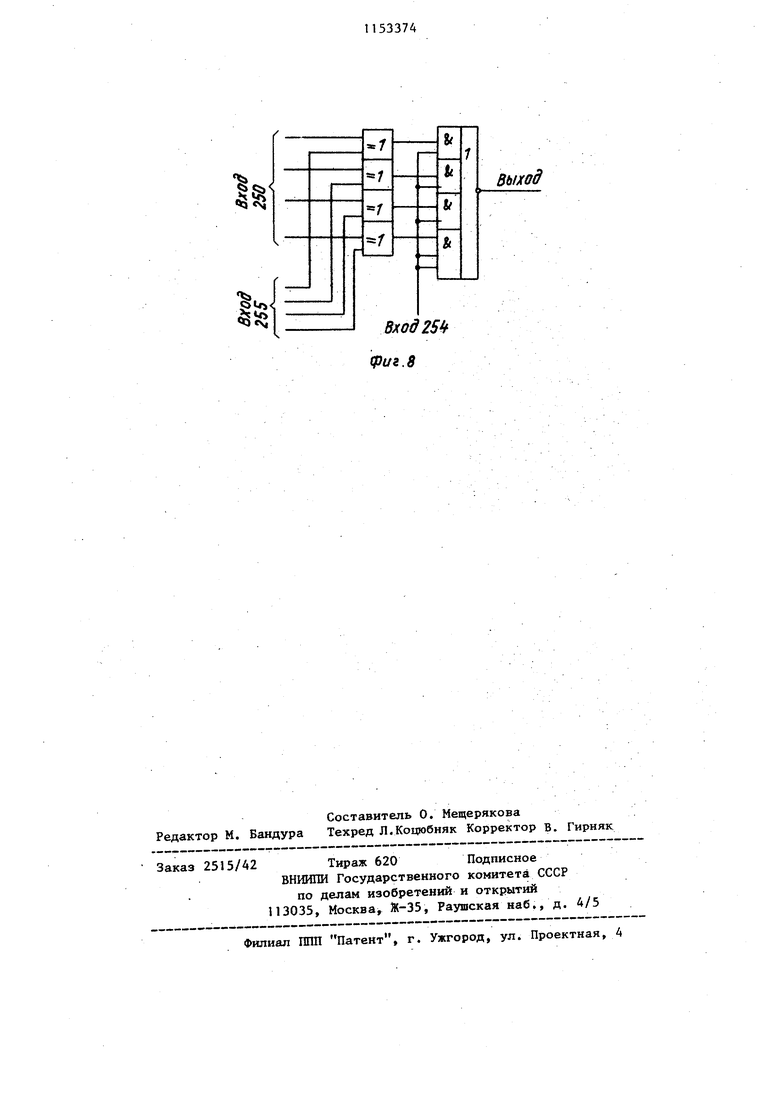

Приме ч ание. А1-А4 - вход 90;

V - разрешающий вход 248i Q1-Q8 - выход 249. приме- чете на единицу продукции) составит (в рас- 20 тыс. рублей. I 15337428

7J.f 7JJ

фиг. 2

(pui.3

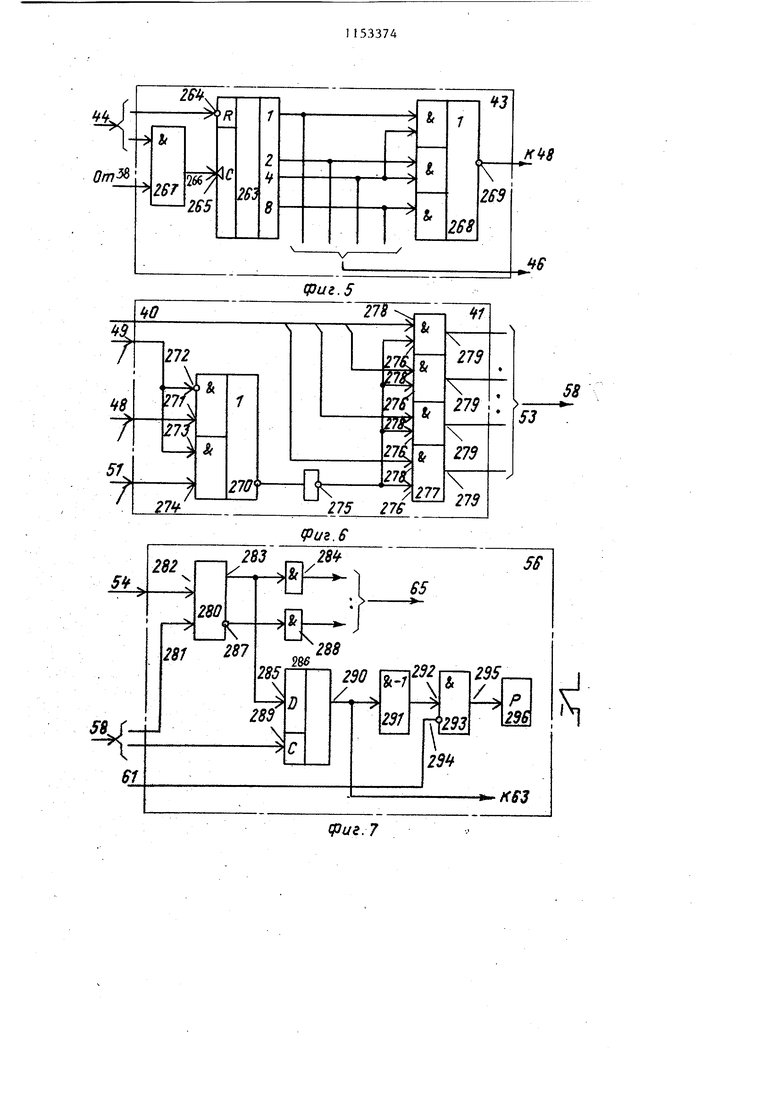

fpua.S

fPuz.6

(риг.

Ir

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Машина для непрерывного литья металлов | 1971 |

|

SU365915A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| СПОСОБ ВЫБОРА ЯЧЕЙКИ И ОКОНЕЧНОЕ УСТРОЙСТВО | 2017 |

|

RU2745326C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство- СССР по заявке № 3339973/24-07 | |||

| кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1985-04-30—Публикация

1983-08-19—Подача