1

Изобретение относится к области цифровой вычислительной техники и может быть использоваио в делителях частоты с любым (целым или дробным) коэффициентом деления.

Известны двоичные сумматоры, выполненные на пороговых элементах, феррит-диодных элементах и феррит-транзисторных ячейках. Однако такие сумматоры по своей схеме, а использование простых статических триггеров в различных перосчетных схемах сопряжено с трудностям и образования импульсов переноса в следующие разряды.

Для упрощения схемы вход-л предлагаемого сумматора соединены с соответствующими входами диодно-транзисторной схемы совпадения и с катодами соответствующих развязывающих диодов, аноды которых объединены и через резистор и первичные обмотки трансформаторов переноса н суммы соединены с коллекторами траизисторов статического триггера. Вторичная обмотка трансформатора переноса подключена ко входам усилителя выходных импульсов переноса. Первый и второй входы статического триггера соединены через последовательно соединенные развязывающие диоды, вторичные обмотки первого и второго трансформаторов су.ммы и встречно включенные вторичные обмотки первого и второго трансформаторов запрета суммы с

эмиттерами транзисторов статического триггера, а в цепь коллектора диодно-транзисторной схемы совпадения включены последовательно дополнительная обмотка трансформатора переноса и первичные обмотки запрещающих трансформаторов суммы.

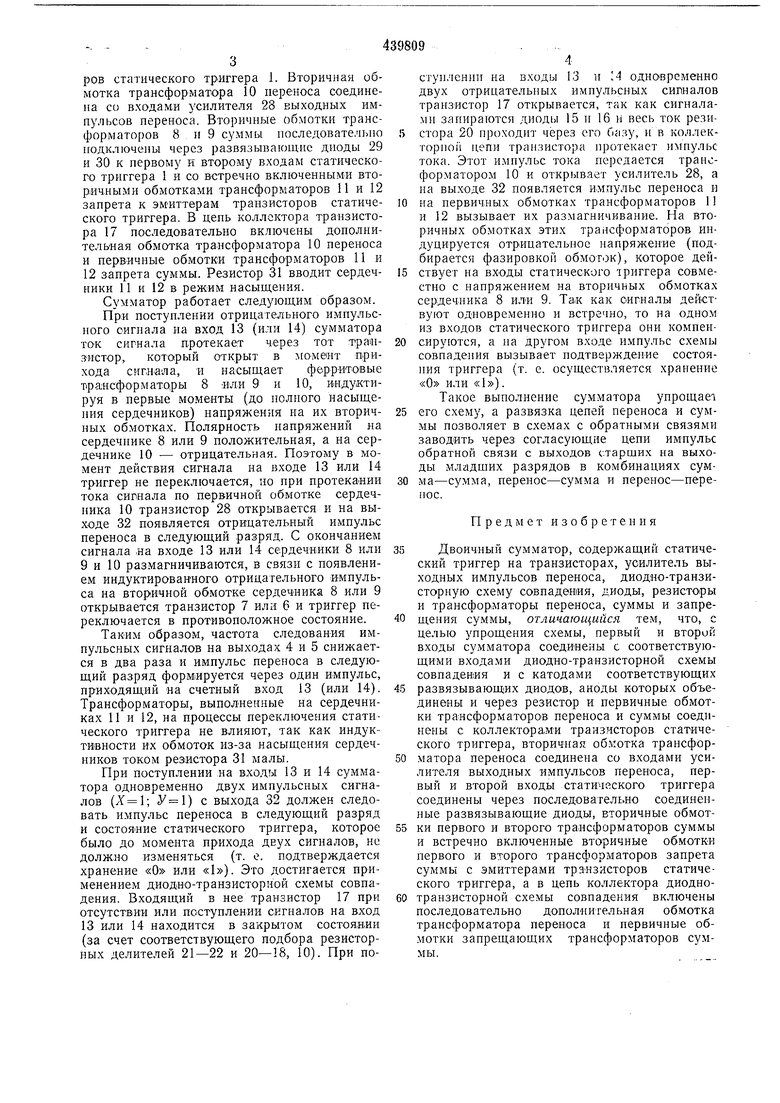

На чертеже представлена блок-схема описываемого сумматора.

Элементом памяти сумматора является 10 статический триггер 1, на входы 2 и 3 которого поступают импульсы сброса для начальной установки. Выходы 4 и 5 коллекторов транзисторов 6 и 7 являются выходами «О и «1, соответственно, по которым можно су15 дить о внутреннем состоянии триггера 1. Сердечники 8 и 9 ферритовых трансформаторов с их обмотками образуют цепь суммы, сердечник 10 - цепь переноса, а сердеч«ики 11 и 12 - цепь запрета суммы. Вход 13 сумма0 тора - счетный вход первого слагаемого X, а вход 14 - второго слагаемого У. Входы 13 и 14 соединены с соответствующими входами диодно-транзисторной схемы совпадения, в которую входят развязывающие диоды 15 и 16, транзистор 17 и резисторы 18-22, и с катодами развязывающих диодов 23 и 24. Аноды диодов 23 и 24 объединены и через резистор 25, первичные обмотки трансформаторов суммы и переноса и развязывающие диоды 0 26 и 27 соединены с коллекторами транзисто3

ров статического триггера 1. Вторичная обмотка трансформатора 10 переноса соединена со входами усилителя 28 выходных импульсов переноса. Вторичные обмотки трансформаторов 8 и 9 суммы последовательно подключены через развязывающие дподы 29 и 30 к первому и второму входам статического триггера 1 и со встречно включенными вторичными обмотками трансформаторов И и 12 запрета к эмИттерам транзисторов статического триггера. В цепь коллектора транзистора 17 последовательно включены дополнительная обмотка трансформатора 10 переноса и первичные обмотки трансформаторов 11 и 12 запрета суммы. Резистор 31 вводит сердечники 11 и 12 в режим насыщения.

Сумматор работает следующим образом. При поступлении отрицательного импульсного сигнала на вход 13 (или 14) сумматора ток сигнала протекает через тот траизИ-стор, который открыт в jroMewT прихода сигнала, и насыщает фьрр-итовые Трансформаторы 8 или 9 и 10, индуктируя в первые моменты (до полного насыщения сердечников) напряжения на их вторичных обмотках. Полярность напряжений на сердечнике 8 или 9 положительная, а на сердечнике 10 - отрицательная. Поэтому в момент действия сигнала на входе 13 или 14 триггер не переключается, но при протекании тока сигнала по первичной обмотке сердечника 10 транзистор 28 открывается и на выходе 32 появляется отрицательный импульс переноса в следующий разряд. С окончанием сигнала ,на входе 13 или 14 сердечники 8 или 9 и 10 размагничиваются, в связи с появлением индуктированного отрицательного импульса на вторичной обмотке сердечника 8 или 9 открывается транзистор 7 или 6 и триггер переключается в противоположное состояние.

Таким образом, частота следования импульсных сигналов на выходах 4 и 5 снижается в два раза и импульс переноса в следующий разряд формируется через один импульс, приходящий на счетный вход 13 (или 14). Трансформаторы, выпол-ненные на сердечниках 11 и 12, на процессы переключения статического триггера не влияют, так как индуктивности их обмоток из-за насыщения сердечников током резистора 31 малы.

При поступлении ,на Вхходул 13 и 14 сумматора одновременно двух импульсных сигналов (Х }; ) с выхода 32 должен следовать импульс переноса в следующий разряд и состояние статического триггера, которое было до момента прихода двух сигналов, не должно изменяться (т. е. подтверждается хранение «О или «1). Это достигается применением диодно-транзисториой схемы совпадения. Входящий в нее транзистор 17 при отсутствии или поступлении сигналов на вход 13 или 14 находится в закрытом состоянии (за счет соответствующего подбора резисторных делителей 21-22 и 20-18, 10). При по4

стунленип на входы 13 и 14 одновременно двух отрицательных импульсных сигналов транзистор 17 открывается, так как сигналами запираются диоды 15 и 16 и весь ток резистора 20 проходит через его базу, ив коллекTopnoii цепи транзистора протекает импульс тока. Этот импульс тока передается трансформатором 10 и открывает усилитель 28, а на выходе 32 появляется и мпульс переноса и

на первичных обмотках трансформаторов 11 и 12 вызывает их размагничивание. Па вторичных обмотках этих трансформаторов индуцируется отр ицательное напряжение (подбирается фазировкои обмоток), которое действует иа входы статического триггера совместно с напряжением на вторичных обмотках сердечника 8 или 9. Та-к как сигналы действуют одновременно и встречно, то на одном из входов статического триггера они компенсируются, а на другом входе импульс схемы совпадения вызывает подтверждение состояния триггера (т. е. осуществляется хранение «О или «1).

Такое выполнение сумматора упрощает;

его схему, а развязка цепей переноса и суммы позволяет в схемах с обратными связями заводить через согласующие цепи импульс обратной связи с выходов старших на выходы младщих разрядов в комбинациях сумма-сумма, перенос-сумма и перенос-перенос.

Предмет изобретения

Двоичный сумматор, содержащий статический триггер на транзисторах, усилитель выходных импульсов переиоса, диодно-транзисторную схему совпадения, диоды, резисторы и трансформаторы переноса, суммы и запрещения суммы, отличающийся тем, что, с целью упрощения схемы, первый и второй входы сумматора соединены с соответствующими входами диодно-транзисторной схемы совпадения и с катодами соответствующих

развязывающих диодов, аноды которых объединены и через резистор и первичные обмотки трансформаторов переноса и суммы соединены с коллекторами транзисторов статического триггера, вторичная обмотка трансформатора переноса соединена со входами усилителя выходных импульсов переноса, первый и второй входы статического триггера соединены через последовательно соединенные развязывающие диоды, вторичные обмотки первого и второго трансформаторов суммы и встречно включенные вторичные обмотки первого и второго трансформаторов запрета суммы с эмиттерами транзисторов статического триггера, а в цепь коллектора диоднотранзисторной схемы совпадения включены последовательно дополнительная обмотка трансформатора переноса и первичные обмотки запрещающих трансформаторов суммы.

25 6 9

23

fj

| название | год | авторы | номер документа |

|---|---|---|---|

| Однотактный реверсивный триггер | 1972 |

|

SU440774A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ВЫСОКОВОЛЬТНЫМ ТИРИСТОРОМ | 2023 |

|

RU2821266C1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Формирователь адресных токов для блоков памяти | 1975 |

|

SU1109074A3 |

| РАСПРЕДЕЛИТЕЛЬ—СЧЕТЧИК | 1972 |

|

SU332577A1 |

| Устройство для направленной защиты от однофазного замыкания на землю в сети с изолированной нейтралью | 1981 |

|

SU1034115A1 |

| Устройство для защиты сборных шин электрических станций и подстанций | 1982 |

|

SU1019539A1 |

| @ -Канальный формирователь импульсов управления тиристорами | 1988 |

|

SU1598011A1 |

| Устройство для регулирования тока возбуждения электрической машины постоянного тока | 1979 |

|

SU884061A1 |

| Формирователь управляющих импульсов | 1990 |

|

SU1714767A1 |

Авторы

Даты

1974-08-15—Публикация

1972-04-28—Подача