1

Однотактный реверсивный триггер может быть использован в ЭВМ, в частности в схемах реверсивных счетчиков, сдвигающих регистрах для преобразования параллельного кода в последовательный, делителях частоты.

Известны реверсивные счетчики, разрядные триггеры которых выполнены на потенциальных схемах НЕ - ИЛИ, на магнитно-транзисторных схемах с применением трансформаторов с сердечниками с ненрямолинейной и прямолинейной петлей гистерезиса (НПГ и ППГ) или на ферротранзисторных триггерах с применением транзисторных ключей и ценочек реверса.

Такие схемы характеризуются сложностью из-за большого количества элементов или отсутствием потенциальных выходов суммы и переноса. Использование простых статических триггеров в различных пересчетных схемах сопряжено с трудностями образования импульсов переноса в следующие разряды.

Известны также триггеры со счетным входом на трансфлюксорах и пересчетное устройство с использованием насыщающегося трансформатора на счетном входе. Однако они пригодны только для простого счета импульсов.

Цель изобретения - упрощение схемы реверсивного триггера с получением сквозного или задержанного импульса переноса в стар2

щий разряд с использованием одного статического триггера с раздельными входами.

Однотактный реверсивный триггер построен на базе такого статического высокочастотного триггера, используемого как элемент памяти, и трансформаторной схемы образования импульсов переноса и суммы, из которых первые после усиления используются для передачи в старшие разряды на входы «Сложение или «Вычитание, а вторые - для изменения состояния статического триггера согласно логике работы.

Это позволяет упростить схему реверсивного триггера, полностью развязав цепи переноса и суммы, и сохранить работоспособность реверсивного триггера вплоть до частот, на которые рассчптан статический триггер.

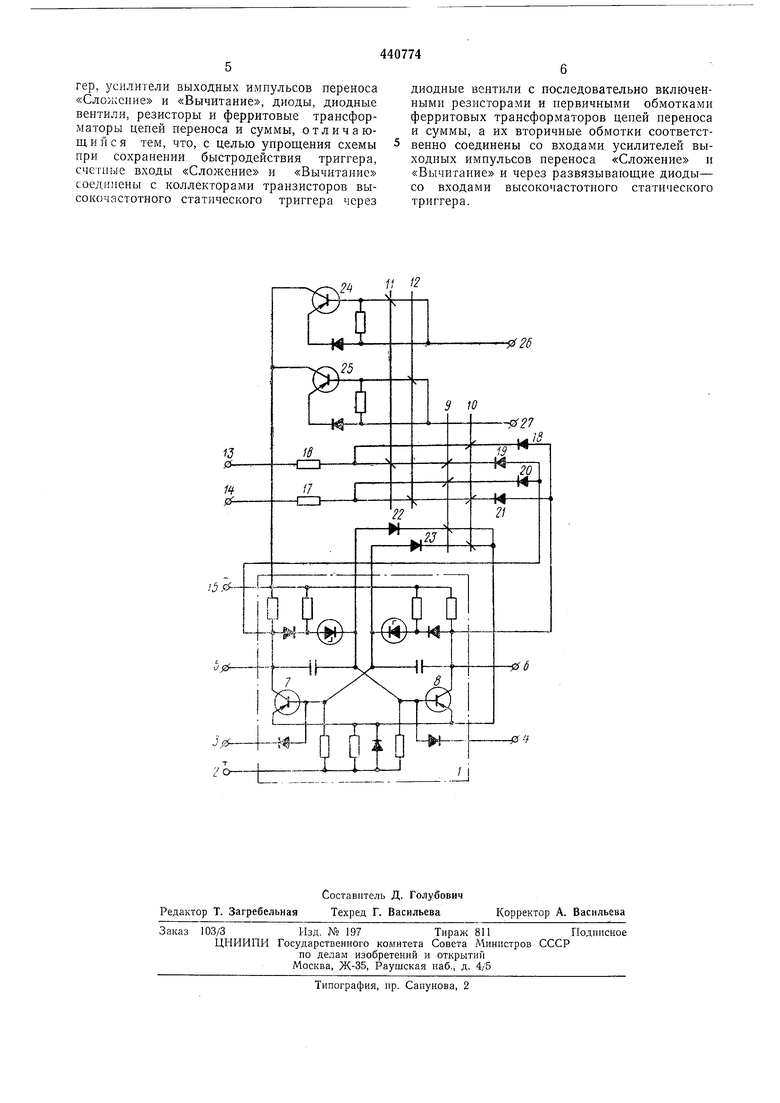

На чертеже изображена схема реверсивного триггера.

Элементом памятп является высокочастотный статический триггер 1, выполпепный по обычной схеме, 2 - положптельная шина источника питания. На входы 3 и 4 триггера поступают импульсы сброса для начальной установки.

Выходы 5 и 6 с коллекторов транзисторов 7 и 8 принимаются за вых. «1 и вых. «О соответственно. Состоянию «О триггера будет соответствовать открытое состояние транзистора 8 и закрытое состояние транзистора 7,

а состоянию «1 - закрытое состояние транзистора 8 иоткрытое транзистора 7.

На чертеже вертикальными линями обозначены сердечники ферритовых трансформаторов, горизонтальными - шины, наклейными- обмотки. Сердечники взяты с НПГ и малых размеров.

Сердечники 9 и 10 с их обмотками образуют iieiib суммы на сердечнике 11 и на сердечнике 12 цепи переноса. Счетный вход импульсов «Сложение - 13, импульсов «Вычитание - 14. Отрицательная шина источника питания - 15.

Входы «Сложение и «Вычитание соответственно соединены с коллекторами транзисторов 7 и 8 статического триггера 1 через резисторы 16, 17, первичные обмотки сердечников 9-12 и диодные вентили 18-21. Вторичные обмотки сердечников 9, 10 через разделительные диоды 22, 23 соединены со входами статического триггера 1, а вторичные обмотки сердечников 11, 12 - со входами транзисторов 24, 25, являюш,ихся усилителями выходных импульсов переноса «Сложение и «Вычитание в следуюш,ий разряд. Выход импульсов переноса «Сложенне - 26, а выход имиульсов «Вычитание - 27.

Если перед началом работы триггер 1 находится в исходном состоянии «О (транзистор 8 открыт, а транзистор 7 закрыт), то цри поступлении отрицательного импульсного сигнала на счетный вход 13 («Сложение) от источников сигнала через резистор 16, первичную обмотку сердечника 10, диодный вентиль

18(диодный вентиль 19 закрыт отрицательным потенциалом с коллектора транзистора

7)и открытый коллекторный переход транзистора 8 протекает ток сигнала. Индуктируемое на вторичной обмотке сердечника 10 напряжение в положительной полярности (подбирается фазировкой обмотки) приложено к минусу диода 23, который остается запертым. Поскольку трансформатор на сердечнике 10 оказывается без нагрузки (в режиме холостого хода), он быстро насыщается, и положительное напряжение на его вторичной обмотке скоро пропадает (примерно через 0,025 мксек). С окончанием импульсного сигнала на входе 13 ток сигнала падает до нуля, сер ечник 10 размагничивается, и индуктированное на его вторичной обмотке отрицательное напряжение через диод 23 открывает транзистор 7 статического триггера 1, которы йперехсдит в состояние «1 (открыт транзистор 7 и закрыт транзистор 8). С приходом следующего импульсного сигнала на вход 3 ток сигнала протекает через резистор 16, первичные обмотки сердечников 11 и 9, диодный вентиль

19(диодный вентиль 18 закрыт отрицательным потенциалом с коллектора транзистора

8)и открытый коллекторный переход транзистора 7. На вторичных обмотках сердечников 11 и 9 индуктируются соответственно отрицательное и положительное напряжения. При этом транзистор 24 открывается, и формируется сквозной импульс переноса в следующий разряд по выходу 26, а так как трансформатор на сердечнике 9, как и в первом случае на сердечнике 10, оказывается в режиме холостого хода (диод 22 закрыт), то полол ительное напряжение на его вторичной обмотке изза насьщения сердечника 9 быстро пропадает. С окончанием второго импульсного сигнала на входе 13 происходит окончание формирования

сквозного импульса переноса по выходу 26 (так как транзистор 24 закрывается вследствие прекращения индуктирования на вторичной обмотке отрицательного импульса из-за пропадания тока в первичной обмотке трансформатора на сердечнике 11), и в результате появления отрицательного импульса на входе транзистора 8 (сердечник 9 размагничивается) вновь происходит переключение статического триггера в состояние «О. Таким образом, получается понижение частоты следования импульсных сигналов на выходах 5 и 6 в два раза и формирование одного сквозного импульса переноса в следующий разряд на каждый четный имнульс, приходящий на счетный вход 13.

Принцип работы реверсивногоо триггера по счетному входу 14 «Вычитание не изменяется. Только формирование одного сквозного импульса переноса в следующий разряд по

выходу 27 «Вычитание происходит на каждый нечетный импульс, приходящий на счетный вход 14.

Схема однотактного реверсивного триггера позволяет в случае необходимости выдавать

импульс переноса в следующий разряд с задержкой, равной длительности самих импульсных сигналов, приходящих на счетные входы 13 или 14, для чего фазировка вторичных обмоток трансформаторов в цепи переноса на

сердечниках 11 и 12 должна быть изменена на 180° посредством переброса начала и конца этих обмоток. При этом режим работы трансформаторов переноса ие будет отличаться от режима работы трансформаторов цени суммы

на сердечниках 9 и 10.

Таким образом, схема реверсивного счетчика на базе обычного высокочастотного статического триггера с применением трансформаторных цепей образования импульсов переноса и суммы позволяет упростить схему триггера и устройств, где он будет применяться, а развязка цепей переноса и суммы легко позволяет в схемах с обратными связями (при работе разрядных триггеров в режиме выдачи импульсов нереноса с задержкой на длительность входных импульсов сигнала) подавать через согласующие цепи импульс обратной связи с выходов старших разрядов на входы с младших в комбинациях: сумма-сумма;

перенос - сумма, перенос - перенос.

Предмет изобретения

Однотактный реверсивный триггер, содержащий высокочастотный статический тригrep, усилители выходных импульсов переноса «Сложение и «Вычитание, диоды, диодные вентили, резисторы и ферритовые трансформаторы цепей переноса и суммы, отличающийся тем, что, с целью упрощения схемы при сохранении быстродействия триггера, счегпые входы «Сложение и «Вычитание соединены с коллекторами транзисторов высокочастотного статического триггера через

диодные вентили с последовательно включенными резисторами и первичными обмотками ферритовых трансформаторов цепей переноса и суммы, а их вторичные обмотки соответственно соединены со входами усилителей выходных импульсов переноса «Сложение и «Вычитание и через развязывающие диоды- со входами высокочастотного статического триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный сумматор | 1972 |

|

SU439809A1 |

| Электронный двоичный реверсивный счетчик | 1960 |

|

SU134487A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU836794A1 |

| Формирователь управляющих импульсов | 1990 |

|

SU1714767A1 |

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| Двоичный реверсивный делитель частоты | 1960 |

|

SU133500A1 |

| ПРОГРАММНОЕ УСТРОЙСТВО | 1970 |

|

SU270346A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК С ПАРАЛЛЕЛЬНЫМ ПЕРЕНОСОМ | 1971 |

|

SU319084A1 |

| Балансный диодно-регенеративный компаратор | 1974 |

|

SU520699A1 |

i f -ll -----i-.i.

/ I

Авторы

Даты

1974-08-25—Публикация

1972-04-28—Подача