1

Изобретение относится к устройствам автоматики и предназначено для использовання в коммутаторах измерительных сигналов систем сбора и обработки данных.

Известны устройства управления коммутатором, содержащие задающие генераторы, распределители, программный блок, переключатель скорости опроса, схемы совпадений, триггер выбора, триггер разрешения н схему ИЛИ, причем выход «I триггера разрешения соединен с одним нз выходов схемы И в цепи выбора высокой частоты (ВЧ) и низкой частоты (ИЧ), выходы которых соединены соответственно с входом за-нуска задающего генератора ВЧ и задающего генератора НЧ, выходы задающих генераторов ВЧ и НЧ через схему ИЛИ подключены к входу запуска распределителя, выходы которого подключены к соответствующим входам программного блока и ключей каналов.

Цель изобретения - уменьшение погрешности коммутации от влияния канала на канал во время переходного процесса.

Для осуществления этой цели в схему устройства введены два триггера памяти н две схемы И-НЕ -: высокой частоты и низкой частоты соответственно, схема НЕ и устройство задержки, при этом выход ВЧ программного блока соединен с входом установкн «I триггера памяти ВЧ, установки «О триггера

2

памяти НЧ н с одним из входов схемы И-НЕ ВЧ, выход НЧ программного блока соединен с входом установки «I триггера памяти НЧ, установкн «О триггера памяти ВЧ и с одним нз входов схемы И-НЕ ВЧ, выход «I триггера памяти ВЧ через схему И-НЕ ВЧ соединен с одним из входов триггера выбора; выход «I трнггера памяти НЧ через схему И-НЕ НЧ соединен с другим входом триггера выбора, у которого один выход подключен к другому входу схемы И в цепи выбора ВЧ, а другой выход - к другому входу схемы И в цепи выбора НЧ н через схему НЕ и устройство задержки - к третьему входу схемы И в цепи выбора ВЧ.

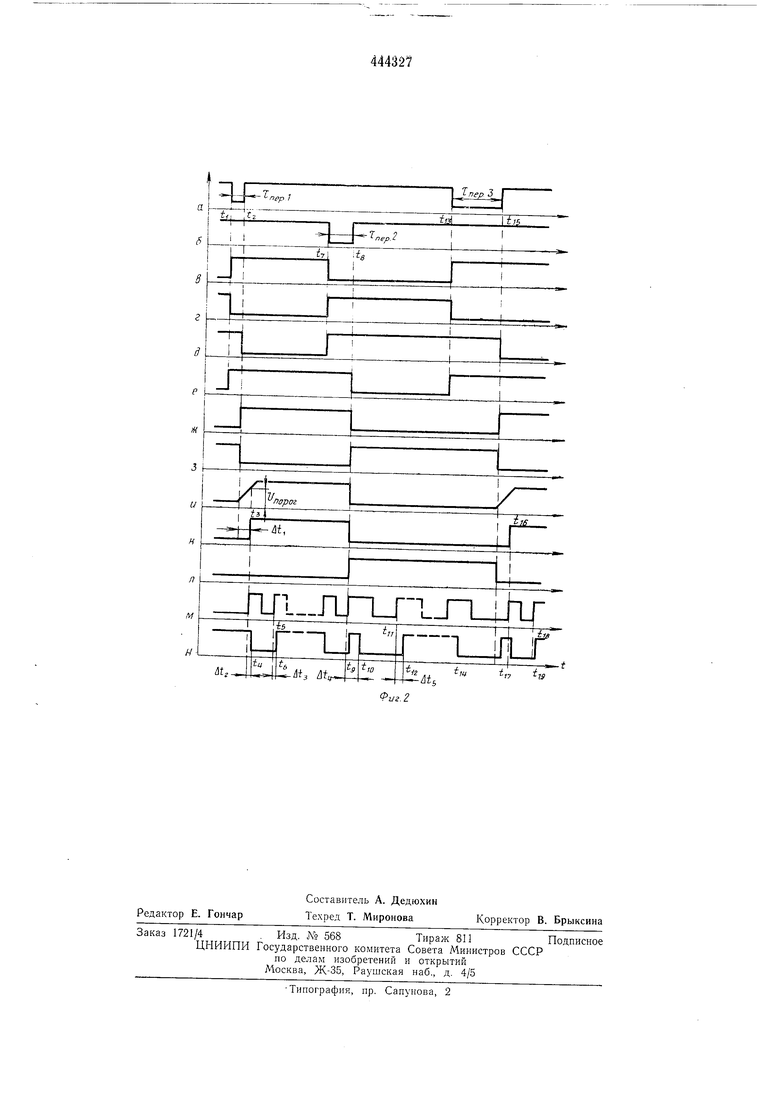

На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг. 2 - его временная диаграмма.

Устройство управления коммутатором содержит программный блок 1, у которого выход ВЧ 1/1 соединен с входом установки «I триггера памяти ВЧ 2, установки «О триггера иамяти НЧ 3 и с одним из входов схемы И-НЕ ВЧ 4, а выход НЧ 1/2 - с входом установки «I триггера памяти НЧ 3, установки «О триггера памяти ВЧ 2 и с одним из входов схемы И-НЕ НЧ 5; триггер выбора 6, у которого на вход установки «I через схему Й-НЕ ВЧ 4 подан сигнал с выхода «I триггера памяти ВЧ 2, на вход установки «О через схему И-НЕ НЧ 5 подан сигнал с выхода «I триггера памяти НЧ 3, выход «I через схему И в цепи выбора соединен с входом запуска задающего генератора ВЧ 8, а выход «О через схему И 9 в цепи выбора соединен с входом запуска задающего генератора НЧ 10; схему НЕ И, у которой вход соедннен с выходом «О триггера выбора 6, а выход - с другим входом И7 в цепи выбора и с одним из выводов конденсатора 12, другой вывод которого заземлен; схему ИЛИ 13, у которой на один из входов поданы тактовые имнульсы с выхода задающего генератора ВЧ 8, а на другой вход - тактовые импульсы с выхода задающего генератора НЧ 10; распределитель 14, у которого вход запуска соединен с выходом схемы 13, а выходы - с соответствующими входами программного блока 1. Кроме того, с выхода 15 распределителя 14 снимаются сигналы управления ключами соответствующих каналов. Работа устройства поясняется временной диаграммой, где цепи формирования импульсов, приведенных на соответствующих эпюрах временной диаграммы обозначены буквами (см. фиг. 1 и 2). Импульс пуска известным способом сформирует в момент ti (см. фиг. 2, а) на одном из выходов программного блока 1 равный себе по длительности импульс переключения скорости опроса. Кроме того, нроизойдет запуск триггера разрешения 16, который после окончания воздействия импульса пуска, в момент t2 снимет со схемы И7 и И9 в цепи выбора запрет на прохождение импульсов переключения скорости опроса. Допустим, что в момент ti импульс переключения длительностью Тпер Сформирован на выходе ВЧ 1/1 программного блока 1. Тогда триггер памяти ВЧ 2 перейдет в состояние «I (см. фиг. 2, в), триггер памяти НЧ 3 - в состояние «О (см. фиг. 2, в), триггер памяти НЧ 3 - в состояние «О (см. фиг. 2, г), ас выхода схемы И-НЕ НЧ 5 прекратится подача импульса установки в «О (см. фиг. 2, е) триггера выбора 6. После окончания воздействия импульса переключения Tnepi в момент t2 (см. фиг. 2, (3) - с выхода схемы И-НЕ ВЧ 4 будет подан импульс установки в «I триггера выбора 6, с выхода «1 которого поступит импульс выбора (см. фиг. 2, ж) на один из входов схемы И 7. Одновременно, с выхода «О триггера выбора 6 прекратится (см. фиг. 2, з) подача сигнала, и на последний вход схемы И7 с выхода схемы НЕ 11 подается (см. фиг. 2, и) импульс разрешения. Когда напряжение на конденсаторе 12 в момент /з (см. фиг. 2, и) достигнет порогового Уцорог срабатывания схемы И7, импульс запуска с задержкой /3 - 2 поступит (см. фиг. 2, /с) на вход задающего генератора ВЧ 8, с выхода которого тактовые импульсы ВЧ через ИЛИ 13 поступят (см. фиг. 2, м) на запуск распределителя 14. С выхода 15 поступят последовательные импульсы управления ключамн соответствующих каналов. Из-за инерционности, обусловленной временем переключения ключа, каждый канал В Ч подключится к общему выходу и отключится с задержкой на и А/з - 4 (см. фиг. 2, н) соответственно. Считаем, что в момент tj (см. фиг. 2, б) импульс переключения Tiiep2 ts, - 7 сформирован на выходе НЧ 1/2 программного блока 1. Тогда триггер памяти НЧ 3 перейдет в состояние «I (см. фиг. 2, г), триггер памяти ВЧ 2 - в состояние «О (см. фиг. 2, б), ас выхода схемы И - НЕ ВЧ 4 прекратится подача импульса установки в «I (см. фиг. 2, д) триггера выбора 6. Носле окончания воздействия импульса переключения Тпер2 Б момент /8 (см. фиг. 2, е) - с выхода схемы И - НЕ НЧ 5 будет подан импульс на вход установки «О триггера выбора 6 (см. фиг. 2, з). В результате прекратится подача импульсов разрешения от схемы НЕ И (см. фиг. 2, а) и с выхода «I триггера выбора 6 (см. фиг. 2, ж) через схему И7 (см. фиг. 2, к) на работу задающего генератора ЬЧ 8 (см. фиг. 2, м), а с выхода схемы И9 поступит (см. фиг. 2, л) импульс пуска задающего генератора НЧ 10, с выхода которого тактовые импульсы НЧ поступят (см. фиг. 2,лг) через ИЛИ 13 на запуск распределителя 14. С выхода 15 начнут поступать импульсы управления ключами соответствующих каналов. На временной диаграмме условно показано, что при формировании тактовых импульсов НЧ происходит управление ключами, время переключения которых значительно больше, чем время переключения ключей, управляемых тактовыми импульсами ВЧ. Каждый ключ каиала НЧ подключится к общему выходу и отключится с задержкой на Д/4 - 4 и - 11 (см. фиг. 2, н) соответственно. Несмотря на то, что предыдущий канал ВЧ из-за задержки э - 4 продолжает оставаться подключенным к общему выходу и после момента /s, когда начинается воздействие импульса управления на ключ последующего канала НЧ, влияние канала на канал не произойдет, так как задержка Если в момент la (см. фиг. 2, а) импульс переключения Тперз 15 - 13 сформирован на выходе ВЧ 1/1 программного блока 1, то триггер памяти ВЧ 2 перейдет в состояние «I (см. фиг. 2, в), триггер памяти НЧ 3 - в состояние «О (см. фиг. 2, г), а с выхода схемы И - НЕ НЧ 5 прекратится подача импульса установки в «О (см. фиг. 2, е) триггера выбора 6. Носле окончания воздействия импульса переключения Тперз в момент 15 (см. фиг. 2, д) с выхода схемы И - НЕ ВЧ 4 будет подан импульс на вход установки «1 триггера выбора 6, с выхода «1 которого импульс выбора (см. фиг. 2, ж) поступит на один из входов схемы И7. Ноступление импульса с выхода «О триггера выбора 6 прекратится (см. фиг. 2, з), поэтому с выхода схемы И9 снимается (см. иг. 2, л) импульс пуска, и задающий генератор 10 перестает (см. фиг. 2, м формировать тактовые импульсы НЧ. Одновременно на выходе схемы НЕ 11 начинает формироваться имнульс разрешения (см. фиг. 2, и). Конденсатор 12 задержит этот импульс иа Аб - Лб (см. фиг. 2, и. Когда напряжение на конденсаторе 12 в момент t (см. фиг. 2, и) достигнет С/порог срабатывания схемы И7, импульс пуска поступит (см. фиг. 2, к) на вход задающего генератора ВЧ 8, с выхода которого тактовые импульсы ВЧ через ИЛИ 13 поступят (см. фиг. 2, м) на запуск распределителя 14. Импульсы управления с выхода 15 поступят на ключи каналов ВЧ. Как видно из временной диаграммы, первый канал ВЧ этой группы подключится к общему выходу в момент in, т. е. тогда, когда за счет введенной задержки Ati ti - (15 предыдущий канал НЧ успевает полностью отключиться. Величина задержки A/i (см. фиг. 2, к) выбирается равной или больщей, чем максимальное время переключения (переходного процесса) применяемых в коммутаторе ключей, поэтому влияния канала на канал практически не будет и погрешность коммутации уменьшится.

Скорость опроса каналов в пределах поддиапазонов ВЧ и НЧ может быть изменена с помощью дополнительного набора времязадающих элементов (например, R и С), переключаемых вручную (блоки 17 и 18 соответственно).

Предмет изобретен и я

Устройство управления коммутатором, содержащее задающие генераторы, распределитель, программный блок, переключатель скорости опроса, схемы совпадений, триггер выбора, триггер разрешения и схему ИЛИ, причем выход «1 триггера разрешения соединен с одним из выходов схемы И в цепп выбора высокой частоты (ВЧ) и пизкой частоты (НЧ), выходы которых соединены соответственно с входом запуска задающего генератора ВЧ п НЧ через схему ИЛИ подключены к входу запуска распределителя, выходы которого подключены к соответствующим входам программного блока п ключей каналов, отличающееся тем, что, с целью уменьщения погрешности коммутации от

влияния канала на канал во время переходного процесса, в его схему введены два триггера памяти и две схемы И - НЕ - высокой частоты (ВЧ) и низкой частоты (НЧ) соответственно, схема НЕ и устройство задержки,

при этом выход ВЧ программного блока соединен с входом установки «1 триггера памяти ВЧ, устаиовки «О триггера памяти НЧ и с одним из входов схемы И - НЕ ВЧ, выход НЧ ирограммного блока соединен со входом

установки «1 триггера памяти НЧ установки «О триггера иамяти ВЧ и с одним из входов схемы И - НЕ ВЧ; выход «1 триггера памяти ВЧ через схему И - НЕ ВЧ соедииен с одним из входов триггера выбора; выход «1

триггера памяти НЧ через схему И - НЕ НЧ соедииеи с другим входом триггера выбора, у которого один выход подключен к другому входу схемы И в цепп выбора ВЧ, а другой выход - к другому входу схемы И в цепи

выбора НЧ и - через схему НЕ и устройство задержки - к третьему входу схемы Н н цепи выбора ВЧ.

№

1

а I-.-П-.- .

Т пер 3

1

L пер J

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ КОММУТАТОРОМ | 1973 |

|

SU387522A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1223248A1 |

| Устройство для дистанционного контроля дуплексных стационарных радиостанций | 1986 |

|

SU1403384A1 |

| Система радиосвязи с однополосной модуляцией сигналов | 1983 |

|

SU1262739A1 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU993468A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ЗАТУХАНИЯ МЕЖДУ АНТЕННАМ | 1995 |

|

RU2127889C1 |

| Устройство для передачи информации | 1979 |

|

SU851447A1 |

| Программное задающее устройство | 1981 |

|

SU991376A1 |

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

Авторы

Даты

1974-09-25—Публикация

1972-09-28—Подача