Изобретение относится к устройствам вычислительной техники, в частности к цифровым системам контроля и обработки информации ,

Известны устройства для оравнения следующих друг за другом чисел, заданных последовательностью импульсов, содержащие два счетных регастра с суммирующими и вычитаю щими счетными входами, линии задер жки, инвертор и логические схемы И, ИЛИ.

В этих устройствах вход регистра с суммирующим входом соединен со входом устройстш через схВ му И, второй вход которой связан через схему IIE с выходом схемы ИЛИ, а вход регистра с вычитающим входом соединен со входом устройства через схему И, второй вход которой связан G выходом охемы ИЛИ, входы которой в свою очередь связаны о выходами разрядов регастра о вшитаюящм входом,

а входы этих разрядов соединены о выходшли ооответствугощих разрядов регистра с суммирующим входом- через схемы И, вторые входа которых черев линию задержки соединены 00 входом сигнала сброса регистра с вычитающим входом.

Наиболее существенным недоотатком этих устройств является большое количество регистров, в. сост. ветственно и малая надежность,так как для получения наибольшего или налменьшего из следуязщих друг за другом чисел необходимо два отдельных устройства,выполняющих соответственные функции.

Целью изобретения -является устранение вышеуказанного недостаТ ка. Для этого в предлагаемом устройстве первые входы третьего и четвертого элементов подключены к первому управляющему входу устройства, второй управляющий вход которого ооединен с пятым зле

ментом IT

, ;при этом вторые всоды

ялементов И, подключены к информационному входу устройства, третьи входы четвертого и пятого элементов И соединены с соответст.вующими выходами первого элемента (мИ, третий вход третьего элемента И подключен к инверсному ВЫХОДУ триггера, вход которого соединен со входом первого элемента задержки, при атом ЕИХОДЫ третьего, четвертого и пятого элементов И через второй элемент ИЖ подключены ко входу сложения второго регистра..

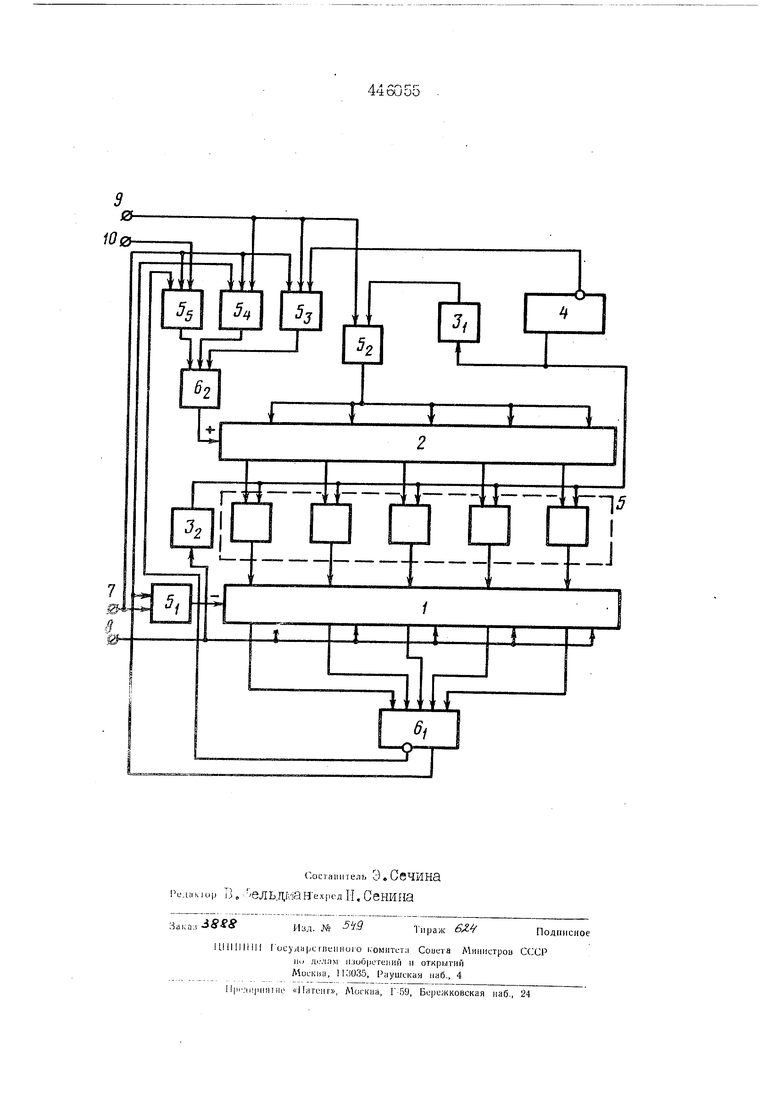

Сущность изобретения поясняв ся чертежом.

устройство для сравнения двоичных чисел содержит регистр I с вычитающим и регистр 2 с суммирующим счетныгл входами, линии задержки 3. триггер 4, логические схемы И ИЛИ 6i2 входы устройства 7-10.

Устройство работает следующим образом.

В исходном состоянии регистры I, 2 свободны и триггер 4 в нулевом состоянии. Если разрешающий потенщ1ал на втором управляющем входе 10 выборки наиоольшего из следующих друг за другом чисел, то перюе число, поступающее на инфощационный вход 7 через схемы И 5 и ИЛИ 6 , запи ывается в регистр 2. Импульс сброса, поступающий после числа на вход 8, переписывает содержимое регистра 2 в регистр I и устанавливает триггер 4 в единичное состояние.

Иглпульсы, соответствующие еле дующеьту чкслу, поступают через схему И 5 на вычитающий вход регистра I и уменьшают его содержюлое.

Если это число окажется больше записываемого в регистрах, то в тот момент, когда в разрядах регастра I будут нули, прекращается поступление импульсов очередности числа на вход регистра I и остальные импульсы числа, соответствующие разности сравниваемых двоичных чисел, поступают на суммирующий вход регистра 2, увеличивая его содержимое. Если второе число меньше первого или равно ему, то содержимое регистра 2 не изменится Поступаш(ий после очередного числа сигнал сброс стирает содержимое регистра I и перезаписывает в этот регистр дюичное число, записанное в регистре 2, которое является

f.

результатом сравнения.

При поступлении на инфордациО нный вход устройства 7 следующего сравниваемого числа операция сравнения производится аналогично и результат сравнения всегда оказыва ется записанным в регистре .1.

В случае, если разрешающий потенциал на первом управляющем входе 9 выборки наименьшего из следующих друг за другом чисел, то первое число, поступающее на информационный вход 7 через схемы И 5з и ИЛИ 6д записывается в регистр 2. Импульс сброса, поступающий пос

ле числа на вход 8, переписывает содержимое регистра 2 в регистр I и устанавливает триггер 4 в единичное состояние и регистр 2 в нулевое.

Импульсы, соответствующие следующему двоичному числу,поступают на входы регистров I и 2 через схемы И 5i и И 5, ИЛИ б соответственно. В случае, если поступающее число равно или больше записанного в регистр I, то в тот момент когда в разрядах регистра I будут нули, прекращается поступление импульсов очередности числа на входы регистров I и 2. Поступающий после очередного числа сигнал сброса стирает содержимое регистра I и перезаписывает в атот регистр двоичное число, записанное в регистре 2, которое является результатом сравнения, и стирает содержимое регистра 2.

Б результате в регистр I будет записано наш,1еньшее из следующих друг за другом чисел.

nPF fvffiT ИЗОБРЕТЕШ1Я

Устройство для сравнения двоичных чисел, содержащее элементы И, ИЛИ, триггер, первый регистр, вход вычитания которого соединен с выходом первого элемента И, первый вход которого подключен к информационному входу устройства, а второй вход - к первому выходу первого элемента ИЛИ, входы которого соединены соответственно с разрядными выходами первого регистра, установочные входы которого соединены с выходами соответствующих элементов И, первые входы которых подключены соответственно к разрядным выходагл второго регистра, а вторые входы - ко входу первого элемента задержки и к выходу

Ьторого элемента задержки, вход которого соединен со входом сброса устройства, выход первого элемента задержки соединен с первш входом второго элемента И, соединенного со входами установки второго регистра, при этом второй вход второго элемента И подключен к первому управляющему входу устройства, о тличающееся тем, что, с целью упрощения устройства, первыз входы третьего и четвертого элементов И подключены к первому управляющему ВХОДУ устройства, второй управляющий вход которого соединен

с ..пятым элементом

атом подклю вторые входы элементов чены к инфорлаиионному входу устройства, третьи входы четвертого и пятого элементов И соединены с соответствующими выходагли первого элемента ИЛИ, третий вход третье го элемента И подключен к инверС ному выходу триггера, вход которого соединен со входом первого элемента задержки, при этом выходы третьего, четвертого и пятого элементов И через второй элемент МИ подключены ко входу сложения второго регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения двоичных чисел | 1975 |

|

SU563674A1 |

| Устройство для сравнения двоичныхчиСЕл | 1979 |

|

SU830376A1 |

| Устройство для сортировки чисел | 1984 |

|

SU1179317A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU942014A1 |

| Устройство для сравнения двоичных чисел | 1979 |

|

SU798818A1 |

| Устройство для определения экстремальных чисел, представленных числоимпульсным кодом | 1989 |

|

SU1665369A1 |

| Устройство для сортировки двоичных чисел | 1984 |

|

SU1182509A1 |

| Устройство для упорядочения массива чисел | 1990 |

|

SU1803909A1 |

| Устройство для сравнения двоичных чисел | 1972 |

|

SU444180A1 |

| Устройство для сравнения чисел | 1978 |

|

SU767753A1 |

Авторы

Даты

1974-10-05—Публикация

1973-04-13—Подача