(54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения двоичных чисел | 1975 |

|

SU603986A2 |

| Устройство для моделирования процессов функционирования подвижных поверочных пунктов | 1990 |

|

SU1746386A2 |

| Устройство задержки импульсов | 1981 |

|

SU974564A2 |

| Устройство для моделирования систем массового обслуживания | 1989 |

|

SU1667100A1 |

| ОБНАРУЖИТЕЛЬ ПЕРЕОТРАЖЕННЫХ СИГНАЛОВ | 1999 |

|

RU2191400C2 |

| Преобразователь временных интервалов в код | 1980 |

|

SU960880A1 |

| Устройство для сравнения чисел | 1978 |

|

SU767753A1 |

| Следящий стохастический интегратор | 1982 |

|

SU1061141A1 |

| Цифровой управляемый преобразователь частоты | 1982 |

|

SU1069146A1 |

| Устройство для моделирования систем массового обслуживания | 1985 |

|

SU1290342A1 |

1

Изобретение относится к автоматике 1 и цифровой вычислительной технике и может быть использовано, например, в системах управления технологическими процессами, системах обегающего контроля для комплекс ного решения задач сравнения чисел, представленных-параллельным способом.,

Известны устройства сравнения для получения отдельных результатов, наибольшего, наименьшего чисел, наибольшей разности. Однако эти устройства не позволяют получить величину наименьшей разности, а также не дают комплексного решения, при котором одновременно определяются все четыре указанные результата цифрового

сравнения.

Цепь изобретения - создание простого устройства с расширенными функциональны-, ми возможностями для сравнения двоичных чисел, представленных параллельным спо- , собом, в котором з§ полный цикл отработки алгоритма его функционирования в качестве рег льтатов сравнения определ-яются экстремальные значения как сравниваемых чисел, так .и их разностей.I

Для достижения этой цели в предлагаемом устройстве сравнения выходы третьей и четвертой схем И через шестую схему ИЛИ связаны с входом первого сум- ктрующего счетчика, а другие входы третьей и четвертой схем И - с выходами пятой и шестой схем И, одним из входов.. связанных с первыми входами двух седь мых схем И и с выходами первого триггера, счетный вход которого связан с вто-, рыми входами обоих седьмых схем И , выходом третьей схемы ИЛИ, первым входом восьмой схемы И и одним из раэдельных входов второго триггера, другие входы пятой и шестой CJSSM И соединены с входом второго суммирующего счетчика и с выходом девятой схемы И, выходы седьмых и восьмой схем И подключены к шинам сброса соответственно реверсивных и первого суммирующего счет- чиков, первый вход девятой схемы И связан с прямым выходом второго тригге-. ра, другой вход которого соединен с входной шиной устройства, а инверсный выходс одним из входов десятой схемы И,

выход которой подключен к входу третьего суммирующего счетчика, а ее другой вход и другой вход девятой схемы И связаны с выходом одиннадцатой схемы И, один из входов которой подключен к выходу второй схемы И, а другой - к другому входу восьмой схемы И, к выходу второй схемы ИЛИ, и с входом четвертого суммирующего счетчика.

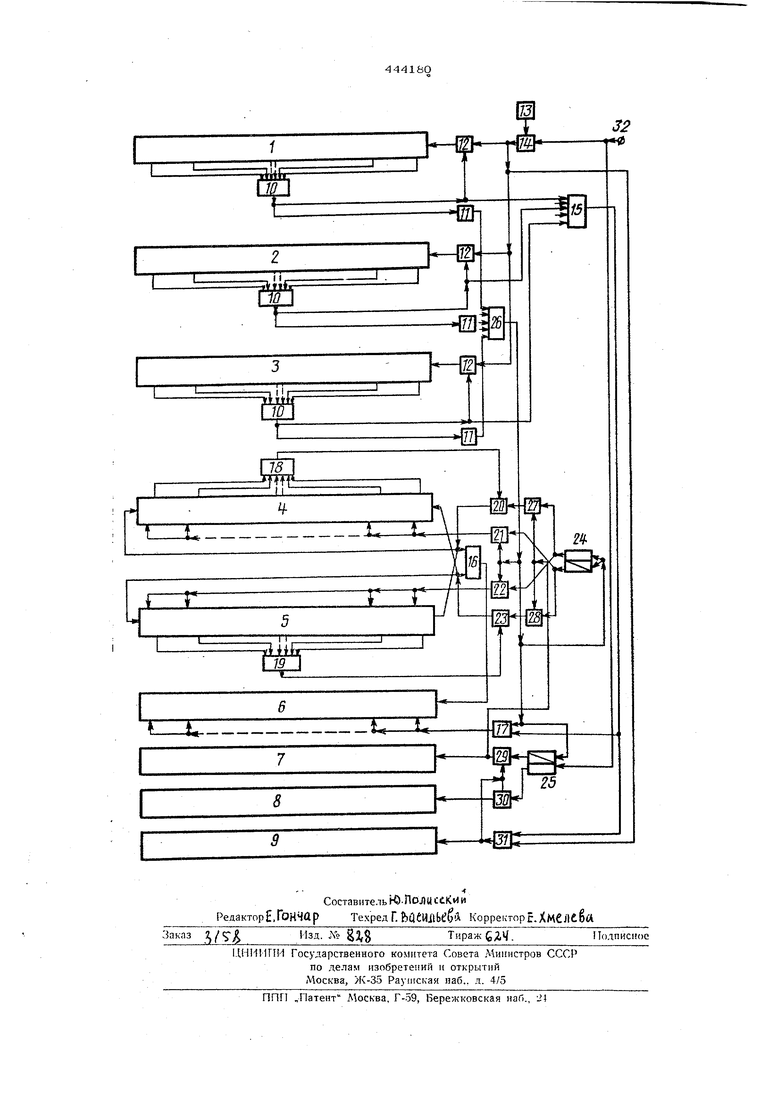

На чертеже показана блок-схема устройства для сравнения двоичных чисел.

Устройство содержит вычитающие счетчики 1, 2 и 3 сравниваемых чисел с вычитающим счетным входом, первый 4 и . второй 5 реверсивные счетчики; первый 6 и второй 7 суммирующие счетчики (минимальной и максимальной разности) с суммирующим счетным входом; третий 8 и Четвертый 9 суммирующие счетчики (на- именьшего и наибольшего чисел) с суммирующим счетным входом; первую схему ИЛИ 1О; дифференцирующие цепи 11; первые схемы И 12, генератор счетных импульсов 13; вторую схему И 14; вторую схему ИЛИ 15; шестую схему ИЛИ 16; восьмую схему И 17; четвертую cxeN-iy РШИ 18; пятую схему ИЛИ 19; третью схему И 20; седьмые схемы И 21, 22; четвертую схему И 23; первый управляющий триггер со счетным входом 24; второй управляющий триггер 25 с раздельными входами; третью схекгу , пятую 27 и шестую 28 схемы И, девятую 29, десятую 30 одиннадцатую 31 схемы И, входную клемму 32 устройства.

Устройство работает следующим образом, В исходном состоянии сравниваемые числа записаны в счетчики 1-3. При этом есть сигналы на выходах каждой из схем 10 и следовательно на вторых входах каждой из схем 12 и на выходе схемы 15, а также на вторых входах схем 17 и 31. Первый н второй управляющие триггеры находятся в состоянии, при котором на их единичных выходах имеются сигналы. В каждом из разрядов счетчиков 4 и 5 записаны единицы.

После поступления на клемму 32 раз- мездающего сигнала импульсы от генератора 13 через схему 14 и схемы 12 поступают на информационные входы счетчиков 1-3, уменьшая их содержимое. Одновременно импульсы через схемы 14 и 31 поступают в счетчик наибольшего ла 9 и подсчитьюаются в нем. С выхода схемы .И 31 импульсы поступают на второй вход схемы И ЗО. Поскольку при I подаче на клемму 32 разрешающий сиг- i нал устанавливает триггер 25 в состоя- ние, при котором появляется сигнал на его нулевом выходе, следовательно, на первом входе схемы И ЗО, импульсы через эту схему проходят в счетчик 8 наименьщего числа и подсчитываются в нем.

После поступления в схему количества импульсов, равного наименьшему числу, содержимое одного (или нескольких) счетчиков 1-3 становится равным нулю, исчезает сигнал с выхода соответствующей схемы 10 и, следовательно, сигнал на втором входе соответствующей схемы ИЛИ 12. Прохождение импульсов в эти счетчики прекращается. Исчезновение сигнала на выI ходе схемы Ю фиксируется соответствующей дифференцирующей цепью 11, импульс с выхода которой через схему ИЛИ 26 перебрасывает триггер 25 в исходное состояние, в результате чего появляется сигнал на первом входе схемы И 29, снимается сигнал с первого входа схемы И ЗО, и подсчет импульсов в счетчике 9 наименьщего числа прекращается. Импульс с выхода схемы ИЛИ 26 перебрасывает триггер 24 в состояние, при котором появляется сигнал на его нулевом выходе, следовательно, на втором входе схемы ИЛИ 27 и первом входе схемы И 22. Импульс с выхода схемы ИЛИ 26 подается на вторые входы схем И 21 и 22, проходит через схему И 22, очищая счетчик 5, в результате чего закрывается схема И 23.

Поскольку появился сигнал на первом входе 29, счетные импульсы с выхода схемы И 31 через схему И 29 начинают поступать на информационный вход счетчика 7 максимальной разности и подсчитываются в нем. Одновременно счетные импульсы с выхода схемы И 29 поступают на первые входы схем И 27 и 28. При появлении сигнала на втором входе схемы И 27 и с выхода схемы ИЛИ 18 на первом входе схемы И 20, импульсы .через схемы И 27 и 20 проходят на суммирующий вход счетчика 5, подсчитываясь в нем. При этом схема И 23 открывается и импульсы поступ юкт на вычитающий вход счетчика 4, уменьшая его содержимое, а также через схему ИЛИ 16 подсчитываются в счетчике 6 минимальной разности.

После того, как число, следующее за наименьшим из сравниваемых чисел, обращается в Нуль, исчезает сигнал с выходаодной из схем ИЛИ 1О и закрывается соответствующая схема И 12, прекращая

поступление вычитающих импульсов в дан- ный счетчик.

j Исчезновение сигнала на выходе схемы ИЛИ 10 фиксируется соответствующей дифференцирующей цепью 11, импульс с выхода которой через схему ИЛИ 26 подтверждает состояние триггера 25 и перебрасывает триггер 24 в противоположное состояние, в результате чего появляются сигналы на первом входе схемы И 21 и втором входе схемы И 28. Импульсы с выхода схемы ИЛИ 26 поступают на второй вход схемы И 21, проходят через схему И 21, очищая счетчик 4, благодаря чему закрывается схема И 2О, и, проходя через схему И 17, очищает -счетчик 6 минимальной разности Импульсы с выхода схемы И 29 через схемы И 28 и 23 ггодсчитываются в реверсивном счетчике 4 и через схему ИЛИ 16 - в суммирующий счетчик 6 и вычитаются из содержимого реверсивного счетчика 5.

Если количество импульсов, поступив- щих в схему с момента времени обращени в нуль одного или нескольких сравниваемых чисел, зафиксированного дифференциру ющей цепью 11, до момента времени обращения в 1гуль следующего одного (или нескольких) сравниваемых чисел, также зафиксированного дифференцирующей цепью 11 (т, е. текущее значение разности

сравниваемых чисел), меньше или равно уменьщаемому, записанному в одном из реверсивных счетчиков 4 или 5 (в данном случае в счетчике 5), то в схеме в этот отрезок времени никаких переключений не происходит. Эта разность, как наименьшая из всех предыдущих, окажется записанной в суммирующем счетчике 6. Если же очередная текущая разность больще уменьщаемого, то момент времени, при котором выполняется равенство количества импульсов, поступивших в схему, предыдущему значению разности, содержимое регистра уменьшаемого (в данном случае счетчика 5) станет равным нулю, схема И 14 закроется, и дальнейшее поступление: иктульсов в устройство прекратится. Предыдущее значение разности в качестве наименьшего из всех сравниваемых к этому моменту будет восстановлено в схеме И 22 и запомнено.

После того, как обратится в нуль наибольшее из всех чисел, исчезнет сигнал с выхода схемы : ИЛИ 15, т., е. сигнал на вторых входах схГем И 31 и 17, поступление импульсов в суммирующ.ие счетчики 9.и 7 прекратится, а импульс с выхода схемы ИЛИ 26 не сбросит содержимое счетчика 6 в нуль. Таким образом, в счетчиках 9 и 8 записаны наибольщее и наименьшее из сравниваемых

и 6 - максимальная

чисел, в счетчиках 7 разность чисел.

Предмет изобретения

Устройство для сравнения двоичных чисел, содержащее Ц двоичных вычитающих счетчиков, выходы каждого из которых через схемы ИЛИ связаны с одним из входов первых схем И , другими входами связанных с выходом второй схемы И, подключенной одним из входов к выходу генератора, и с входами второй схемы ИЛИ, а через дифференцирующие це|пи с входами третьей схемы ИЛИ, выходы первых схем И соединены с информационными входами соответствующих вычитающих счетчиков, два реверсивных счетчика, выходы которых связаны с входами четвертой и пятой схем ИЛИ входы сложения - с выходами третьей и четвертой схем И, одни из входов которых соединены с выходами пятой и четвертой схем ИЛИ соответственно, выход третьей схемы И кроме того подключен к входу вычитания второго реверсивного счетчика, а выход четвертой схемы И - к входу вычитания первого реверсивного счетчика, четыре суммирующих счетчика, триггеры, схемы И, ИЛИ, отличающее- с я тем, что, с целью расширения функциональных возможностей, в нем выходы третьей и четвертой схем И через шестую схему ИЛИ связаны с входом первого суммирующего счетчика, а другие входы третьей и четвертой схем И - с выходами пятой и щестой схем И, одним и

входов, связанных с первыми входами двух седьмых схем И и с выходами первого триггера, счетный вход которого связан с вторыми входами обоих седьмых схем И, выходом третьей схемы ИЛИ первым входом восьмой схемы И и одним из раздельных входов второго триггера, другие входы пятой и шестой схем И соединены с входом второго суммирующего счетчика и с выходом девятой схемы И, выходы седьмых и восьмой схем И подключены, к шинам сброса соответственно реверсивных и первого суммирующего счетчиков, первый вход девятой схемы И связан с прямым выхо- дом второго триггера, другой вход которого соединен с входной шиной устройства, а инверсивный выход - с одним из входов десятой схемы И, выход которой подключен к входу третьего суммирующего счетчика, а ее другой вход и другой вход девятой схемы И связаны с выхо7 дом одиннадцатой схемы И, один из входов которой подключен к выходу второй схемы И, а другой - к другому входу 444180 Ь Iвосьмой схемы И, к выходу второй схе-; мы ИЛИ , и с входом четвертого суммирующего счетчика.

т

S2

Авторы

Даты

1974-09-25—Публикация

1972-08-11—Подача