(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЧЕРЕДСВАНИЯ И ОБРЬША ФАЗ

I

Изобретение СУГНОСИТСЯ к области автоматизации электроэнергетических систем и может быть использовано при синхронизации генераторов и при подключении трехфазных потребителей в электроэнергетических системах различного назначения и, в частности, в судовых электроэнергетических системах.

Известны устройства аналогичного назначения, содержащие входной трансформатор первичные обмотки которого подключены: к фазам контролируемой сети, а вторичные ко входам формирователей прямоугольных импульсов, симметричный триггер, схемы совпадения, интегрирующие элементы и инверторы.

Однако подобные устройства не обеспечивают высокой точности: дают ложные сигналы при обрыве одной из фаз либо не позволяют контролировать обрьш фазы непосредственно перед подключением потребителей или перед синхронизацией.

Для повышения надежности контроля выI ходы формирователей прямоугольных импульсов подключены соответственно к трехГвходовым схемам совпадения, вторые входы которых соединены вместе и подключены к одному из входов симметричного триггера и к выходу двухвходовой схемы совпадения входы которой подключены к выходам формирователей прямоугольных; импульсов, :связанным также через два инвертора со входами второй двухвходовой схемы совпадения, подключенной по выходу ко второму входу симметричного триггера. Один из выходов последнего подключен ко входам трехвходовых схем ссжпадения, выходы которых в свою очередь, через интегрирующие элементы подключены к соответствующим входам инверторов и одновременно ко входрм

схемы совпадения.

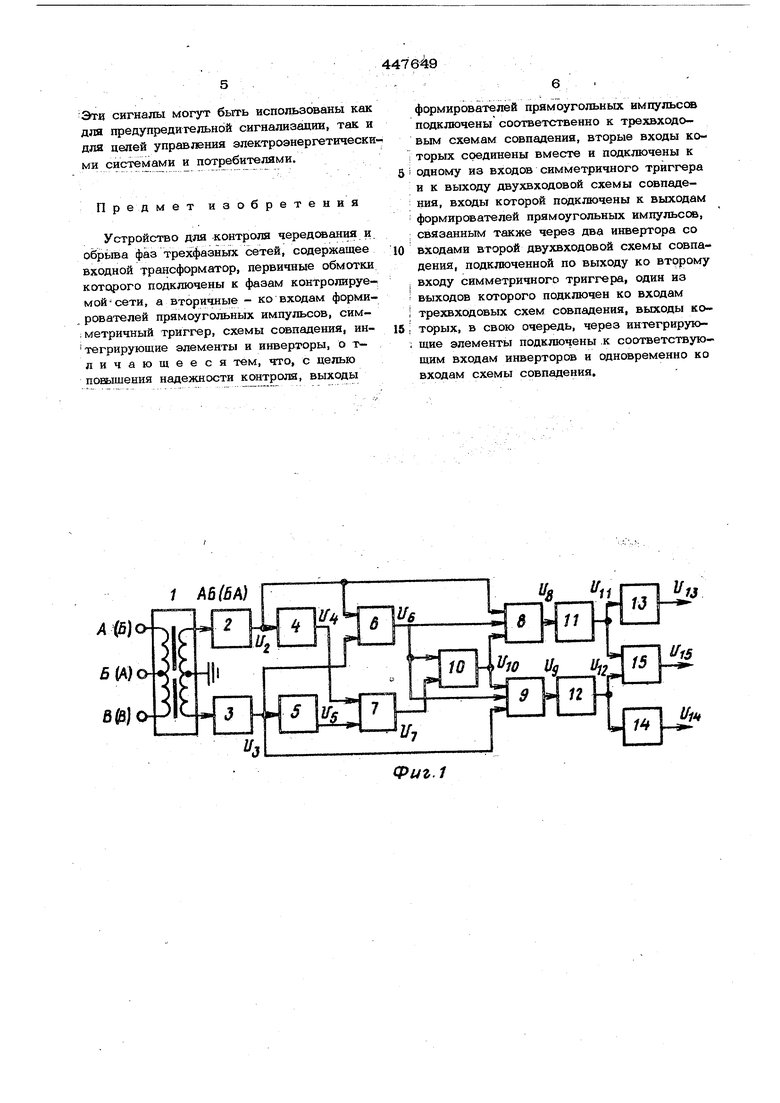

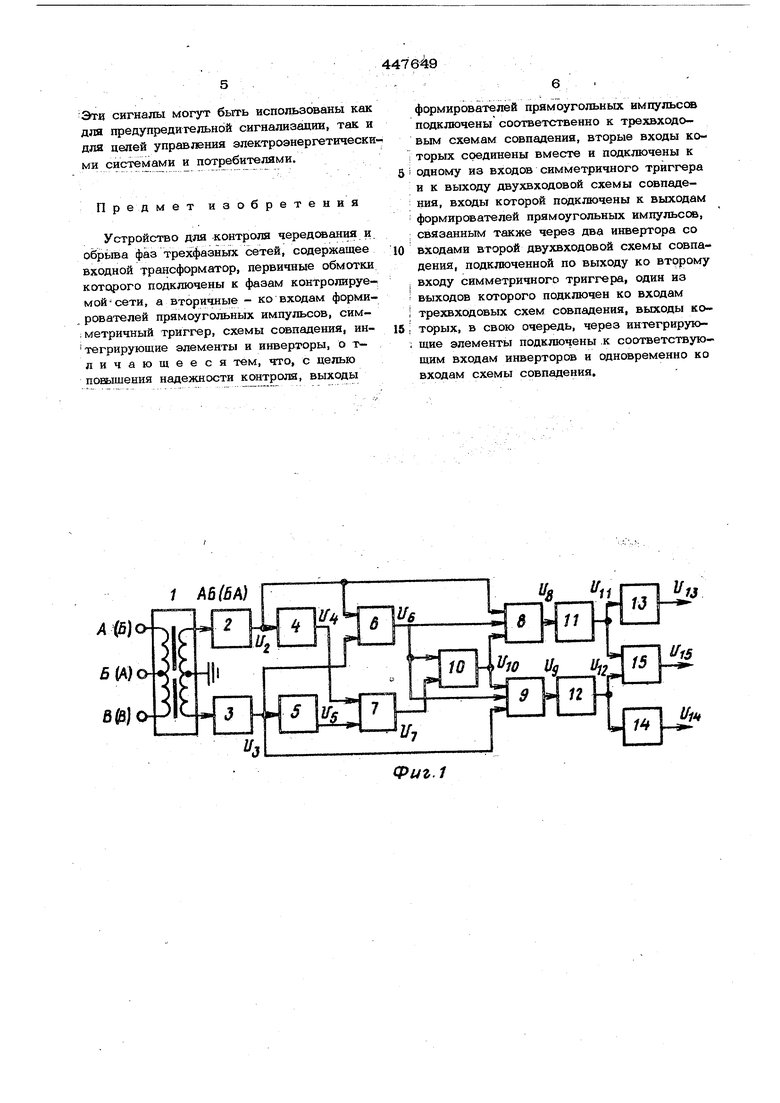

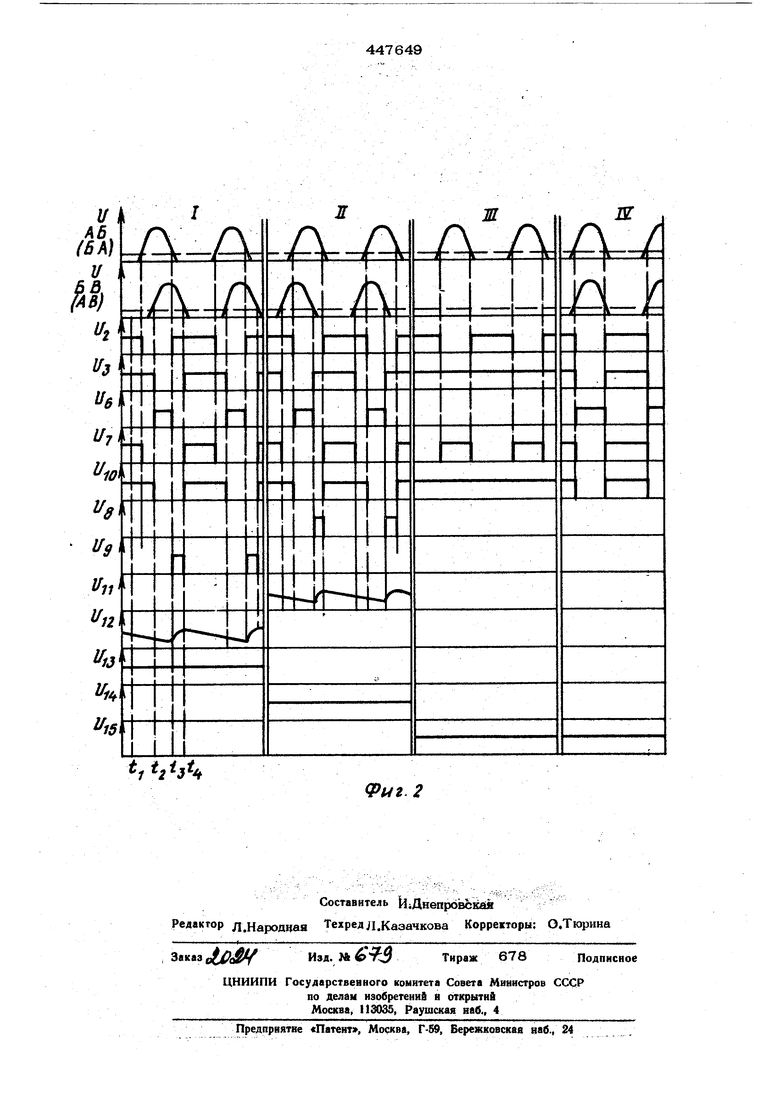

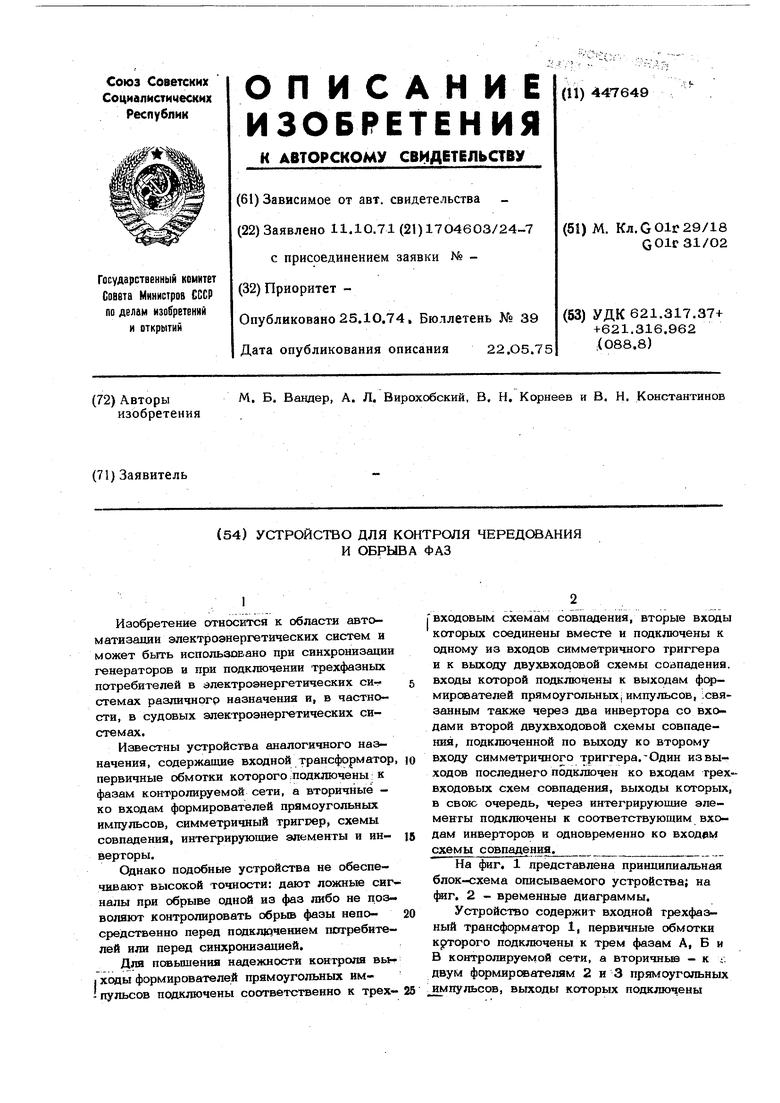

На фиг. 1 представлена принципиальная блок-схема описываемого устройства; на фиг. 2 - временные диаграммы.

Устройство содержит входной трехфазный трансформатор 1, первичные обмотки которого подключены к трем фазам А, Б и В контролируемой сети, а вторичные - к ;. двум формирсжателям 2 и 3 прямоугольных

импульсов, выходы которых подключены сосугъетствёнио к инверторам 4 и 5, а так же к двухБходовым схемам совпадения 6/7 If т рехвходс®ым - 8 и 9. Инверторы 4 и 5 подключены к другим входам двухвходовых схем совпадения 6 и 7, выходы которых соединены с раадель ными входами триггера Ю, Причем выход схемы совпадения 6 подключен еще и ко вторым входам трехвходовых схем совпаде НИИ 8 и 9, третьи входы которых соедине;ны с одним из выходов триггера Ю. Выхо ды трехвходовых схем совпадения 8 и 9 через интегрирующие элементы 11 и 12 подключены соответственно к выходным инверторам 13, 14 и одновременно к двухвходоврй схеме совпадения 15. Выходные напряжения элементов 2-15 обозначены на фиг. 1 и 2 с соответственно, (АВ) - напряжения формирователей 2 и 3. При включении устройства в сеть возможны четыре варианта работы схемы: первый, когда напряжение U . с (т подаваемое на вход формирователя 2 прямоугольных импульсов, опережает напряжение У„ , „, подаваемое на вход формирова теда 3 прямоугольных импульсов , что усповно соответствует прямо1у1у порядку чередования фаз; второй вариант, соответствующий обратному порядку, чередования фаз, когда напряжение Up|D(до) опережает напряжение ЬдБ(БА) ° на фаза А или В, и четвертый - оборвана фаза Б. Каждому варианту соответствует временная диаграмма на фиг. 2, . . Пусть включение устройства произойдет (диаграмма 1 на фиг, в момент времени t.. 2), тогда на выходе формирователей 2 и 3 прямоугольных импульсов появятся сигна1& и и Uo- Эти сигналы инвертируются эпеJ2. 3 ,. .. -- - ментами 4 и 5 и подаются на вход двухвходовой схемы совпадения 7, на выходе ксугорой появляется сигнал U, устанавлива ющий симметричный триггер 10 в положение запрета. На входы трехвходовых схем совпадения 8 и 9 подается сигнал запрета J lp-„„..... ....: : в момент времени t двухвходовой схемы совпадения 6 появляется сигнал Ug совпадения сигналов который устанавливает симметричный триг гер 10 в положение, при котором с трех{входовых схем совподенвя В и 9 снимается сигнал запрета У, ,,, НО одновременно появХО . ляется сигнал запрета У,,. После этого в момент времени to со схем 8 и 9 снимается сигнал запрета Ug. но одновременно на входе трехв одовой схемы совпадения 8 появляется сигнал запрета 2 а на входе трехвходовой схемы совпадения 9 все три сигнала запрета схгсутству ют, Б результате на выходе схемы 9 появляется сигнал UQ, который через интегрирующее звено 1О воздействует на входы схем 14 и 15 и на их выходе напряжение отсутствует. Одновременно появляется сиг нал U о на выходе инвертора 13, соответствующий прямому порядку чередования фаз, Бо втором варианте (временная диаграм- ма на фиг. 2) схема работает аналогично за исключением момента времени 1г„, когда (сигнал появляется на выходе трехвходовой схемы совпадения 8. Б результате выходной сигнал Уч д появится на выходе инвертора 14, что соответствует обратному порядку чередования фаз. При обрьше фазы А или Б (временная j диаграмма JE на фиг, 2) одноиз напряжений АБ(БА) ББ(АБ) , в результате чего сигнал и„двухвходовой схемы ,совпадения 7 устанавливает триггер 10 в положение запрета и, следовательно, сигна- на выходе схем совпадения 8 -пы .и 9 отсутствуют. Сработает схема совпаде- ния 15, на выходе которой появится сигнал У , что соответствует обрьту фазы. При обрьше фазы Б входные напряжения (БА) Чж(АБ) временная диаграмма 1У на фиг. 2) оказьтаются в фазе и, таким образом, на входы схемы совпадения § и 9 будут поочередно приходить сигналы запрета У.. Q и и оттриггера 10 и от схемы совпадения 6, в результате чего сигналы Uo п, будут отсутствовать, а на выходе о у схемы совпадения 15 появится сигнал также соответствующий обрыву фазы. Таким) образом, схема сигнализирует о псфядке чередования фаз и об обрыве одной ,из фаз, причем, в каждом случае выходной Iсигнал появляется на одном из трех рыходных канале®, обозначенных Прямой порядок, Обрыв фазы и Обратный порядок.

Этт сигналы могут быть использованы как для предупредительной сигнализации, так и для цепей управления электроэнергетическими системами и потребителями.

П р е д мет изобретении

Устройство для контроля чередования и обрьта фаз трехфазных сетей, содержащее входной трансформатор, первичные обмотки которого подключены к фазам контролируемой сети, а вторичные - ко входам формирователей прямоугольных импульсов, симI метричный триггер, схемы совпадения, интегрирующие элементы и инверторы, о тличающееся тем, что, с целью повышения надежности контроля, выходы

6,

формирователей прямоугольных импульсов подключены соответственно к трехвходовым схемам совпадения, вторые входы которых соединены вместе и подключены к одному из входов симметричного триггера и к выходу двухвходовой схемы совпадения, входы которой подключены к выходам формирователей прямоугольных импульсе, связанным также через два инвертора со входами второй двухвходовой схемы совпадения, подключенной по выходу ко второму входу симметричного триггера, один из выходов которого подключен ко входам трехвходовых схем совпадения, выходы которых, в свою очередь, через интегрирующие элементы подключены .к соответствующим входам инверторов и одновременно ко входам схемы совпадения.

и

fj

тз

Риг.2

Авторы

Даты

1974-10-25—Публикация

1971-10-11—Подача