Изобретение относится к области контроля многофазных сетей переменного тока и может быть использовано в любой отрасли промышленности в системах электропитания, управления и защиты механизмов и устройств, критических к неправильному чередованию или пропаданию фаз многофазной сети.

Целью изобретения является расширение функциональных возможностей устройства посредством локализации отказа сети выработкой трех допоянительных сигналов неисправности, индицирующих раздельно обрыв двух или трех фаз, обрыв одной фазы и нарушение чередования фаз.

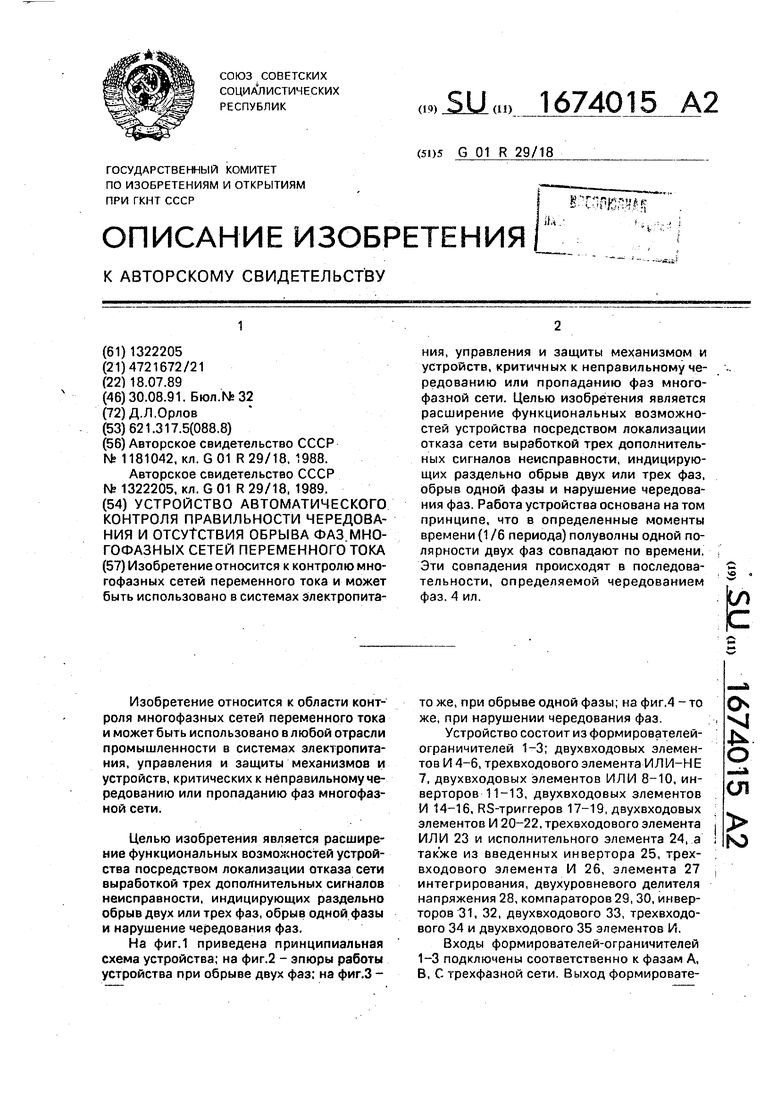

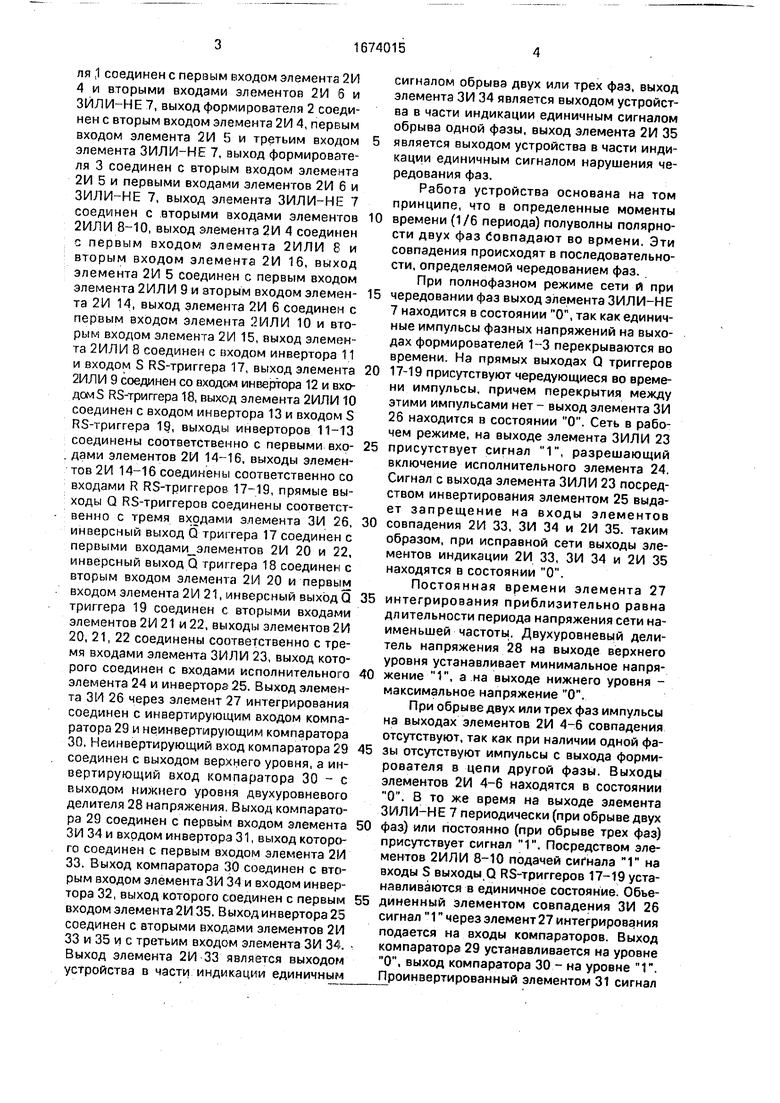

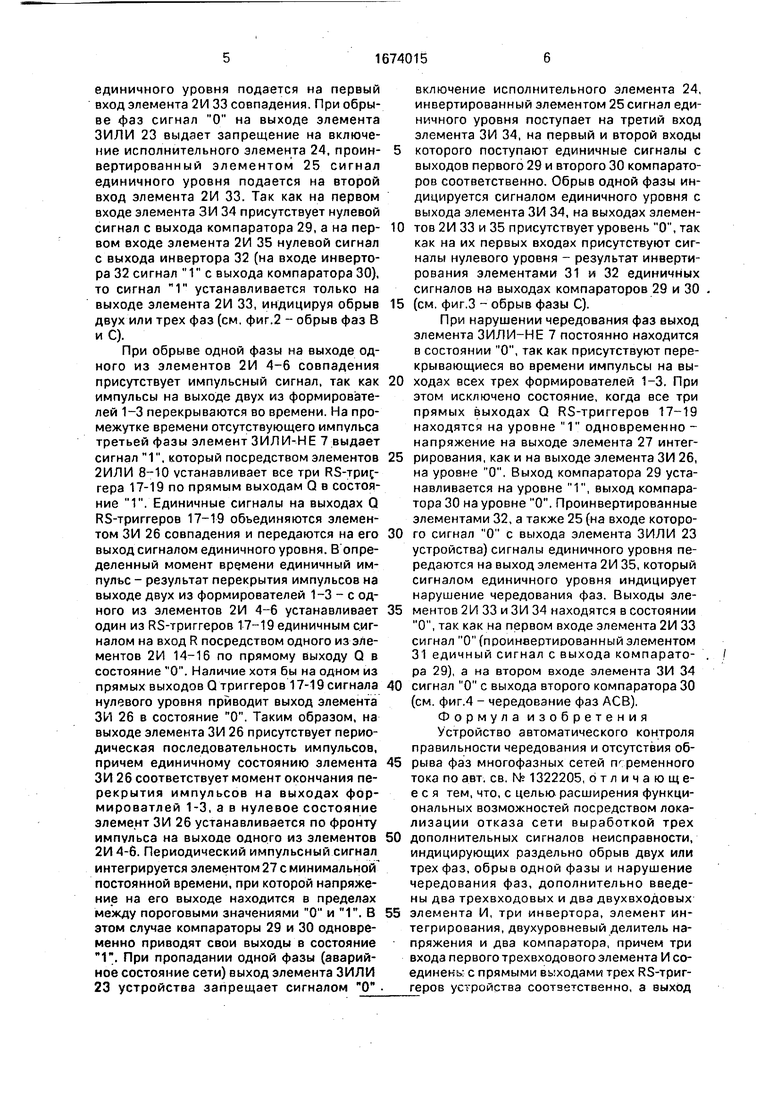

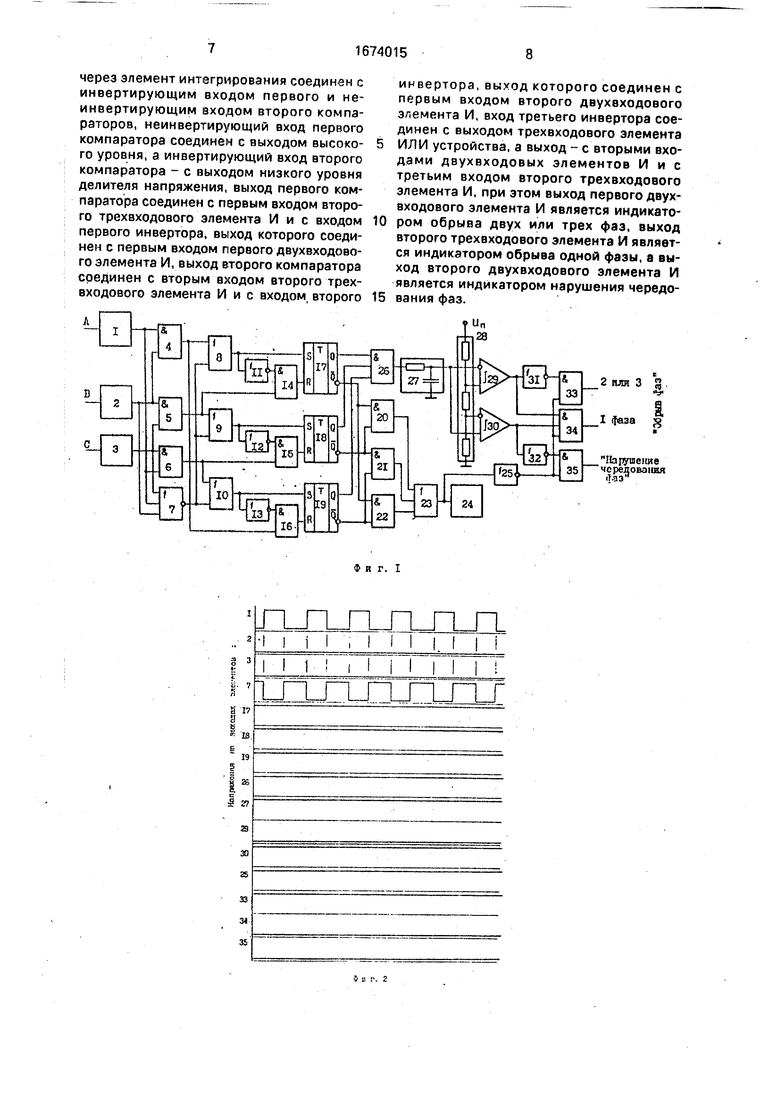

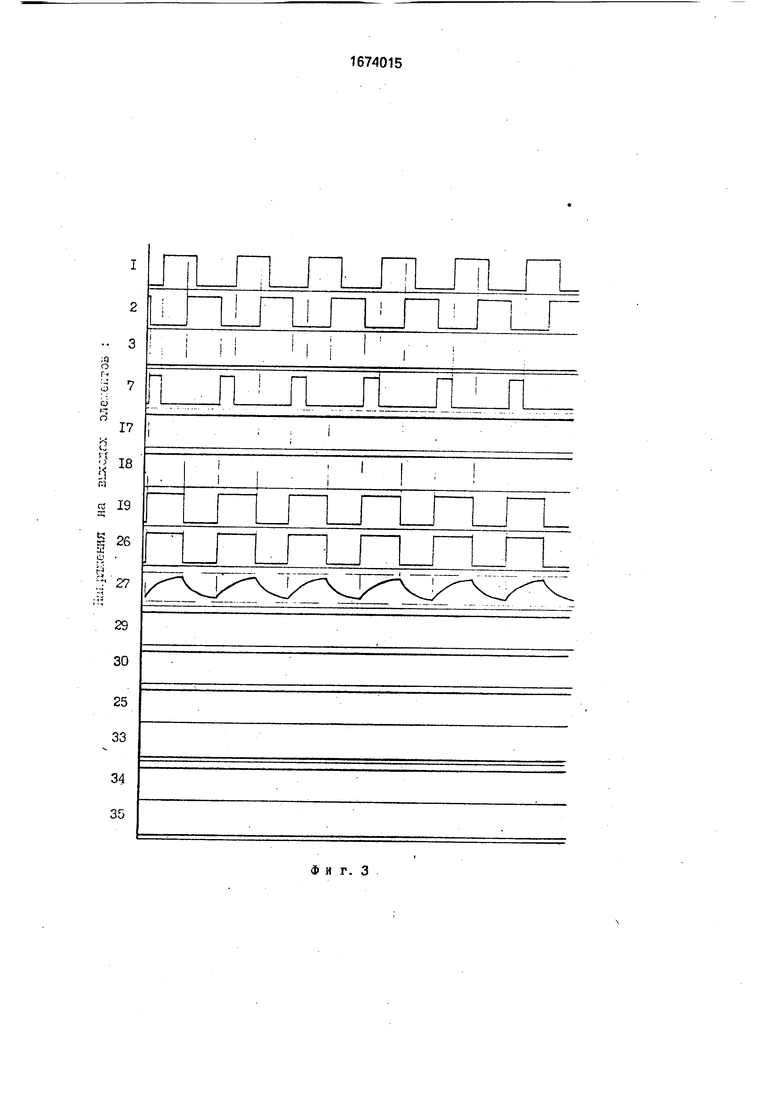

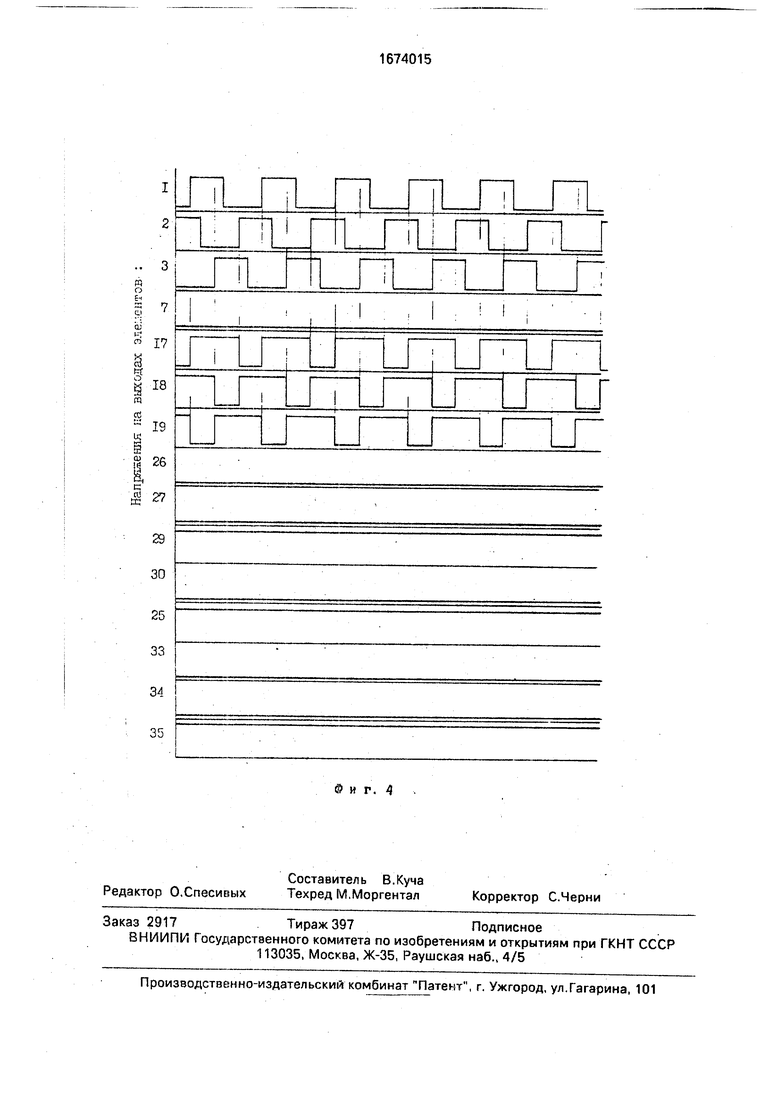

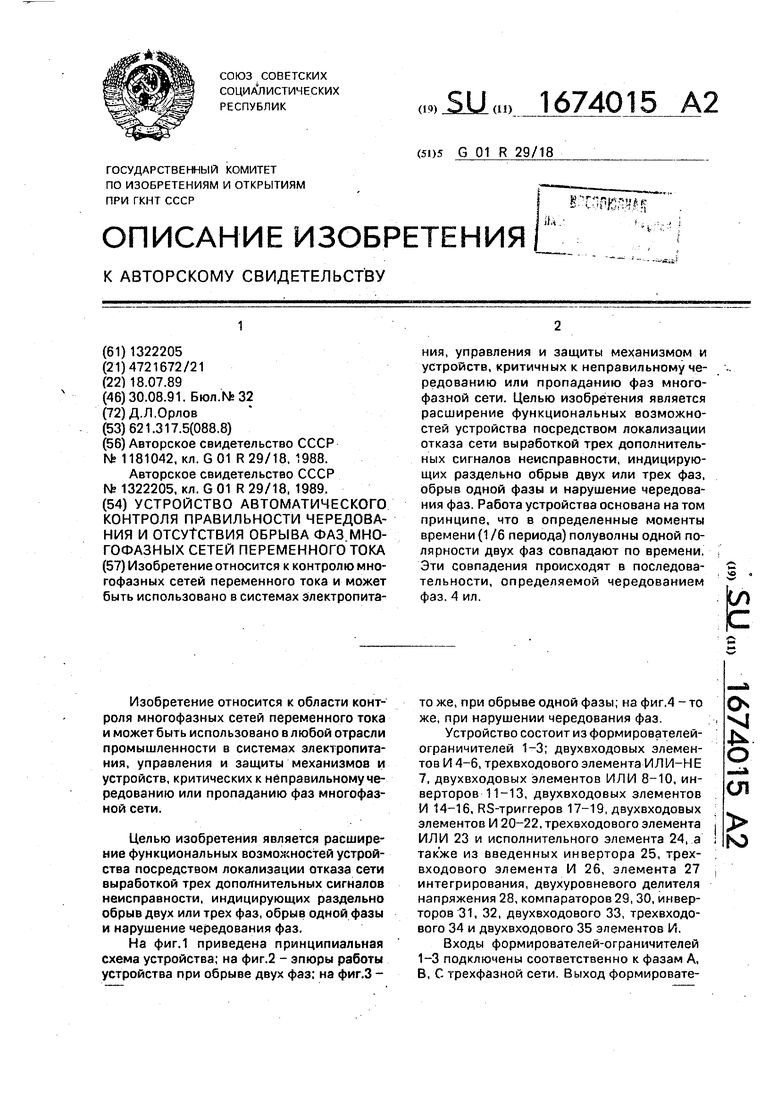

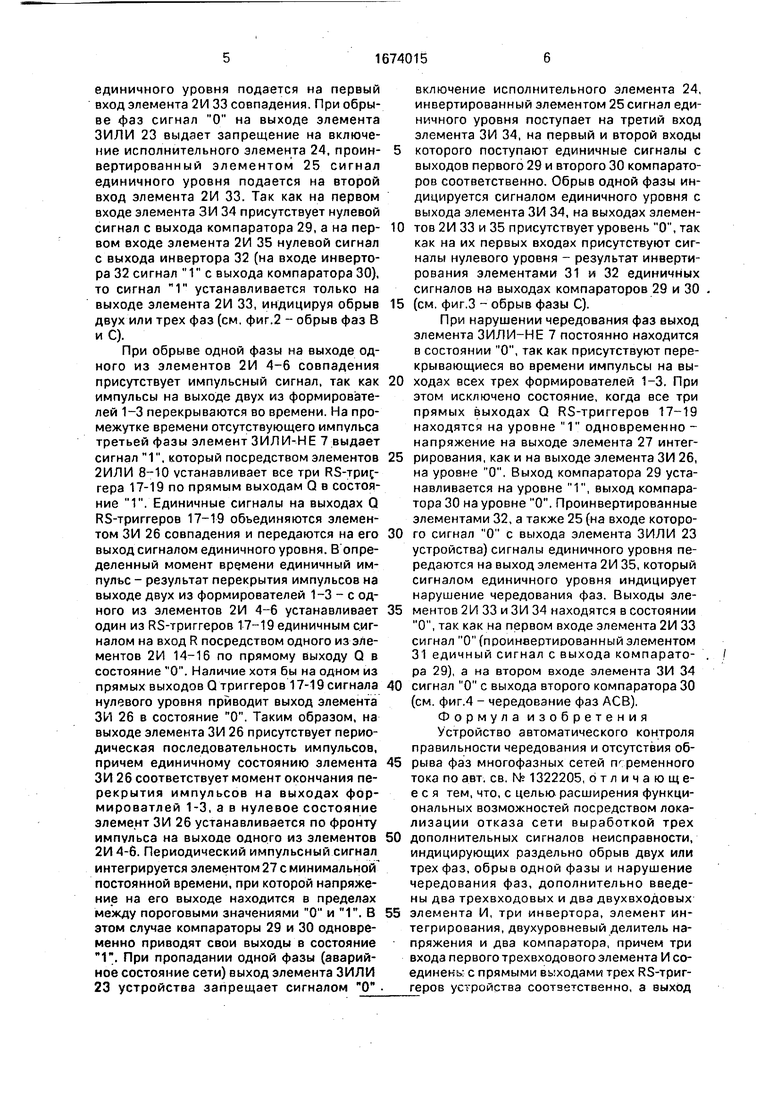

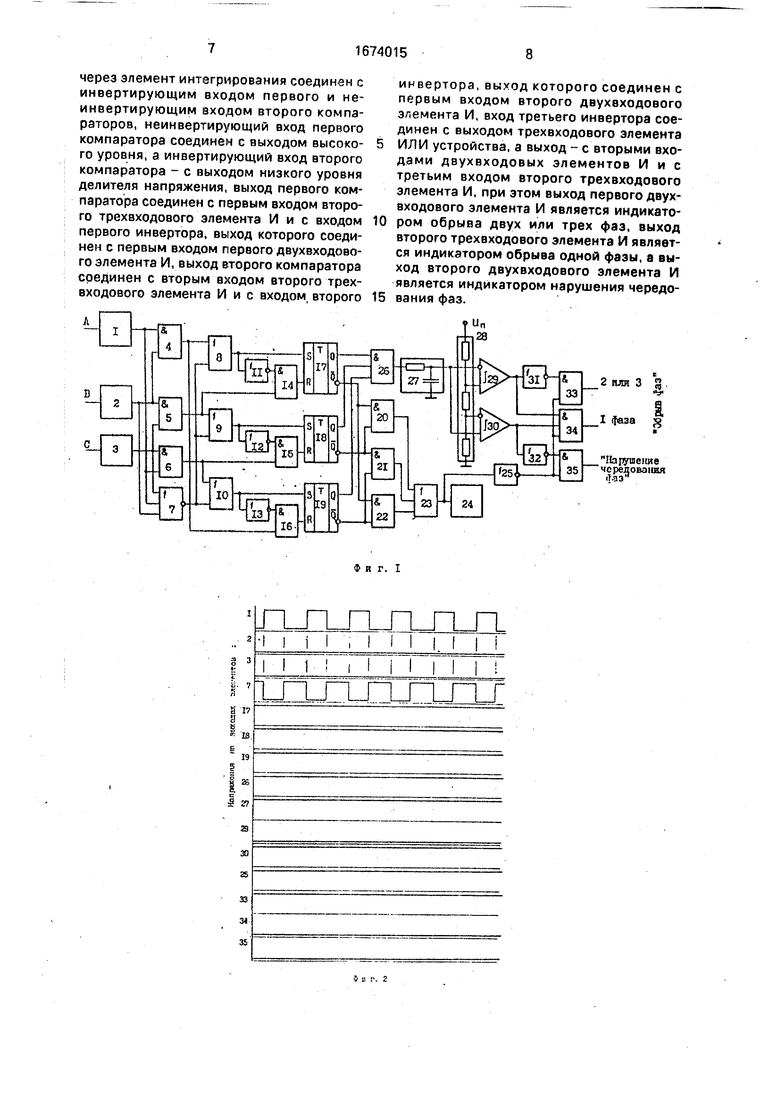

На фиг.1 приведена принципиальная схема устройства; на фиг.2 - эпюры работы устройства при обрыве двух фаз; на фиг.З то же, при обрыве одной фазы, на фиг.4 - то же, при нарушении чередования фаз.

Устройство состоит из формирователей- ограничителей 1-3; двухвходовых элементов И 4-6, трехвходового элемента ИЛИ-НЕ

7,двухвходовых элементов ИЛИ 8-10, инверторов 11-13, двухвходовых элементов И 14-16, RS-триггеров 17-19, двухвходовых элементов И 20-22, трехвходового элемента ИЛИ 23 и исполнительного элемента 24, а также из введенных инвертора 25, трехвходового элемента И 26, элемента 27 интегрирования, двухуровневого делителя напряжения 28, компараторов 29, 30, инверторов 31, 32, двухвходового 33, трехвходового 34 и двухвходового 35 элементов И.

Входы формирователей-ограничителей 1-3 подключены соответственно к фазам А,

8,С трехфазной сети. Выход формироватеО

2.

О СП

го

ля 1 соединен с первым входом элемента 2И 4 и вторыми входами элементов 2И 6 и ЗИЛИ-НЕ 7, выход формирователя 2 соединен с вторым входом элемента 2И 4, первым входом элемента 2И 5 и третьим входом элемента ЗИЛИ-НЕ 7, выход формирователя 3 соединен с вторым входом элемента 2И 5 и первыми входами элементов 2И 6 и ЗИЛИ-НЕ 7. выход элемента ЗИЛИ-НЕ 7 соединен с вторыми входами элементов 2ИЛИ 8-10, выход элемента 2И 4 соединен с первым входом элемента 2ИЛИ 8 и вторым входом элемента 2И 16, выход элемента 2И 5 соединен с первым входом элемента 2ИЛИ 9 и вторым входом элемента 2И 14, выход элемента 2И 6 соединен с первым входом элемента 2ИЛИ 10 и вторым входом элемента 2И 15, выход элемента 2ИЛИ 8 соединен с входом инвертора 11 и входом S RS-триггера 17, выход элемента 2ИЛИ 9 соединен со входом инвертора 12 и входом S RS-триггера 18, выход элемента 2ИЛИ 10 соединен с входом инвертора 13 и входом S RS-триггера 19. выходы инверторов 11-13 соединены соответственно с первыми входами элементов 2И 14-16, выходы элементов 2И 14-16 соединены соответственно со входами R RS-триггеров 17-19, прямые выходы Q RS-триггеров соединены соответственно с тремя входами элемента ЗИ 26, инверсный выход Q триггера 17 соединен с первыми входами элементов 2И 20 и 22, инверсный выход Q триггера 18 соединен с вторым входом элемента 2И 20 и первым входом элемента 2И 21, инверсный выход Q триггера 19 соединен с вторыми входами элементов 2И 21 и 22, выходы элементов 2И 20, 21, 22 соединены соответственно с тремя входами элемента ЗИЛИ 23, выход которого соединен с входами исполнительного элемента 24 и инвертора 25. Выход элемента ЗИ 26 через элемент 27 интегрирования соединен с инвертирующим входом компаратора 29 и неинвертирующим компаратора 30. Неинвертирующий вход компаратора 29 соединен с выходом верхнего уровня, а инвертирующий вход компаратора 30 - с выходом нижнего уровня двухуровневого делителя 28 напряжения. Выход компаратора 29 соединен с первым входом элемента ЗИ 34 и входом инвертора 31, выход которого соединен с первым входом элемента 2И 33. Выход компаратора 30 соединен с вторым входом элемента ЗИ 34 и входом инвертора 32, выход которого соединен с первым входом элемента 2И 35. Выход инвертора 25 соединен с вторыми входами элементов 2И 33 и 35 и с третьим входом элемента ЗИ 34. Выход элемента 2И 33 является выходом устройства в части индикации единичным

сигналом обрыва двух или трех фаз, выход элемента ЗИ 34 является выходом устройства в части индикации единичным сигналом обрыва одной фазы, выход элемента 2И 35

является выходом устройства в части индикации единичным сигналом нарушения чередования фаз.

Работа устройства основана на том принципе, что в определенные моменты

0 времени (1/6 периода) полуволны полярности двух фаз Совпадают во врмени. Эти совпадения происходят в последовательности, определяемой чередованием фаз.

При полнофазном режиме сети и при

5 чередовании фаз выход элемента ЗИЛИ-НЕ 7 находится в состоянии О, так как единичные импульсы фазных напряжений на выходах формирователей 1-3 перекрываются во времени. На прямых выходах Q триггеров

0 17-19 присутствуют чередующиеся во времени импульсы, причем перекрытия между этими импульсами нет - выход элемента ЗИ 26 находится в состоянии О. Сеть в рабочем режиме, на выходе элемента ЗИЛИ 23

5 присутствует сигнал 1, разрешающий включение исполнительного элемента 24. Сигнал с выхода элемента ЗИЛИ 23 посредством инвертирования элементом 25 выдает запрещение на входы элементов

0 совпадения 2И 33. ЗИ 34 и 2И 35. таким образом, при исправной сети выходы элементов индикации 2И 33, ЗИ 34 и 2И 35 находятся в состоянии О.

Постоянная времени элемента 27

5 интегрирования приблизительно равна длительности периода напряжения сети наименьшей частоты. Двухуровневый делитель напряжения 28 на выходе верхнего уровня устанавливает минимальное напря0 жение Г, а на выходе нижнего уровня - максимальное напряжение О.

При обрыве двух или трех фаз импульсы на выходах элементов 2И 4-6 совпадения отсутствуют, так как при наличии одной фа5 зы отсутствуют импульсы с выхода формирователя в цепи другой фазы. Выходы элементов 2И 4-6 находятся в состоянии О. В то же время на выходе элемента ЗИЛИ-НЕ 7 периодически (при обрыве двух

0 фаз) или постоянно (при обрыве трех фаз) присутствует сигнал 1. Посредством элементов 2ИЛИ 8-10 подачей сигнала 1я на входы S выходы Q RS-триггеров 17-19 устанавливаются в единичное состояние. Объе5 диненный элементом совпадения ЗИ 26 сигнал 1 через элемент 27 интегрирования подается на входы компараторов. Выход компаратора 29 устанавливается на уровне О, выход компаратора 30 - на уровне Т. Проинвертированный элементом 31 сигнал

единичного уровня подается на первый вход элемента 2И 33 совпадения. При обрыве фаз сигнал О на выходе элемента ЗИЛИ 23 выдает запрещение на включение исполнительного элемента 24, проин- вертированный элементом 25 сигнал единичного уровня подается на второй вход элемента 2И 33. Так как на первом входе элемента ЗИ 34 присутствует нулевой сигнал с выхода компаратора 29, а на первом входе элемента 2И 35 нулевой сигнал с выхода инвертора 32 (на входе инвертора 32 сигнал 1 с выхода компаратора 30), то сигнал 1 устанавливается только на выходе элемента 2И 33, индицируя обрыв двух или трех фаз (см. фиг.2 - обрыв фаз В и С).

При обрыве одной фазы на выходе одного из элементов 2И 4-6 совпадения присутствует импульсный сигнал, так как импульсы на выходе двух из формирователей 1-3 перекрываются во времени. На промежутке времени отсутствующего импульса третьей фазы элемент ЗИЛИ-НЕ 7 выдает сигнал 1, который посредством элементов 2ИЛИ 8-10 устанавливает все три RS-триг,- гера 17-19 по прямым выходам Q в состояние 1. Единичные сигналы на выходах Q RS-триггеров 17-19 объединяются элементом ЗИ 26 совпадения и передаются на его выход сигналом единичного уровня. В определенный момент времени единичный импульс - результат перекрытия импульсов на выходе двух из формирователей 1-3 - с одного из элементов 2И 4-6 устанавливает один из RS-триггеров 17-19 единичным сигналом на вход R посредством одного из элементов 2И 14-16 по прямому выходу Q в состояние О. Наличие хотя бы на одном из прямых выходов Q триггеров 17-19 сигнала нулевого уровня приводит выход элемента ЗИ 26 в состояние О. Таким образом, на выходе элемента ЗИ 26 присутствует периодическая последовательность импульсов, причем единичному состоянию элемента ЗИ 26 соответствует момент окончания перекрытия импульсов на выходах фор- мироватлей 1-3,а в нулевое состояние элемент ЗИ 26 устанавливается по фронту импульса на выходе одного из элементов 2И 4-6. Периодический импульсный сигнал

интегрируется элементом 27 с минимальной постоянной времени, при которой напряжение на его выходе находится в пределах между пороговыми значениями О и 1. В этом случае компараторы 29 и 30 одновременно приводят свои выходы в состояние 1. При пропадании одной фазы (аварийное состояние сети) выход элемента ЗИЛИ 23 устройства запрещает сигналом О

включение исполнительного элемента 24, инвертированный элементом 25 сигнал единичного уровня поступает на третий вход элемента ЗИ 34, на первый и второй входы 5 которого поступают единичные сигналы с выходов первого 29 и второго 30 компараторов соответственно. Обрыв одной фазы индицируется сигналом единичного уровня с выхода элемента ЗИ 34, на выходах злемен10 тов 2И 33 и 35 присутствует уровень О, так как на их первых входах присутствуют сигналы нулевого уровня - результат инвертирования элементами 31 и 32 единичных сигналов на выходах компараторов 29 и 30

5 (см. фиг.3 - обрыв фазы С).

При нарушении чередования фаз выход элемента ЗИЛИ-НЕ 7 постоянно находится в состоянии О, так как присутствуют перекрывающиеся во времени импульсы на вы0 ходах всех трех формирователей 1-3. При этом исключено состояние, когда все три прямых выходах Q RS-триггеров 17-19 находятся на уровне 1 одновременно - напряжение на выходе элемента 27 интег5 рирования, как и на выходе элемента ЗИ 26, на уровне О. Выход компаратора 29 устанавливается на уровне 1, выход компаратора 30 на уровне О, Проинвертированные элементами 32, а также 25 (на входе которо0 го сигнал О с выхода элемента ЗИЛИ 23 устройства) сигналы единичного уровня передаются на выход элемента 2И 35, который сигналом единичного уровня индицирует нарушение чередования фаз. Выходы эле5 ментов 2И 33 и ЗИ 34 находятся в состоянии О, так как на первом входе элемента 2И 33 сигнал О(проинвертиоованный элементом 31 едичный сигнал с выхода компаратора 29), а на втором входе элемента ЗИ 34

0 сигнал О с выхода второго компаратора 30 (см. фиг.4 - чередование фаз АСВ). Формула изобретения Устройство автоматического контроля правильности чередования и отсутствия об5 рыва фаз многофазных сетей п ременного тока по авт. св. № 1322205, отличающееся тем, что, с целью расширения функциональных возможностей посредством локализации отказа сети выработкой трех

0 дополнительных сигналов неисправности, индицирующих раздельно обрыв двух или трех фаз, обрыв одной фазы и нарушение чередования фаз, дополнительно введены два трехвходовых и два двухвходовых

5 элемента И, три инвертора, элемент интегрирования, двухуровневый делитель напряжения и два компаратора, причем три входа первого трехвходового элемента И соединена с прямыми выходами трех RS-триггеров устройства соответственно. а выход

через элемент интегрирования соединен с инвертирующим входом первого и неинвертирующим входом второго компараторов, неинвертирующий вход первого компаратора соединен с выходом высокого уровня, а инвертирующий вход второго компаратора - с выходом низкого уровня делителя напряжения, выход первого компаратора соединен с первым входом второго трехвходового элемента И и с входом первого инвертора, выход которого соединен с первым входом первого двухвходово- го элемента И, выход второго компаратора соединен с вторым входом второго трехвходового элемента И и с входом второго

0

5

инвертора, выход которого соединен с первым входом второго двухвходового элемента И, вход третьего инвертора соединен с выходом трехвходового элемента ИЛИ устройства, а выход - с вторыми входами двухвходовых элементов И и с третьим входом второго трехвходового элемента И, при этом выход первого двухвходового элемента И является индикатором обрыва двух или трех фаз, выход второго трехвходового элемента И является индикатором обрыва одной фазы, а выход второго двухвходового элемента И является индикатором нарушения чередования фаз.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматического контроля правильности чередования и отсутствия обрыва фаз многофазных сетей переменного тока | 1986 |

|

SU1322205A1 |

| Устройство для синхронизации группы преобразователей | 1984 |

|

SU1231566A1 |

| Устройство контроля чередованияфАз ТРЕХфАзНОй НАгРузКи | 1978 |

|

SU813324A1 |

| Реверсивный распределитель импульсов | 1981 |

|

SU953728A1 |

| Способ регулирования частоты вращения трехфазного асинхронного электродвигателя | 1985 |

|

SU1376209A1 |

| Устройство для компенсации реактивной мощности | 1990 |

|

SU1746463A1 |

| Реверсивный распределитель импульсов | 1978 |

|

SU752806A1 |

| Многокамерное хранилище сельскохозяйственной продукции с регулируемой газовой средой | 1983 |

|

SU1399921A1 |

| УСИЛИТЕЛЬ МОЩНОСТИ ДЛЯ УПРАВЛЕНИЯ ИСПОЛНИТЕЛЬНЫМ ДВИГАТЕЛЕМ ПЕРЕМЕННОГО ТОКА | 1995 |

|

RU2103804C1 |

| Устройство для определения поврежденной фазы в сети с изолированной нейтралью | 1985 |

|

SU1257583A1 |

Изобретение относится к контролю многофазных сетей переменного тока и может быть использовано в системах электропитания, управления и защиты механизмов и устройств, критичных к неправильному чередованию или пропаданию фаз многофазной сети. Целью изобретения является расширение функциональных возможностей устройства посредством локализации отказа сети выработкой трех дополнительных сигналов неисправности, индицирующих раздельно обрыв двух или трех фаз, обрыв одной фазы и нарушение чередования фаз. Работа устройства основана на том принципе, что в определенные моменты времени (1/6 периода) полуволны одной полярности двух фаз совпадают по времени. Эти совпадения происходят в последовательности, определяемой чередованием фаз. 4 ил.

; i

2 пли з 2

I фаза g

Нарушение

чередования

Ф и г. I

Л

г

3

7

17

П

П П П П ; П

ft

н18

Г.)

g 26

29 30

25

33

34 35

Ф и г. 3

Г

17 i 18

J

19 26 27

29

30

25

33

34

35

Г

D

L

3

| Устройство для контроля чередования и обрыва фаз трехфазной сети | 1984 |

|

SU1181042A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство автоматического контроля правильности чередования и отсутствия обрыва фаз многофазных сетей переменного тока | 1986 |

|

SU1322205A1 |

Авторы

Даты

1991-08-30—Публикация

1989-07-18—Подача