I

Изобретение относится к технике передачи и приема дискретной информации по каналам связи при нестабильной несущей частоте сигнала. В реальных каналах изменение частоты вызывается рядом причин, в частности эффектом Допплера, нестабильностью генераторов и т. д., что приводит к снижению помехоустойчивости.

Для улучшения помехоустойчивости в условиях нестабильной частоты используют известные способы автоматической подстройки частоты и фазы, а также специальные способы модуляции и демодуляции, нечувствительные к изменению частоты. При использовании фазоразностной модуляции (ФРМ), для обеспечения нечувствительности к изменению частоты сигнала вместо ФРМ первого порядка (ФРМ-1) применяют ФРЛ1 более высоких порядков.

Однако известные системы связи с ФРМ имеют недостаточную помехоустойчивость к флуктуациям частоты сигнала.

Целью изобретения является повышение помехоустойчивости системы к флуктуациям частоты сигнала.

Для этого на выходе канала связи включен приемник фазоразностной модуляции второго порядка, содержащий два квадратурных автокоррелятора, состоящих из общего элемента памяти наполовину длительности посылки,

фазовращателя, двух перемножителей и двух интеграторов со сбросом, выходы которых непосредственно и через другие элементы памяти наполовину длительности посылки подключены к соответствующим перемнол ителям, выходы которых через сумматор подключены к пороговому элементу, другой вход которого связан с блоком для управления и синхронизации, соединенным также с элементами памяти наполовину длительности посылки и с входами сброса интеграторов.

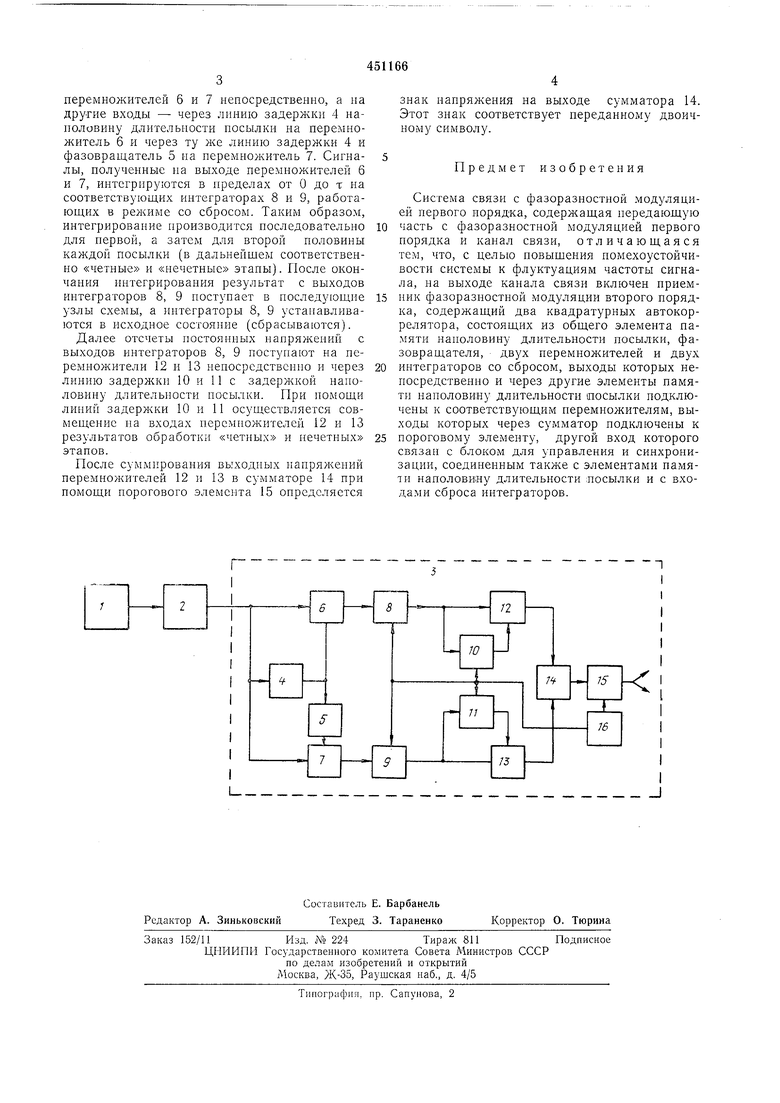

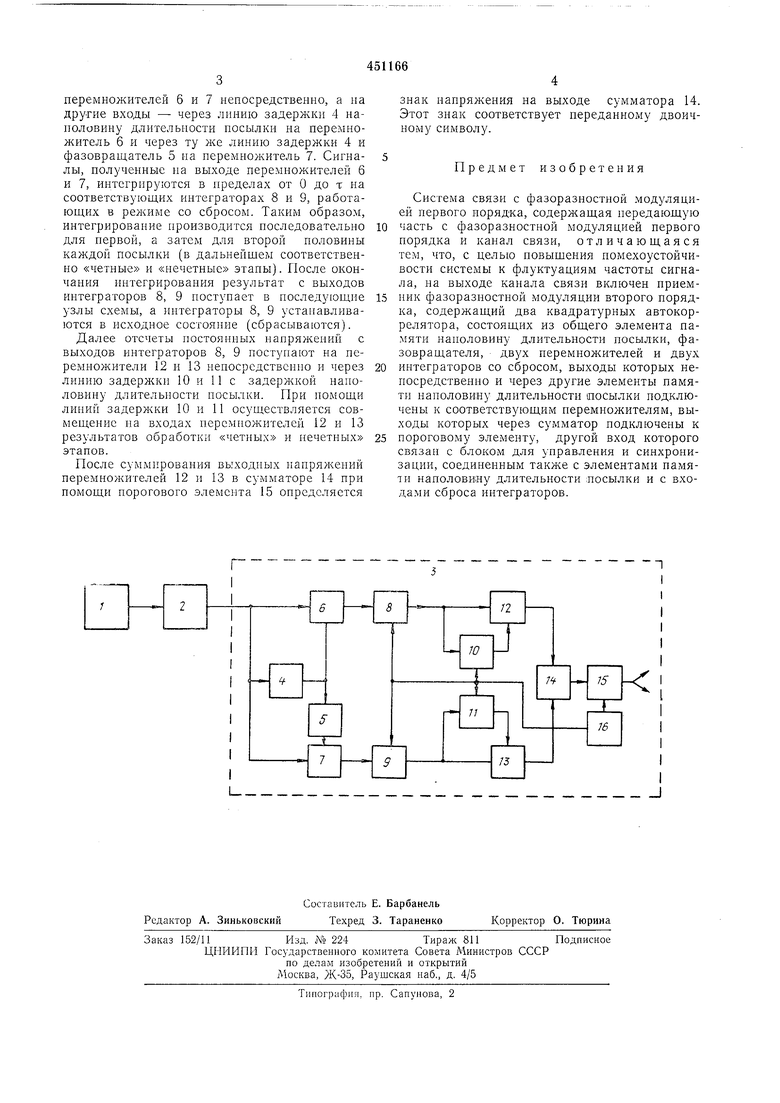

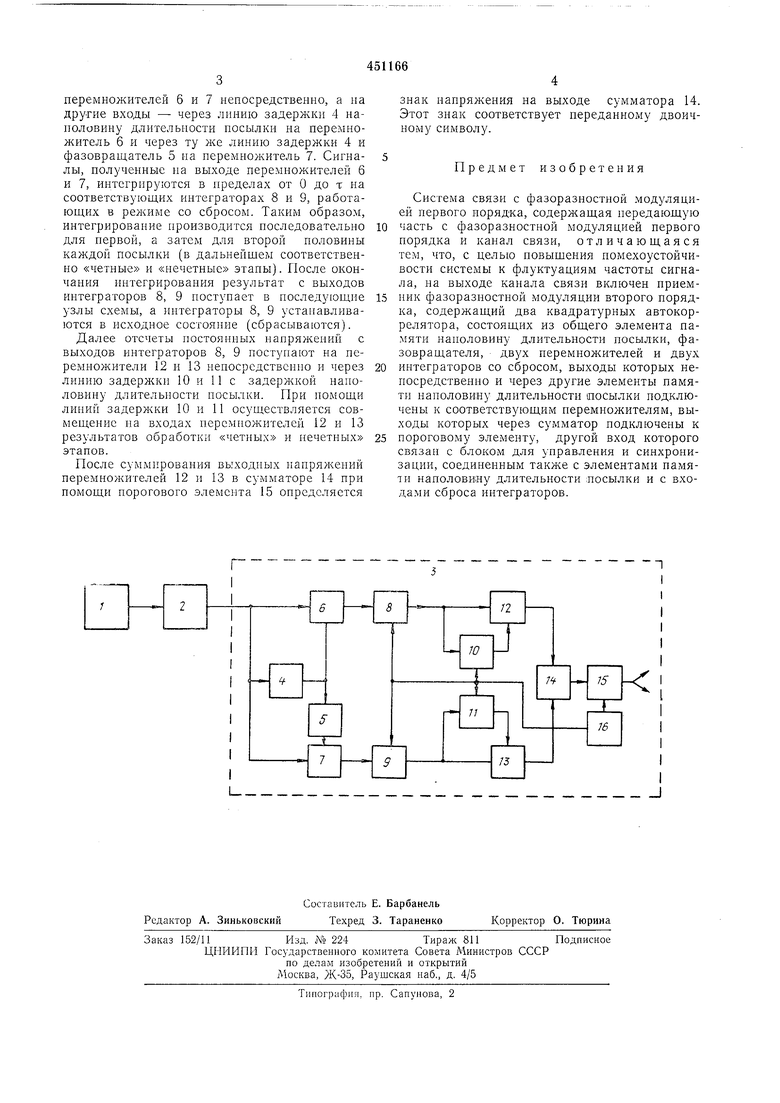

На чертеже прпведепа блок-с.хема системы.

Система связи с фазоразностной модуляцией первого порядка содержит передатчик сигналов с фазоразностной модуляцией первого порядка 1, канал связи 2 и автокорреляциониый приемник 3, содержаиип линию задержки наполовину длительности посылки сигнала 4, фазовращатель 5, дающий сдвиг на .п/2, иеремножители переменных напряжении 6 и 7, интеграторы с устройством сброса 8, 9, линии задержки 10 и 11, иеремножители постоянных напряжений 12 и 13, сумматор постоянных напряжений 14, пороговый элемент 15 и блок 16 для сиихронизации и управления.

Информация вложена в первые разности фаз в соответствии с принципом модуляции в системах ФРМ-1.

После прохол дения ио каналу связи 2 сигнал иостуиает в приемник 3 на одни из входор

перемножителей 6 и 7 непосредственно, а на другие входы - через линию задержки 4 наиоловину длительности иосылки на перемиожитель 6 и через ту же линию задержки 4 и фазовращатель 5 на иеремножитель 7. Сигналы, полученные на выходе перемножителей 6 и 7, интегрируются в пределах от О до т на соответствующих интеграторах 8 и 9, работающих в режиме со сбросом. Таким образом, интегрирование иропзводится последовательно для первой, а затем для второй ноловпны каждой иосылки (в дальнейшем соответственно «четные и «нечетные этапы). После окончания интегрирования результат с выходов иитеграторов 8, 9 поступает в последующие узлы схемы, а интеграторы 8, 9 устанавливаются в исходное состояние (сбрасываются).

Далее отсчеты постоянных напряжений с выходов интеграторов 8, 9 поступают на перемиожители 12 и 13 непосредствепио и через линию задержки 10 и 11 с задержкой наполовину длительности иосылки. При помощи линий задержки 10 и 11 осуществляется совмещение па входах перемпожителей 12 и 13 результатов обработки «четных и нечетных этапов.

После суммирования выходных напряжений перемножителей 12 п 13 в сумматоре 14 при помощи порогового элемента 15 определяется

знак напряжения на выходе сумматора 14. Этот знак соответствует переданному двоичному символу.

Предмет изобретения

Система связи с фазоразностной модуляцией первого порядка, содержащая иередающую часть с фазоразностной модуляцией первого порядка и каиал связи, отличающаяся тем, что, с целью повышения помехоустойчивости системы к флуктуациям частоты сигнала, на выходе канала связи включен нриемник фазоразпостной модуляции второго иорядка, содержащий два квадратурных автокоррелятора, состоящих из общего элемента памяти наполовину длительности посылки, фазовращателя, двух перемножителей и двух иитеграторов со сбросом, выходы которых непосредственно и через другие элементы памяти иаполовину длительности посылки подключены к соответствующим перемножителям, выходы которых через сумматор подключеиы к иороговому элементу, другой вход которого связан с блоком для управления и синхронизации, соединенным также с элементами памяти наполовину длительности лосылки и с входа.ми сброса интеграторов.

Авторы

Даты

1974-11-25—Публикация