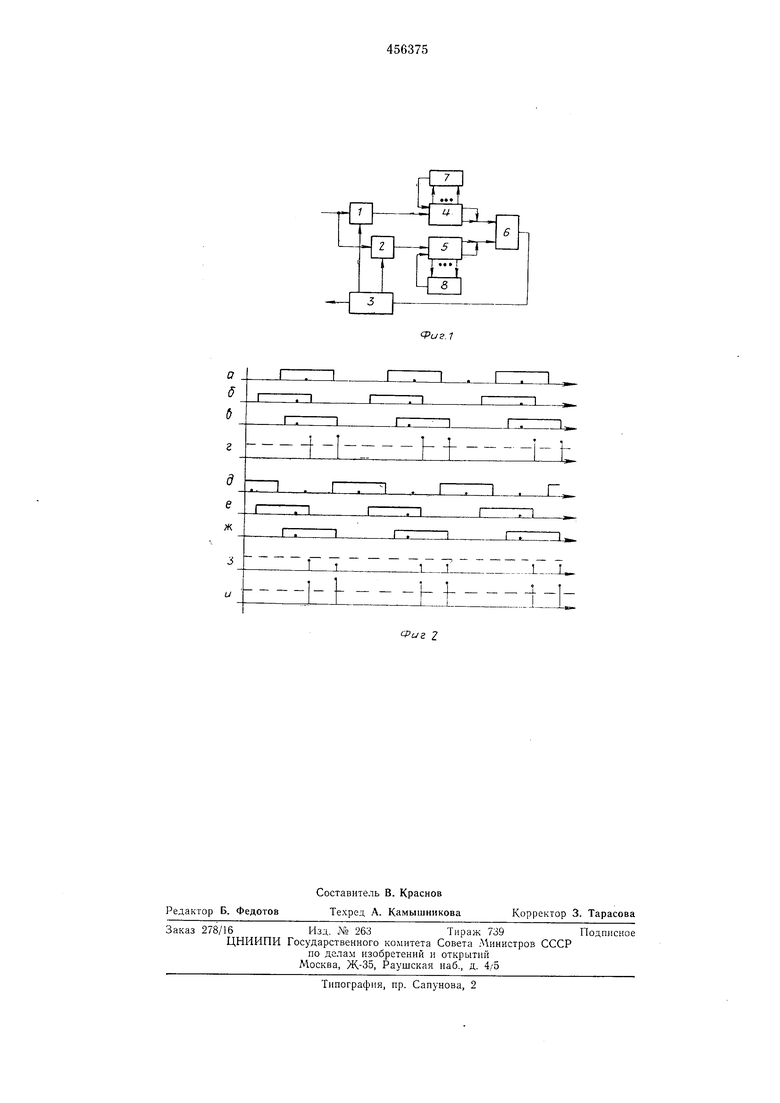

вой положительной посылки интегратор 5 фиксирует величину большую, чем интегратор 4 (фиг. 2 г). Кроме того, оба интегратора фиксируют величины, превышающие половину своего объема (фиг. 2 г, штрих), в результате чего срабатывают дешифраторы 7 и 8.

При опросе интеграторов, например, путем подачи импульсов по прямому входу (так как появились сигналы на выходах дешифраторов 7 и 8) сигнал на выходе интегратора 5 появляется раньше, чем на выходе интегратора 4. Оба сигнала поступают на схему сравнения 6, где определяется время их прихода. После анализа сигнал со схемы сравнения б подается на генератор 3, и весовые функции сдвигаются вправо на некоторый отрезок времени. В синфазном положении интеграторы фиксируют одинаковый результат, и весовые функции не сдвигаются (графики а, б, в, пятая посылка).

Если же в некоторый момент времени весовые функции попадают между положительными посылками (графики д, е, ж), интегратор 4 фиксирует величину большую, чем интегратор 5, и оба фиксируют величины, меньшие половины своего объема (график з). Интеграторы опрашиваются по обратным входам, так как дешифраторы не сработали. Сигнал на выходе интегратора 5 появляется раньше (график и показывает результаты интегрирования в обратном коде), чем на выходе интегратора 4, и весовые функции сдвигаются вправо на некоторый промежуток времени.

В некоторых случаях один из интеграторов опрашивается по прямому входу, а другой - по обратному.

Весовые функции сдвигаются в сторону того интегратора, на выходе которого сигнал появляется раньше.

Таким образом, с помощью только двух последовательно соединенных перемножителей с интеграторами, схемы сравнения двух величин и генератора двух весовых функций можно добиться синфазного положения между генератором приемника и принимаемыми сигналами, что существенно упрощает устройство и, тем самым, повышает его надежность.

„

Предмет изобретения

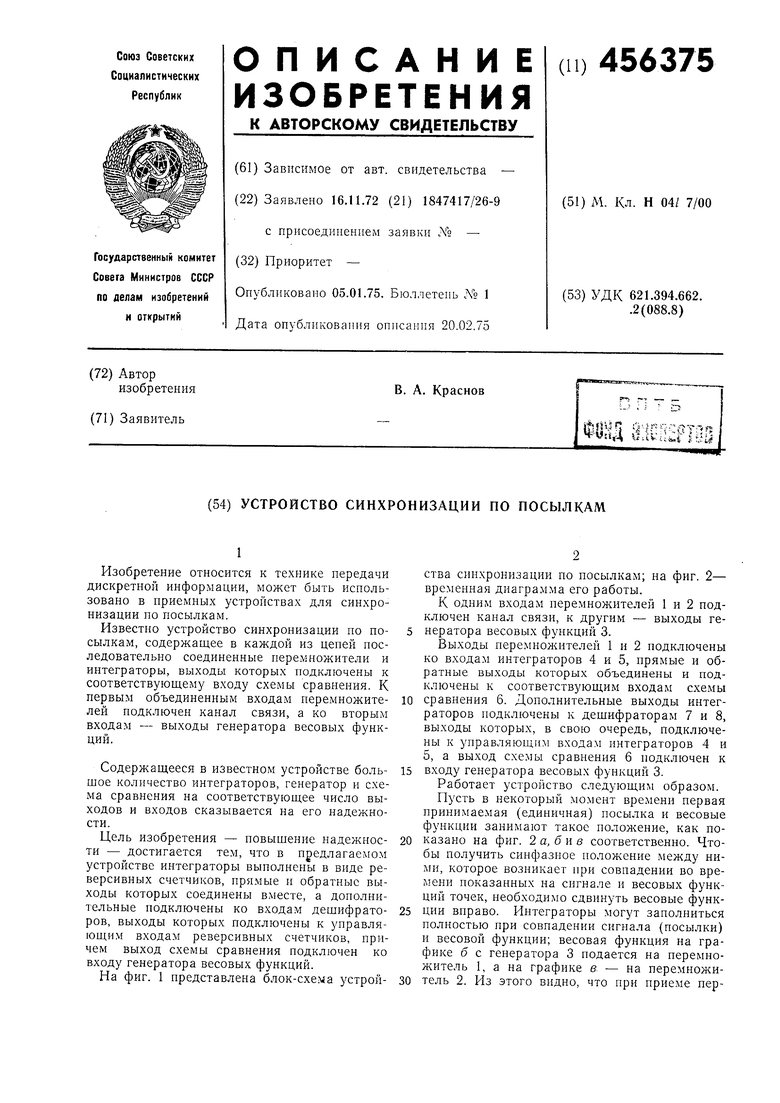

Устройство синхронизации по посылкам, содержащее в каждой из цепей последовательно соединенные перемножители и интеграторы, выходы которых подключены к соответствующему входу схемы сравнения, причем первые входы перемножителей соединены вместе, а вторые подключены к соответствующему выходу генератора весовых функций, отличающееся тем, что, с целью повышения надежности, интеграторы выполнены в виде реверсивных счетчиков, прямые и обратные выходы которых соединены вместе, а дополнительные подключены ко входам дешифраторов, выходы которых подключены к управляюшим входам реверсивпых счетчиков, причем выход схемы сравнения подключен ко входу генератора весовых функций.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СИНХРОНИЗАЦИИ ПО ПОСЫЛКАМ | 1971 |

|

SU308528A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU1008919A1 |

| Способ синхронизации по посылкам | 1981 |

|

SU1091360A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1172046A1 |

| Многоканальный модулятор-демодулятор | 1982 |

|

SU1083398A2 |

| ВСЕСОЮЗНАЯ ,[ядш1Т1/о.га1;-т н^.^^ I-. j^у^ -" « * -• • J >&•__^ЬЛИОТЕКА | 1971 |

|

SU315283A1 |

| Устройство синхронизации по посылкам | 1981 |

|

SU965003A1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

| СПОСОБ ДЕМОДУЛЯЦИИ СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2000 |

|

RU2168869C1 |

| Устройство для приема узкополосных телеграфных сигналов | 1989 |

|

SU1737739A1 |

Авторы

Даты

1975-01-05—Публикация

1972-11-16—Подача