(54) УСТРОЙСТВО СИНХРОНИЗАЦИИ ПО ПОСЫЛКАМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ синхронизации по посылкам | 1981 |

|

SU1091360A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU1008919A1 |

| Устройство синхронизации корреляционного приемника псевдослучайных сигналов | 1982 |

|

SU1069182A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1172046A1 |

| Устройство регистрации телеграфных посылок | 1991 |

|

SU1781833A1 |

| Устройство цикловой синхронизации последовательного модема | 1986 |

|

SU1450123A1 |

| Устройство для квазикогерентного приема фазоманипулированных сигналов | 1984 |

|

SU1239885A1 |

| Устройство для приема сигналов с относительной фазовой модуляцией | 1986 |

|

SU1356253A1 |

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| Устройство для измерения защищенности сигналов от помех | 1989 |

|

SU1658399A1 |

Изобретение относится к технике |синхронной связи .и может быть использовано в приемных устройствах для синхронизации по посылкам.

Известно устройство синхрониза-. ции по посылкам, содержащее объединенные -по первому входу два перемножителя, к вторым входам которых подключены выходы генератора опорных сигналов, а также два реверсивных счетчика, прямые и обратные выходы которых объединены и подключены к входам блока сравнения, выход которого подключен ко входу генератора опорных сигналов, при этом дополнительные выходь реверсивных счетчиков подключены к входам дешифраторов, выходы которых подключены к управляющим входам реверсивных счетчиков fl.

Недостатком известного устройства. я&1яется наличие ложных сдвигов ( в направлениях от синфазного состояния) при работе по посылкам произвольной кодовой комбинации, что приводит к снижению точности синхронизации и уменьшению времени вхождения в синхронизм.

Цель изобретения - повышение точности синхронизации и уменьшение времени вхождения в синхронизм.

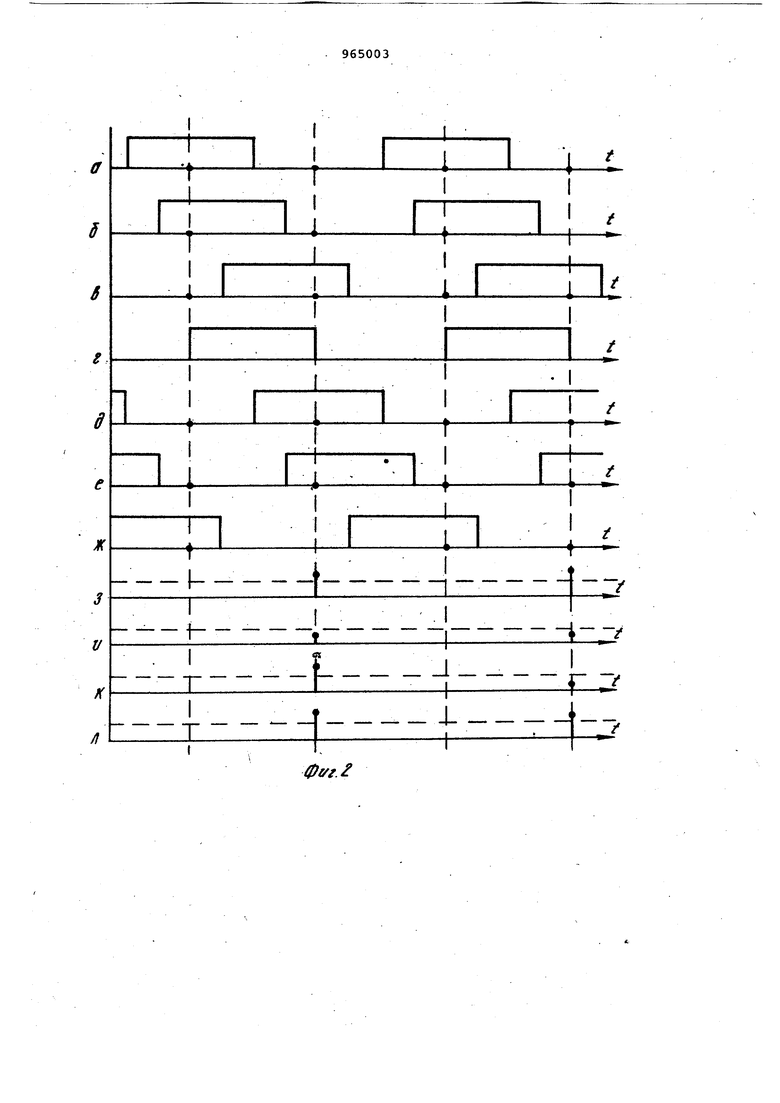

Поставленная цель достигается тем, что в устройство синх19онизации по посылкам, содержащее объединенные по первому входу два перемножителя, к вторым входам которых подключены выходы генератора опо10рных сигналов, а также два реверсивных счетчика, прямые и обратные выходы которых объединены и подключены к входам блока сравнения, выход которого-подключен к входу ге15нератора опорных сигналов, при этом дополнительные выходы реверсивных счетчиков подключены к входам дешифраторов , выходы которых подключены к управляющим входам реверсив20ных счетчиков, введены последовательно соединенные первый инвертор, третий перемножитель, первый элемент ИЛИ и первый ключ, а также второй инвертор, генератор стробирова-25НИН и последовательно соединенные третий инвертор, четвертый перемножитель, второй элемент ИЛИ и второй ключ, к управляющему входу которогс а также к управляющему входу первого ключа подсоединен выход генератора стробирования, к входу которого подключен выход блока сравнения, а выходы первого и второго ключей соединены со входами первого и второго реверсивных счетчиков, при это выходы генератора опорных сигналов подключены соответственно к входу третьего генератора и через второй инвертор к второму входу третьего перемножителя, первый вход которого объединен со вторым входом четверто го перемножителя, при этом вход пер вого инвертора объединен с первыми входами первого и второго перемножителей, выходы которых подключены ко вторым входам элементов ИЛИ. На фиг. 1 представлена структурная схема устройства; на фиг. 2 4 - временные диаграммы его работы точкам (фиг. 2 и 3) и по посылкам произвольной комбинации . (фиг. 4). Диаграммы на фиг. 2 отображают работу устройства при синфазном положении принимаемых и опорных сигналов, на фиг. 3 и 4 - при сдвиге опорных сигналов относительно синфазного положения. Устройство синхронизации по посылкам содержит первый и второй пер множители 1 и 2, первый инвертор 3, |вторрй и третий перемножители 4 и 5 генератор 6 опорных сигналов, второй и третий инверторы 7 и 8, первый и второй элементы ИЛИ 9 и 10, . первый и второй ключи 11 и 12, первый и второй реверсивные счетчики , 13 и 14, генератор 15 стробирования первый и второй дешифраторы 16 и 17 блок 18 сравнения. о Устройство работает следующим образом. Принимаемые посылки (фиг. 2а, За 4а) поступают на входы перемножителей 1 и 2 и умножаются в них на адо ные сигналы (б, в), снимаеглые с выходов генератора 6 опорных сигналов и задержанные один относительно другого на четверть периода. В пере множителях 4 и 5 осуществляется . перемножение инвертированных посылок (д) и опорных сигналов (е, ж), снимаемых с инверторов 3, 7 и 8 соответственно. При совпадении положительных полярностей сомножителей с выходов перемножителей на соответ ствующие входы элементов ИЛИ 9 и 10 поступают счетные импульсы. С выходов элементов ИЛИ 9 и 10 импульсы поступают на сигнальные входы ключе 11 и 12. На управляющие вкоды |слюче 11 и 12 с выхода генератора 15 стро бирования поступает стробирующий, сигнал (-г),задержанный относительно первого опорного сигнала (б) на одну восьмую периода. На временных интервалах, совпадающих с- положительными п лупёриодами строБирующего сигн,эла, счетные импульсы проходят через клю чи 11 и 12, поступают на прямые входы реверсивных счетчиков 13 и 14 и суммируются (интегрируются) там. Результаты интегрирования, зафиксированные в реверсивных счетчиках 13 и 14 (з, и), пропорциональны суммарной дгительности интервалов совпадения полярностей принимаег/их посылок с первым и вторым опорными сигналами на интервале интегрирования соответственно. Реверсивные счетчики 13 и 14 могут заполниться полностью при совпадении в соответствующем перемножителе полярностей перемножаемых сигналов на всем интервале интегрирования. Если результат интегрирования больше половины объема реверсивного счетчика (пунктир- ная линия на з, и, к, л) то срабатывает соответствующий дешифратор. Опрос каждого реверсивного счётчика осуществляется после окончания интегрирования путем подачи импульсов с выхода соответствукщего дешифратора по обратному входу в случае, когда дешифратор сработал, и по прямому входу - в противном случае.. В результате опроса реверсивные, счетчики 13 и 14 обнуляются, и сигна jfa с их выходов поступают на блок 18 сравнения, где определяется время их прихода. При срабатывании дешифраторов 16 и 17 моменты поступления сигналов на блок 18 сравнения задержаны относительно моментов окончания интегрирования на времена, пропорциональные результатам интегрирования. (3, и). В противном случае задержка сигналов пропорциональна результатам интегрирования в обратном коде (к, л). Если первым на вход блока сравнения 18 поступает сигнал.с первого реверсивного счетчика 13, то сигнал с его выхода на входы генератора 6 опорных сигналов и генератора 15 стробирования, и вызывает сдвиг опорных и стробирующего сигналов влево. В случае, когда сигнал с второго рев рсивного счётчика 14 поступает первым, . сигнал с выхода блока 18 сравнения вызывает сдвиг сигналов вправо. При одновременном появлении сигналов на входе блока 18 сравнения сигнал на его выходе не формируется и сдвиг опорных сигналов не происходит. Таким образом, устройство синхронизации по посылкам позволяет повысить точность синхронизации и уменьшить время вхождения в синхронизм при работе по посыпкам произвольной кодовой комбинации за отсутствия ложных сдвигов. Формула изобретения Устройство синхронизации по посылкам, содержащее объединенные по

первому входу два перемножителя, к вторым входам которых подключены выходы генератора опорных сигнсшов, а также два реверсивных счетчика, прямые и обратные выходы которых объединены и подключены к входам блока сравнения, выход которого подключен к входу генератора опорных сигналов, при этом дополнительные.выходы реверсивных счетчиков подключены к входам дешифраторов, выходы которых подключены к управляюв им входам реверсивных счетчиков, о т л и ч а ю щ е е с я тем, что, с целью Повышения точности синхронизации и уменьшения времени вхогхдения в синхронизм, введены последовательно соединенные первый инвертор, третий перемножитель, первый элемент ИЛИ и первый ключ, а также второй инвертор, генератор стробирования и последовательно соединенные третий инвертор, четвертый перемнокитель, второй элемент ИЛИ и второй :ключ, к управляющему входу которого

ffxff

а также к управлякадему входу первого ключа подсоединен выход генератора стробирования, к входу которого подключен выход блока сравнения, а выходы первого и второго ключей

.соединены с входами первого, и второго реверсивных счетчиков, при этом выходы генератора опорных сигналов подключены соответственно к входу третьего инвертора и через второй инвертор к второму входу третьего перемножителя, первый- вход которого объединен со вторым входом четвертого перемножителя, при этом ВХОД первого инвертора объединен с

первыми входами первого и второго I перемножителей, выходы которых под.ключены ко вторым входам элементов ИЛИ.

Источники информации,

принятые во внимание при экспертизе

0fff.

Авторы

Даты

1982-10-07—Публикация

1981-03-16—Подача