1

Изобретение относится к радиотехнике и может использоваться для формирования импульсов.

Известен мультивибратор, содержащий соединенные в кольцо логические схемы «ИЛИ- НЕ, причем вторая логическая схема «ИЛИ-НЕ шунтирована конденсатором.

Однако такой мультивибратор не может генерировать сигналы в ждущем режиме.

Цель изобретения - генерирование сигнала в ждущем режиме.

Для этого в предлагаемом мультивибраторе выход первой логической схемы «ИЛИ-НЕ подключен к второму входу третьей логической схемы «ИЛИ-НЕ.

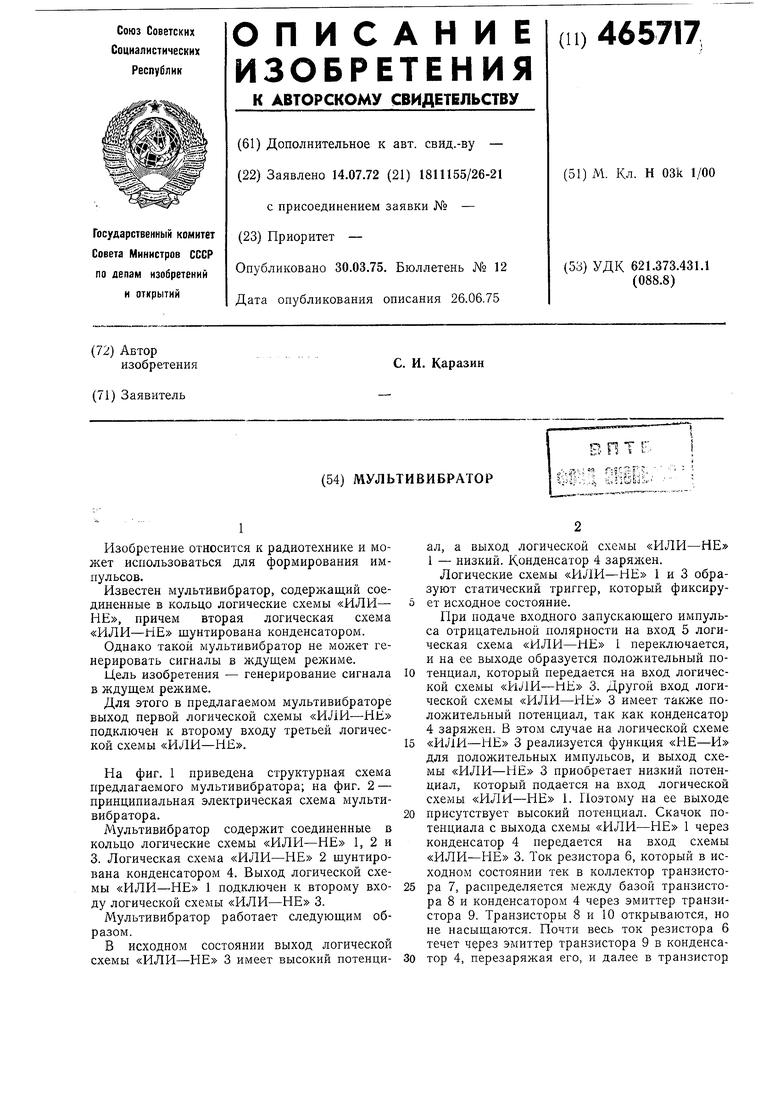

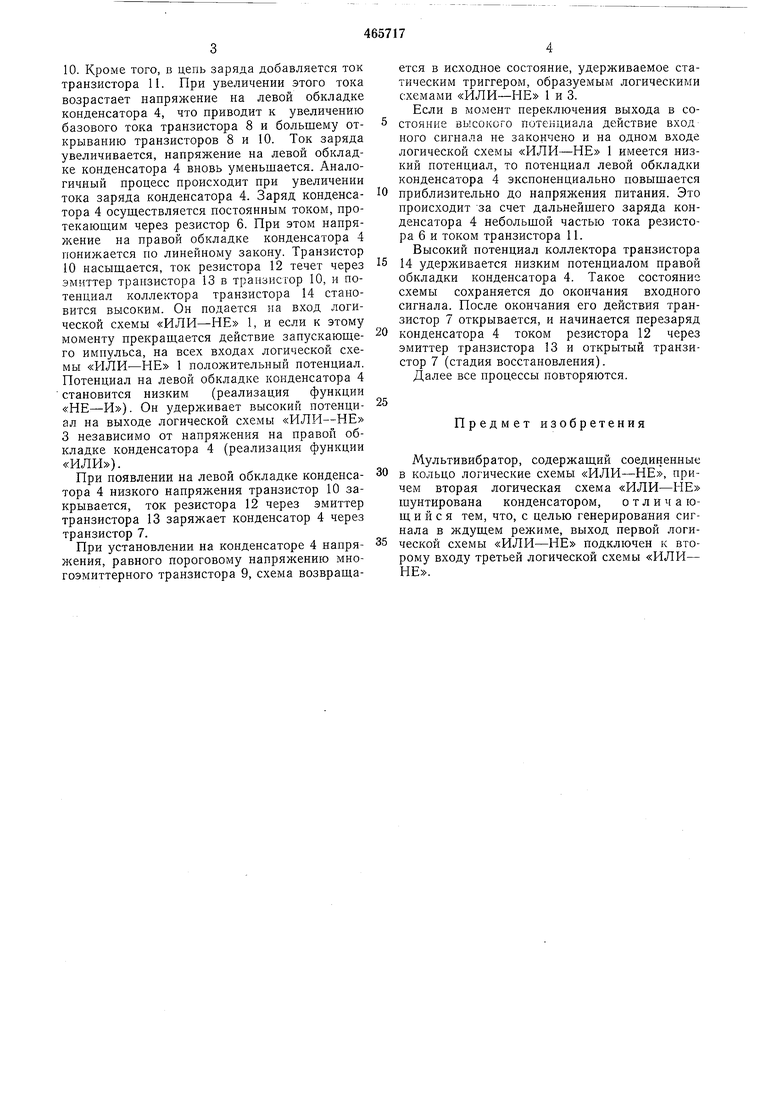

На фиг. 1 приведена структурная схема предлагаемого мультивибратора; на фиг. 2 - принципиальная электрическая схема мультивибратора.

Мультивибратор содержит соединенные в кольцо логические схемы «ИЛИ-НЕ 1, 2 и 3. Логическая схема «ИЛИ- НЕ 2 шунтирована конденсатором 4. Выход логической схемы «ИЛИ-НЕ 1 подключен к второму входу логической схемы «ИЛИ-НЕ 3.

Мультивибратор работает следующим образом.

В исходном состоянии выход логической схемы «ИЛИ-НЕ 3 имеет высокий потенциал, а выход логической схемы «ИЛИ-НЕ 1 - низкий. Конденсатор 4 заряжен.

Логические схемы «ИЛИ-НЕ 1 и 3 образуют статический триггер, который фиксирует исходное состояние.

Нри подаче входного запускающего импульса отрицательной полярности на вход 5 логическая схема «ИЛИ-НЕ 1 переключается, и на ее выходе образуется положительный потенциал, который передается на вход логической схемы «ИЛИ-НЕ 3. Другой вход логической схемы «ИЛИ-НЕ 3 имеет также положительный потенциал, так как конденсатор 4 заряжен. В этом случае на логической схеме «ИЛИ-НЕ 3 реализуется функция «НЕ-И для положительных импульсов, и выход схемы «ИЛИ-НЕ 3 приобретает низкий потенциал, который подается на вход логической схемы «ИЛИ-НЕ 1. Поэтому на ее выходе присутствует высокий потенциал. Скачок потенциала с выхода схемы «ИЛИ-НЕ 1 через конденсатор 4 передается на вход схемы «ИЛИ-НЕ 3. Ток резистора 6, который в исходном состоянии тек в коллектор транзистора 7, распределяется между базой транзистора 8 и конденсатором 4 через эмиттер транзистора 9. Транзисторы 8 и 10 открываются, но не насыщаются. Почти весь ток резистора 6 течет через эмиттер транзистора 9 в конденсатор 4, перезаряжая его, и далее в транзистор

10. Кроме того, в цепь заряда добавляется ток транзистора 11. При увеличении этого тока возрастает напряжение на левой обкладке конденсатора 4, что приводит к увеличению базового тока транзистора 8 и большему открыванию транзисторов 8 и 10. Ток заряда увеличивается, напряжение на левой обкладке конденсатора 4 вновь уменьшается. Аналогичный процесс происходит при увеличении тока заряда конденсатора 4. Заряд конденсатора 4 осушествляется постоянным током, протекаюшим через резистор 6. При этом напряжение на правой обкладке конденсатора 4 понижается по линейному закону. Транзистор 10 насышается, ток резистора 12 течет через эмиттер транзистора 13 в транзистор 10, и потенциал коллектора транзистора 14 становится высоким. Он подается на вход логической схемы «ИЛИ-НЕ 1, и если к этому моменту прекращается действие запускающего импульса, на всех входах логической схемы «ИЛИ-НЕ 1 положительный потенциал. Потенциал на левой обкладке конденсатора 4 становится низким (реализация функции «НЕ-И). Он удерживает высокий потенциал на выходе логической схемы «ИЛИ-НЕ 3 независимо от напряжения на правой обкладке конденсатора 4 (реализация функции «ИЛИ).

При появлении на левой обкладке конденсатора 4 низкого напряжения транзистор 10 закрывается, ток резистора 12 через эмиттер транзистора 13 заряжает конденсатор 4 через транзистор 7.

При установлении на конденсаторе 4 напряжения, равного пороговому напряжению многоэмиттерного транзистора 9, схема возвращается в исходное состояние, удерживаемое статическим триггером, образуемым логическими схемами «ИЛИ-НЕ 1 и 3.

Если в момент переключения выхода в состояние высокого потенциала действие вход иого сигнала не закончено и на одном входе логической схемы «ИЛИ-НЕ 1 имеется низкий потенциал, то потенциал левой обкладки конденсатора 4 экспоненциально повышается

0 приблизительно до напряжения питания. Это происходит за счет дальнейшего заряда конденсатора 4 небольшой частью тока резистора 6 и током транзистора 11.

Высокий потенциал коллектора транзистора

5 14 удерживается низким потенциалом правой обкладки конденсатора 4. Такое состояние схемы сохраняется до окончания входного сигнала. После окончания его действия транзистор 7 открывается, и начинается перезаряд

0 конденсатора 4 током резистора 12 через эмиттер транзистора 13 и открытый транзистор 7 (стадия восстановления). Далее все процессы повторяются.

Предмет изобретения

Мультивибратор, содержащий соединенные в кольцо логические схемы «ИЛИ-НЕ, причем вторая логическая схема «ИЛИ-НЕ шунтирована конденсатором, отличающийся тем, что, с целью генерирования сигнала в ждущем режиме, выход первой логической схемы «ИЛИ-НЕ подключен к второму входу третьей логической схемы «ИЛИ- НЕ.

5 0-

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство согласования коммутационной цепи переменного тока с интегральной микросхемой | 1984 |

|

SU1307552A1 |

| Ждущий мультивибратор | 1979 |

|

SU845270A1 |

| Устройство для контроля генератора тактовых импульсов | 1983 |

|

SU1105836A1 |

| Ждущий многофазный мультивибратор | 1980 |

|

SU919060A1 |

| Мультивибратор | 1981 |

|

SU983985A1 |

| Преобразователь напряжения в длительность импульсов | 1990 |

|

SU1785071A1 |

| Ждущий мультивибратор | 1986 |

|

SU1396246A1 |

| РЕЛЕ ВРЕМЕНИ (С ВЫХОДОМ НА СИМИСТОРЕ) | 1992 |

|

RU2130213C1 |

| Ждущий мультивибратор | 1988 |

|

SU1626339A1 |

| Ждущий мультивибратор | 1990 |

|

SU1739484A1 |

/|/

Авторы

Даты

1975-03-30—Публикация

1972-07-14—Подача