Изобретение относится к цифровой вычислительной технике и может быть использовано при построении вычислительных машин и систем обработки данных.

Известно устройство для сопряжения цифровой вычислительной машины с внешним накопителем по авт. св. № 389504, содержащее электронные часы, логические схемы, ключи, триггеры, блок управления и буферный регистр. Однако с помощью этого устройства невозможно обнаружить ложные импульсы, поступающие из накопителя в интервалах между тактовым импульсом и меткой времени, а также между сигналом опроса, поступающим с буферного регистра, и меткой времени.

Цель изобретения - расширение эксплуатационных возможностей устройства.

Предлагаемое устройство отличается от известного тем, что содержит дополнительный триггер, первую и вторую дополнительные схемы «ИЛИ, схему регистрации, линию задержки и дополнительную схему совпадения, выход которой соединен с входом схемы регистрации, первый вход соединен с входом схемы разделения, а второй - с выходом дополнительного триггера. Входы триггера соединены с выходами дополнительных схем «ИЛИ соответственно, причем первый вход первой дополнительной схемы «ИЛИ соединен с выходом буферного регистра связи и с входом

второй схемы совпадения, второй вход через линию задержки соединен с первым выходом схемы разделения и с входом электронных часов и схемы управления. Первый вход второй дополнительной схемы «ИЛИ соединен с выходом электронных часов и с нулевым входом третьего триггера, второй вход второй дополнительной схемы «ИЛИ соединен с вторым выходом электронных часов.

Такое выполнение позволяет повысить эксплуатационные качества устройства за счет обнаружения ложных импульсов, поступающих с внешнего накопителя.

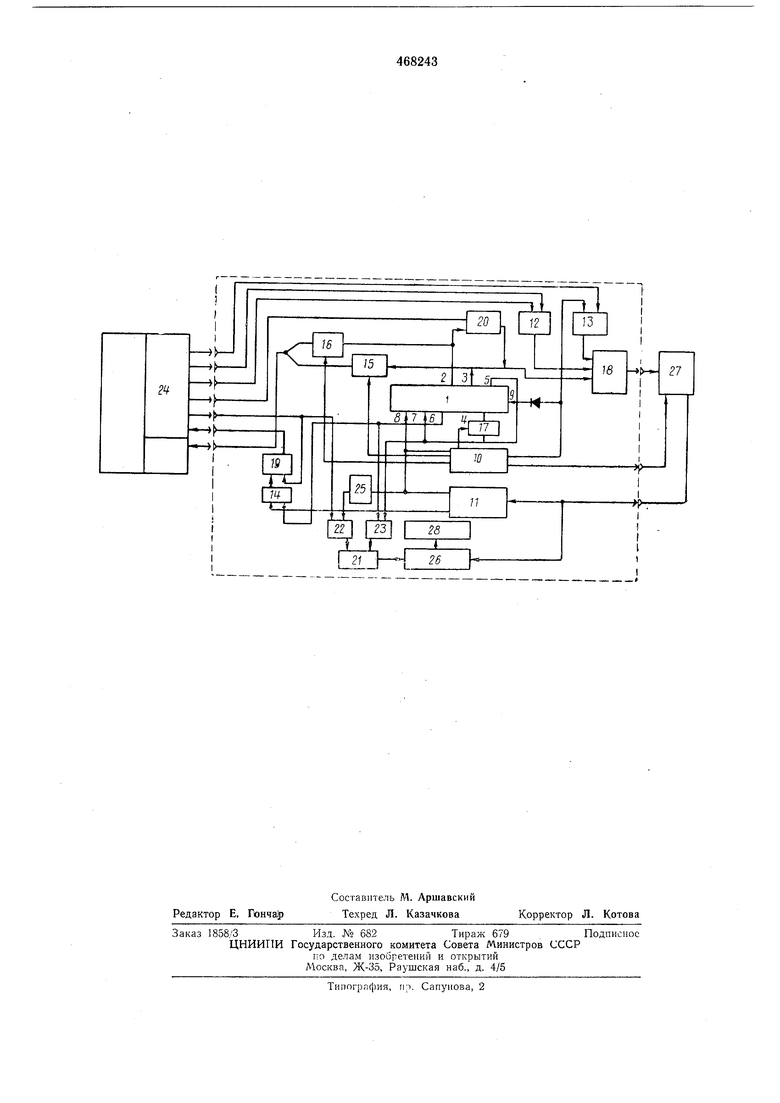

На чертеже показана блок-схема устройства для сопряжения.

Предлагаемое устройство содержит электронные часы 1 с выходами 2-6 и входами 7-9, схему 10 управления, схему 11 разделения, триггеры 12-14, ключи 15-17 и схемы 18-20 совпадения, а также дополнительный триггер 21, входы которого через дополнительные схемы «ИЛИ 22 и 23 соединены с выходом буферного регистра 24 связи через линию задержки 25 с тактовым выходом схемы 11 разделения, с выходами 3 и 4 электронных часов 1. Выход триггера 21 подключен к входу схемы 26 совпадения, второй вход которой соединен с выходом накопителя 27. Выход схемы 26 совпадения соединен со схемой 28 регистрации.- -. - -.

Предлагаемое устройство работает в режиме записи информации из вычислительной машины в накопитель и в считывания ее из накопителя и передачи в вычислительную машину. В режиме записи информация, поступаюшая из вычислительной машины, перестраивается по заданной циклограмме и передается в накопитель 27, триггер 21, схемы 22 и 23 «ИЛИ. Линия 25 задержки, схема 26 совпадения и схема 28 регистрации при этом в работе не участвуют.

В режиме считывания сигналами со схемы 10 управления задается режим работы накопителя 27, запирается ключ 15, открываются ключи 16 и 17 и дается команда в накопитель на начало считывания информации. Схема И разделения сигналов разделяет информацию, приходяшую из накопителя 27 на тактовые и кодовые импульсы, тактовые импульсы подаются на вход 8 электроннь1Х часов 1 и служат командой начала отсчета времени. Кроме того, через линию 25 задержки и схему 22 ИЛИ они поступают на единичный вход триггера 21 и на его выходе появляется сигнал. Кодовые импульсы подаются на триггер 14.

С выхода 2 электронных часов 1 через ключ 16 в вычислительную машину подается импульс, который с Определенной задержкой выходит из машины и подается на схему 19 совпадения. Если в этот момент на выходе триггера 14 есть сигнал, он передается в вычислительную машину и воспринимается, как код единицы.

Кодовый импульс должен появляться на выходе накопителя с определенным сдвигом после тактового. Если он появится слишком рано, сигнал, снимаемый с выхода 6 электронных часов 1 и определяющий нижний предел допустимого сдвига, сбросит триггер 14 и этот кодовый импульс не пройдет в буферный регистр связи 24 вычислительной машины. Этот же сигнал с выхода 6, пройдя через схему 23 «ИЛИ, перебросит триггер 21 в другое состояние, и сигнал на его выходе исчезнет. Таким образом, если на. выходе накопителя 27 появится ложный импульс в интервале времени между тактовым импульсом и сигналом с выхода 6, то он пройдет через схему 26 совпадения в схему 28 регистрации ложных импульсов. Линия 25 задержки выбрана таким образом, чтобы она задерживала тактовый импульс на время, равное его длительности. Это необходимо, чтобы исключить подачу одного

и того же тактового импульса одновременно на два входа схемы 26 совпадения.

Верхняя граница допустимого смещения кодового импульса относительно тактового определяется временем появления сигнала из вычислительной машины, подаваемого на вход схемы 19 совпадения. По сигналу с выхода 4, который подается на сбросовый вход 9 электронных часов 1 и на вход 7, прекращая подачу эталонной частоты на вход счетчика электронных часов 1, которые прекращают отсчет времени и подготавливаются к приему следующего тактового импульса со схемы 11 разделения.

Так же, как описано, схема 26 совпадения открывает вход схемы 28 регистрации для приема ложных импульсов в интервале времени между опросом очередного кодового импульса по сигналу с буферного регистра 24

связи и сигналом с выхода 4 электронных часов 1.

Таким образом, дополнительное устройство позволяет выявить ложные импульсы, записанные в накопитель 27, в интервалах между

тактовыми и кодовыми импульсами.

Предмет изобретения

Устройство для сопряжения цифровой вычислительной машины с внешними накопителями по авт. св. № 389504, отличающееся тем, что, с целью расширения эксплуатационных возможностей, оно содержит дополнительный триггер, первую и вторую дополнительные

схемы «ИЛИ, схему регистрации, линию задержки и дополнительную схему совпадения, выход которой соединен со входом схемы регистрации, первый вход соединен со входом схемы разделения, а второй вход - с выходом

дополнительного триггера, входы которого соединены с выходами дополнительных схем ИЛИ соответственно, первый вход первой дополнительной схемы «ИЛИ соединен с выходом буферного регистра связи и со входом

второй схемы совпадения, второй вход через линию задержки соединен с первым выходом схемы разделения и со входом электронных часов и схемы управления, первый вход второй дополнительной схемы «ИЛИ соединен с

выходом электронных часов п с нулевым входом третьего триггера, второй вход второй дополнительной схемы «ИЛИ соединен со вторым выходом электронных часов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1973 |

|

SU497577A2 |

| В !•'. Г? | 1973 |

|

SU389504A1 |

| Устройство для обмена информацией | 1974 |

|

SU503228A1 |

| Устройство для вывода информации | 1983 |

|

SU1124279A1 |

| Устройство для соряжения цифровой вычислительной машины с внешним накопителем | 1975 |

|

SU575653A1 |

| СИСТЕМА ОБНАРУЖЕНИЯ И СОПРОВОЖДЕНИЯ СУДОВ В АКВАТОРИИ ПОГРАНИЧНОЙ ЗОНЫ | 2019 |

|

RU2714614C1 |

| СИСТЕМА ОПОЗНАВАНИЯ "СВОЙ-ЧУЖОЙ" | 2001 |

|

RU2191403C1 |

| Устройство для воспроизведения мно-гОКАНАльНОй МАгНиТНОй зАпиСи | 1979 |

|

SU836662A1 |

| Статистический анализатор | 1974 |

|

SU533940A2 |

| Устройство для автоматического контроля блоков памяти | 1976 |

|

SU610180A1 |

Авторы

Даты

1975-04-25—Публикация

1973-03-30—Подача