мического диапазона без использования дополнительного усилителя для этой цели.

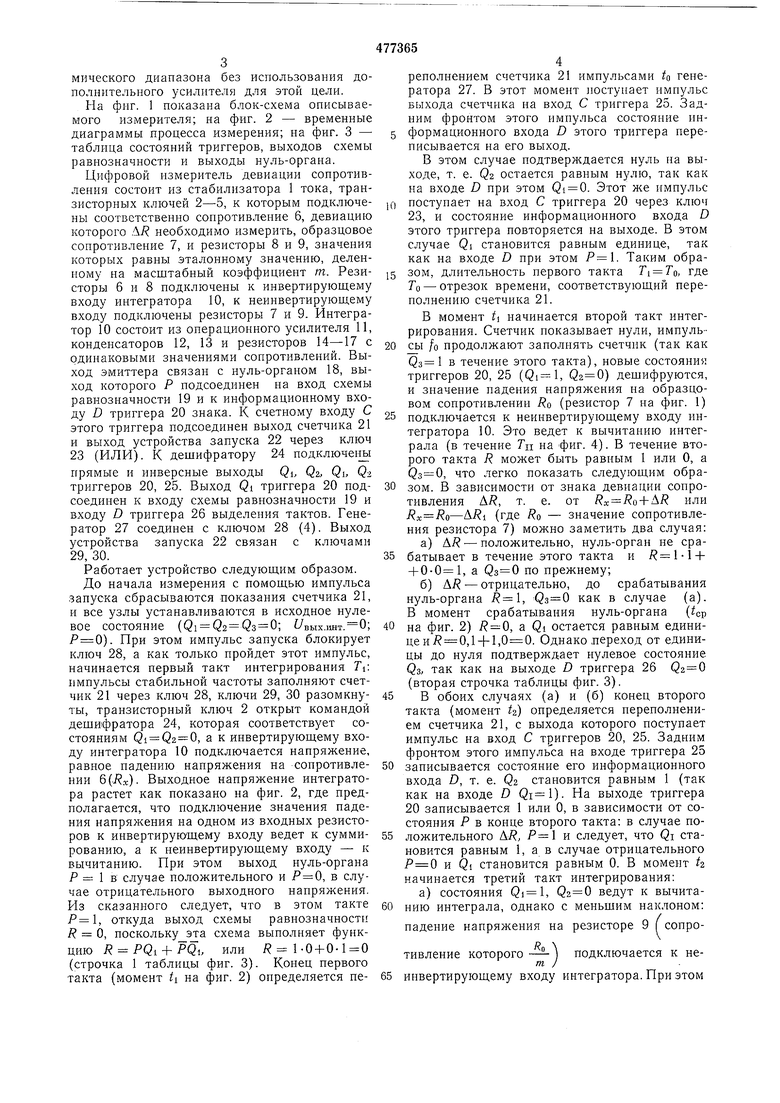

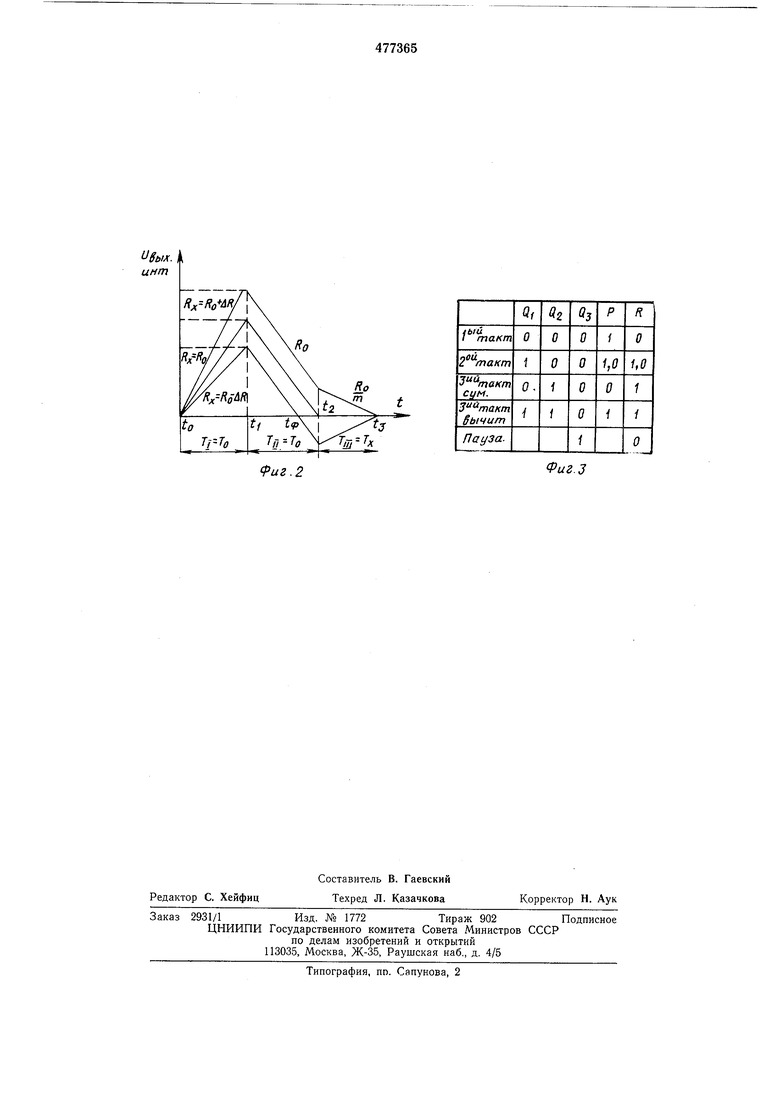

На фиг. 1 показана блок-схема описываемого измерителя; на фиг. 2 - временные диаграммы процесса измерения; на фиг. 3 - таблица состояний триггеров, выходов схемы равнозначности и выходы нуль-органа.

Цифровой измеритель девиации сопротивления состоит из стабилизатора 1 тока, транзисторных ключей 2-5, к которым подключены соответственно соиротивлеиие 6, девиацию которого ДУ необходимо измерить, образцовое сопротивление 7, и резисторы 8 и 9, значения которых равны эталонному значению, деленному на масштабный коэффициеит т. Резисторы 6 и 8 подключены к инвертирующему входу иитегратора 10, к неинвертируюш,ему входу подключены резисторы 7 и 9. Интегратор 10 состоит из операционного усилителя 11, конденсаторов 12, 13 и резисторов 14-17 с одинаковыми значениями сопротивлений. Выход эмиттера связан с нуль-органом 18, выход которого Р подсоединен на вход схемы равнозначности 19 и к информационному входу D триггера 20 знака. К счетному входу С этого триггера подсоединен выход счетчика 21 и выход устройства запуска 22 через ключ 23 (ИЛИ). К дешифратору 24 подключегш

прямые и инверсные выходы Qi, Qz, Qt, Q-i триггеров 20, 25. Выход Qi триггера 20 подсоедииен к входу схемы равнозначиости 19 и входу D триггера 26 выделения тактов. Генератор 27 соединен с ключом 28 (4). Выход устройства запуска 22 связан с ключами 29, 30.

Работает устройство следующим образом.

До начала измерения с помощью импульса запуска сбрасываются показания счетчика 21, и все узлы устанавливаются в исходное нулевое состояние (Qi 0; /вых.инт.0; ). При этом импульс запуска блокирует ключ 28, а как только пройдет этот импульс, начинается первый такт интегрирования Ть импульсы стабильной частоты заполняют счетчик 21 через ключ 28, ключи 29, 30 разомкнуты, транзисторный ключ 2 открыт командой дешифратора 24, которая соответствует состояниям Qi , а к инвертирующему входу интегратора 10 подключается напряжение, равное падению напряжения на сопротивлении 6(Rx)- Выходное напряжение интегратора растет как показано на фиг. 2, где предполагается, что подключение значения падения напряжения на одном из входных резисторов к инвертирующему входу ведет к суммированию, а к неинвертирующему входу - к вычитанию. При этом выход нуль-органа Р 1 в случае положительного и , в случае отрицательного выходного напряжения. Из сказанного следует, что в этом такте , откуда выход схемы равнозначности R - О, поскольку эта схема выполняет функцию R PQi + PQi, или / l-0-fO-l 0 (строчка 1 таблицы фиг. 3). Конец первого такта (момент ti на фиг. 2) определяется переполнением счетчика 21 импульсами to геператора 27. В этот момент поступает пмпульс выхода счетчика на вход С триггера 25. Задним фронтом этого импульса состояние пн5 формационного входа D этого триггера переписывается на его выход.

В этом случае подтверждается нуль на выходе, т. е. Q2 остается равным нулю, так как на входе D при этом Qi 0. Этот же импульс поступает на вход С триггера 20 через ключ 23, и состояние информационного входа D этого триггера повторяется на выходе. В этом случае Qi становится равным единице, так как на входе D при этом Р. Таким образом, длительность первого такта Ti To, где То - отрезок времени, соответствующий переполнению счетчика 21.

В момент t начинается второй такт интегрирования. Счетчик иоказывает нули, импуль20 сь1 /о продолжают заполпять счетчик (так как

Q3 1 в течение этого такта), новые состояния триггеров 20, 25 (, ) дешифруются, и значение падения напряжения на образцовом сопротивлении Ко (резистор 7 на фиг. 1)

25 подключается к неинвертирующему входу интегратора 10. Это ведет к вычитанию интеграла (в течение Гц на фиг. 4). В течение второго такта R может быть равным 1 или О, а , что оТегко показать следующим образом. В зависимости от знака девиации соиротивления А, т. е. от Rx Ro + R. или з.:(, (где RO - значение сопротивления резистора 7) можно заметить два случая:

а)А/ -положительно, нуль-орган не срабатывает в течение этого такта и + + , а по прежнему;

б)А/ - отрицательно, до срабатывания нуль-органа 1, как в случае (а). В момент срабатывания нуль-органа (iop на фиг. 2) , а QI остается равным единице и 0,1+1,. Однако .переход от единицы до нуля подтверждает нулевое состояние QS, так как на выходе D триггера 26 (вторая строчка таблицы фиг. 3).

В обоих случаях (а) и (б) конец второго такта (момент /2) определяется переполнением счетчика 21, с выхода которого поступает импульс на вход С триггеров 20, 25. Задним фронтом этого импульса на входе триггера 25

0 записывается состояние его информационного входа D, т. е. Q2 становится равным 1 (так как на входе D ). Па выходе триггера 20 записывается 1 или О, в зависимости от состояния Р в конце второго такта: в случае положительного и следует, что Qi становится равным 1, а в случае отрицательного и QI становится равным 0. В момент 4 начинается третий такт интегрирования:

а) состояния Q)l, ведут к вычитанию интеграла, однако с меньшим наклоном:

падение напряжения на резисторе 9 ( сопроRO

тивление которого -- подключается к /

инвертирующему входу интегратора. При этом

.1+0-0 1, а по прежнему (строка 4 таблицы фиг. 3);

б) состояния Qi 0, ведут к суммированию интеграла так же с меньшим наклоном, чем во втором такте: падение напряжения

о / R на резисторе о ( сопротивление которого

подключается к инвертирующему входу интегратора. При этом У 1 1+0-0 1, (строка 3 таблицы фиг. 3). В момент tz в обоих случаях (а) и (б), как только срабатывает нуль-орган, изменяется состояние Р, и выходной сигнал схемы равнозначности становится равным нулю: / 1-O-fО-1 1 или j 0-1-f 1-0 0. Переход / от 1 до О определяет конец третьего такта (конец измерения), так как при этом переходе на выходе триггера 26 отражается состояние его входа Д т. е.

и, следовательно, , вследствие чего закрывается ключ 28, и кончается заполнение счетчика 21 импульсами о. При этом цифровой результат измерения фиксируется в счетчике в требуемом масштабе. Знак девиации сопротивления можно фиксировать и индицировать в зависимости от состояния Qi и Q2 в

течеиие третьего такта. Таким образом, относительная измеряемая девиация сопротивления линейно связана с относительным показанием счетчика.

Предмет изобретения

Цифровой измеритель девиации сопротивления, содержащий устройство запуска, генератор эталонных импульсов, ключи, счетчик, связанный с тактовыми входами триггеров знака и выделения тактов, дешифратор, стабилизатор тока, измеряемое и образцовое сопротивления, подключенные к входам дифференциального интегратора, нуль-орган, отличаю HJ, и и с я тем, что, с целью увеличения точности и определения знака девиации сопротивления, введены переключатель, два дополнительных резистора и схема равнозначности, вход которой соединен с выходом нульоргана и триггером знака, а ее выход подсоединен к тактовому входу триггера управления счетчиком н ключом, причем к суммирующим и вычитающим входам интегратора подведены два дополнительных резистора и переключатель, управляемый дешифратором.

ti iA I ts

Т,

иг .2

Фиг.з

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель температуры | 1986 |

|

SU1364910A1 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| Цифровой омметр | 1983 |

|

SU1129553A2 |

| Цифровой измеритель температуры | 1984 |

|

SU1224609A1 |

| Способ цифрового измерения девиации сопротивления | 1973 |

|

SU479054A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1569590A1 |

| Цифровой измеритель температуры | 1985 |

|

SU1303849A1 |

| Низкочастотный цифровой фазометр | 1990 |

|

SU1784924A1 |

| Цифровой измеритель температуры | 1984 |

|

SU1242725A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1560987A1 |

Авторы

Даты

1975-07-15—Публикация

1973-04-27—Подача