1

Способ цифрового измерения девиации сопротивления может быть применен для построения цифровых процентных омм етров, которые используются для определения разброса от поминала резисторов, выпускаемых промышленностью, а также для построения цифровых измерителей девиации сопротивления или преобразуемых в нее неэлектрических величии.

Известные цифровые измерители девиации сопротивления построены по методу двухтактного интегрирования и позволяют получить результат измерения с высокой точностью. Для этого необходимо производить преобразование в два этапа: сначала девиацию сопротивления в напряжение, а затем - напряжение в цифровой код известным методом двухтактного или трехтактного интегрирования. Это усложняет устройство измерения и увеличивает погрешность преобразования.

Цель изобретения - повышение точности измерений и обеспечение возможности выбора удобного масштаба преобразования с учетом определения знака девиации сопротивления.

Это достигается тем, что по предлагаемому способу длительность второго такта выбирают равНой длительности первого такта и дополнительно вводят третий такт интегрирования, в течение которого на вход интегратора подают падение папряжения от упомянутого тока на резисторе с образцовым сопротивлением, уменьшенным в маоштабный коэффициент раз, |Причем длительность третьего такта ограничивают временем, в течение которого выходное напряжение интегратора уменьшается до нуля, а в качестве результата измерения используют кодированное отношение длительности третьего такта к длительности одного из двух первых тактов.

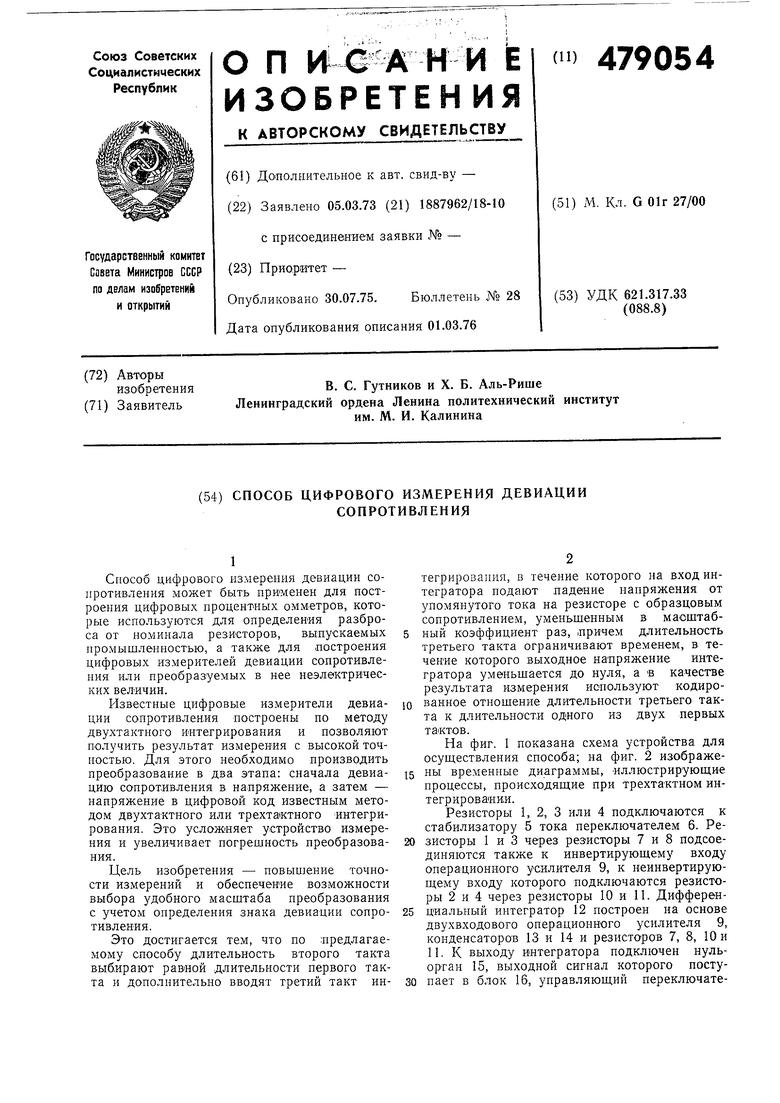

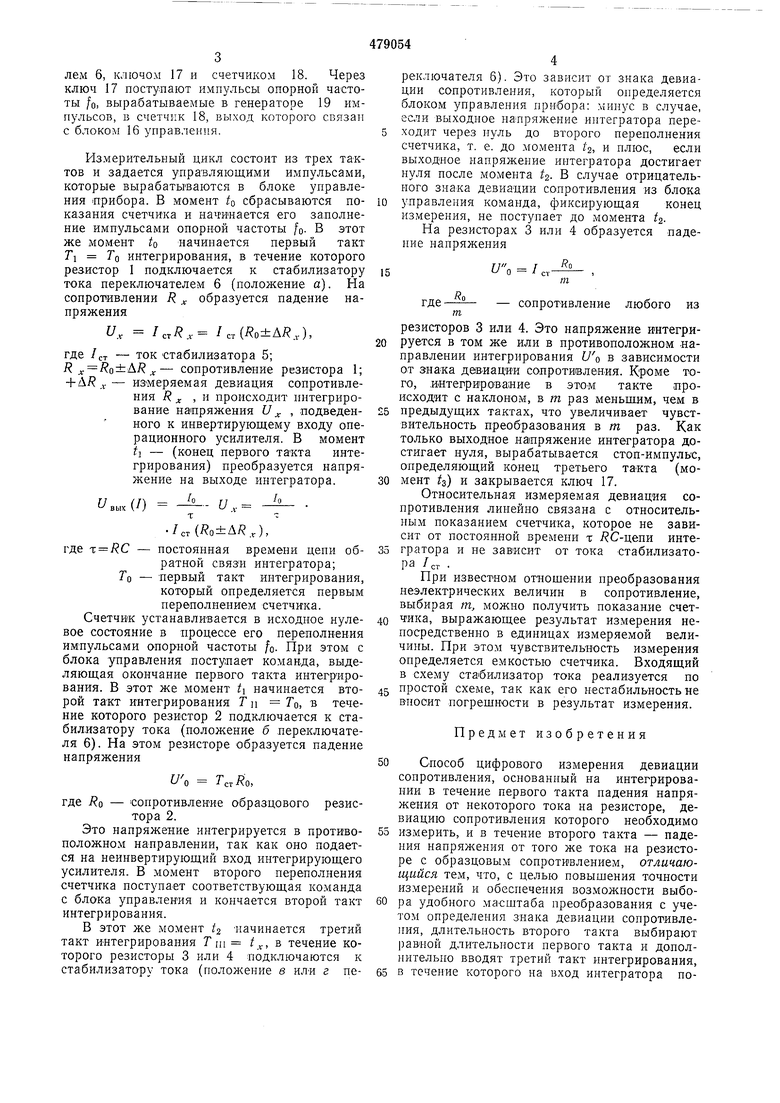

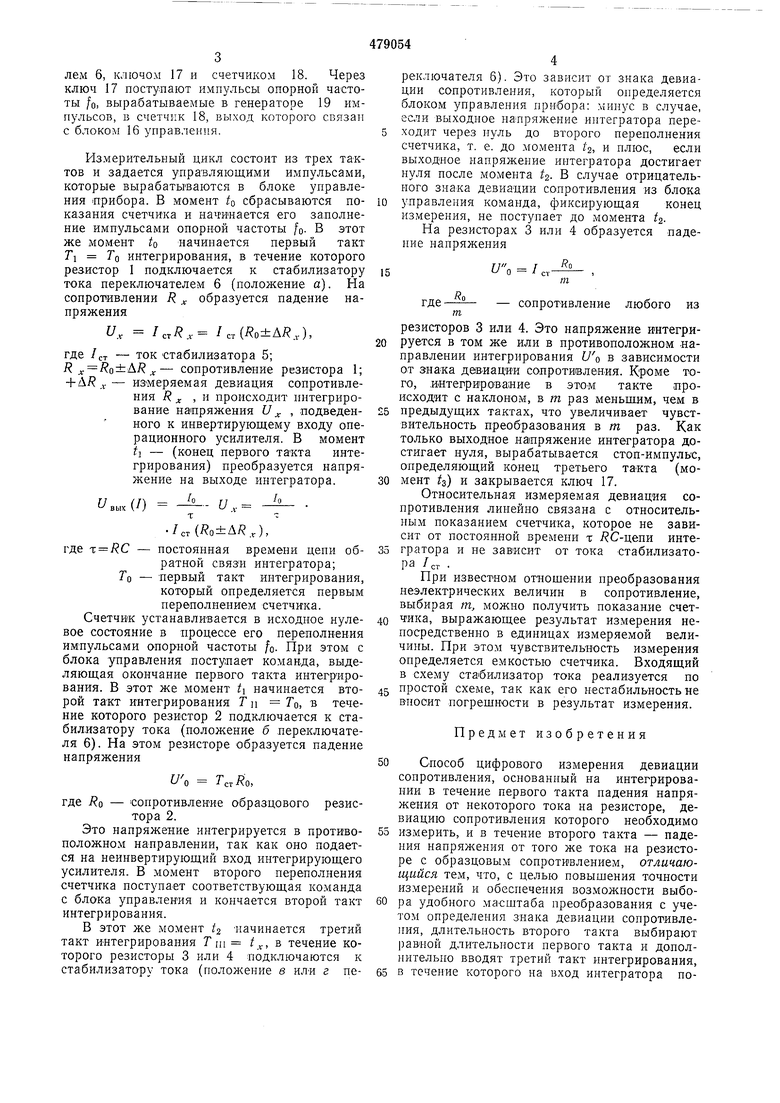

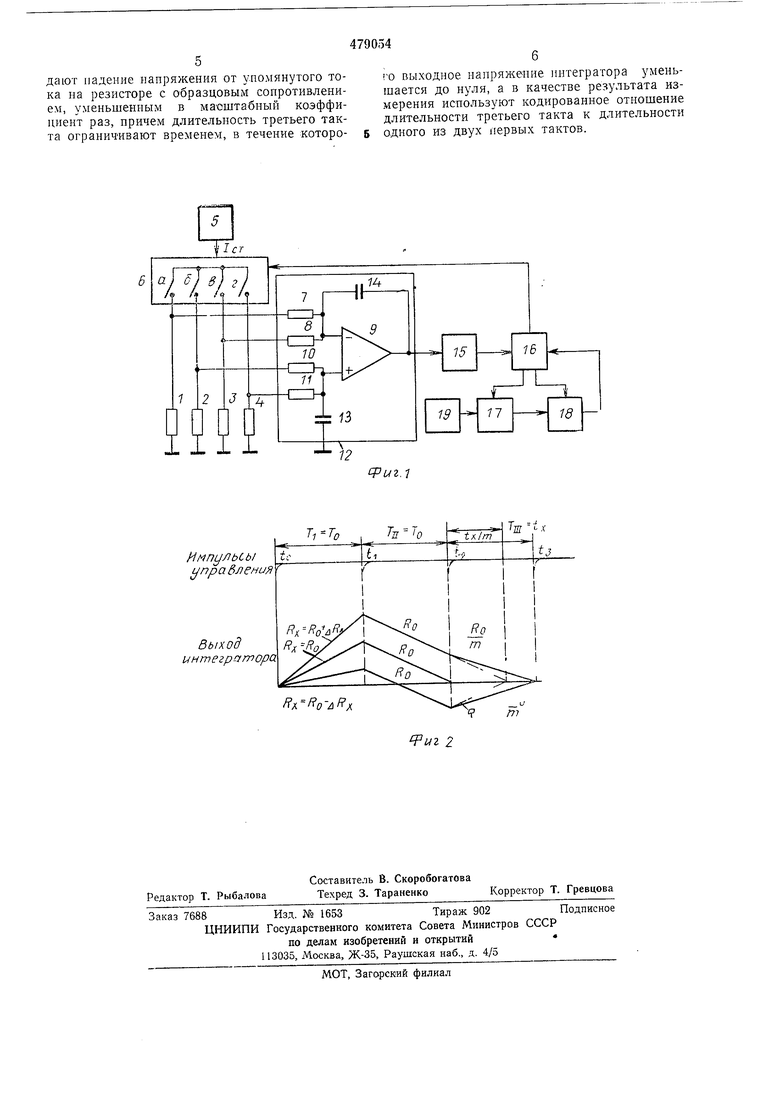

На фиг. 1 показана схема устройства для осуществления способа; на фиг. 2 изображены временные диаграммы, иллюстрирующие процессы, происходящие при трехтактном интегрировании.

Резисторы 1, 2, 3 или 4 подключаются к стабилизатору 5 тока переключателем 6. Резисторы 1 и 3 через резисторы 7 и 8 подсоединяются также к инвертирующему входу операционного усилителя 9, к неинвертирующему входу которого подключаются резисторы 2 и 4 через резисторы 10 и 11. Дифференциальный интегратор 12 построен на основе двухвходового операционного усилителя 9, конденсаторов 13 и 14 и резисторов 7, 8, 10 и 11. К выходу интегратора подключен нульорган 15, выходной сигнал которого поступает в блок 16, управляющий переключателеи 6, ключом 17 и счетчиком 18. Через ключ 17 поступают импульсы опорной частоты fo, вырабатываемые в генераторе 19 импульсов, в счетчик 18, выход которого связан с блоком 16 управления.

Измерительный цикл состоит из трех тактов и задается управляющими импульсами, которые вырабатываются в блоке управления прибора. В момент о сбрасываются показания счетчика и начищается его залолнение импульсами опорной частоты fo- В этот же момент to начинается первый такт TI TO интегрирования, в течение которого резистор 1 подключается к стабилизатору тока переключателем 6 (положение а). На сопротивлении R образуется падение напряжения

и,, /ст№±А/.,),

где /ст - ток -стабилизатора 5;

R. сопротивление резистора 1;

+ 4/.v- измеряемая девлация сопротивления R , и происходит интегрирование напряжения U . , подведенного к инвертирующему входу операционного усилителя. В момент ti - (конец первого такта интегрирования) преобразуется напряжение на выходе интегратора.

/о

A т

f/Bb,x(/)

- и,

.I,,,,},

где T: RC - постоянная времени цепи обратной связи интегратора; Го - первый такт интегрирования, который определяется первым переполнением счетчика. Счетчик устанавливается в исходное нулевое состояние в процессе его переполнения импульсами опорной частоты /о- При этом с блока управления поступает команда, выделяющая окончание первого такта интегрирования. В этот же момент ti начинается второй такт интегрирования Т п - То, в течение которого резистор 2 подключается к стабилизатору тока (положение б переключателя 6). На этом резисторе образуется падение напряжения

/о ,

где RO - сопротивление образцового резистора 2.

Это напряжение интегрируется в противоположном направлении, так как оно подается на неинвертирующий вход интегрирующего усилителя. В момент второго переполнения счетчика поступает соответствующая ко.манда с блока управления и кончается второй такт интегрирования.

В этот же момент 2 начинается третий такт интегрирования Т т t,, в течение которого резисторы 3 или 4 подключаются к стабилизатору тока (положение в или г переключателя 6). Это зависит от знака девиации сопротивления, который определяется блоком управления прибора: минус в случае, если выходное напряжение интегратора переходит через нуль до второго переполнения счетчика, т. е. до момента /2, и плюс, если выходное напряжение интегратора достигает нуля после момента t-. В случае отрицательного знака девиа-ции сопротивления из блока

управления команда, фиксирующая конец измерения, не поступает до момента /2На резисторах 3 или 4 образуется падение напряжения

Ra

/, .. - - .

т

R

- сопротивление любого из

где

резисторов 3 или 4. Это напряжение интегрируется в том же или в противоположном направлении интегрирования Uo в зависимости от знака девиации сопротивления. Кроме того, ,и«нтегри1р:0Вание в этом такте происходит с наклоном, в т раз меньшим, чем в

предыдущих тактах, что увеличивает чувствительность преобразования в m раз. Как только выходное напряжение интегратора достигает нуля, вырабатывается стоп-импульс, определяющий конец третьего такта (мо.мент з) и закрывается ключ 17.

Относительная измеряемая девиация сопротивления линейно связана с относительным показанием счетчика, которое не зависит от постоянной времени т С-цепи интегратора и не зависит от тока стабилизатора /„ .

При известном отношении преобразования неэлектрических величин в сопротивление, выбирая т, можно получить показание счетчика, выражающее результат измерения непосредственно в единицах измеряемой величины. При этом чувствительность измерения определяется емкостью счетчика. Входящий в схему стабилизатор тока реализуется по

простой схеме, так как его нестабильность не Внооит погрешности в результат измерения.

Предмет изобретения

Способ цифрового измерения девиации сопротивления, основанный на интегрировании в течение первого такта падения напряжения от некоторого тока на резисторе, девиацию сопротивления которого необходимо

измерить, и в течение второго такта - падения напрял ения от того же тока на резисторе с образцовым сопротивлением, отличающийся тем, что, с целью повышения точности измерений и обеспечения возможности выбора удобного масштаба преобразования с учетом определения знака девиации сопротивления, длительность второго такта выбирают равной длительности первого такта и дополнительно вводят третий такт интегрирования,

в течение которого на вход интегратора подают падение напряжения от упомянутого тока на резисторе с образцовым сопротивлением, уменьшенным в масштабный коэффициент раз, причем длительность третьего такта ограничивают временем, в течение которого выходное напряжение интегратора уменьшается до нуля, а в качестве результата измерения используют кодированное отношение длительности третьего такта к длительности одного из двух первых тактов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель девиациии сопротивления | 1973 |

|

SU477365A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1560987A1 |

| Устройство для измерения температуры | 1979 |

|

SU773455A1 |

| ЦИФРОВОЙ ОММЕТР | 1993 |

|

RU2115130C1 |

| Цифровой измеритель параметров | 1977 |

|

SU702317A1 |

| Устройство для измерения температуры | 1977 |

|

SU690326A1 |

| Цифровой измеритель температуры | 1985 |

|

SU1278622A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

| Цифровой измеритель температуры | 1983 |

|

SU1116329A1 |

| Способ аналого-цифрового преобразования с весовым интегрированием и устройство для его реализации | 1981 |

|

SU953722A1 |

TI-TO

Импульсы упрабления

Вы код интегратора

fui 2

Авторы

Даты

1975-07-30—Публикация

1973-03-05—Подача