1

Предлагаемое изобретение относится к аналоговой вычислительной технике, точнее к области аналоговых заноминающих устройств, и может быть использовано в специализированных аналоговых вычислителях, контурах самонастройки с входной информацией в виде низкочастотных автоколебаний.

Известно заноминающее устройство, содержащее усилитель, накопитель, соединенный со входом усилителя, узлы заряда и разряда, входы которых соединеиы с выходом компаратора, а выходы их соединены со входом усилителя. Известны, также модификации схемы данного запоминающего устройства. Основными достоинствами комиараторных запоминающих устройств являются малый дрейф нулевого уровня и высокая точность при сравнительно простой и дешевой схеме усилителя, на вход которого подключен накопитель.

Однако у перечисленных ЗУ отсутствует ряд свойств, необходимых для применения их в контурах самонастройки. Одним из таких свойств является автоматический переход из режима запоминания в режим заииси при вх вых где УВХ - напряжение на входе ЗУ; бвых - напряжение на выходе ЗУ. При этом постоянная времени записи ЗУ должна быть неизменной и переходные процессы про.ходить с учетом начальных и конечных условий.

Вторым свойством является автоматический переход из режима хранения при бвх вых При этом постоянная времени хранения должна быть неизменной, отличающейся на порядок от постоянной времени записи, переходной процесс должен проходить с учетом начальных и конечных услоВИЙ.

С целью повышения быстродействия предлагается аналоговое запоминающее устройство, которое содержит генератор опорного напряжения, два сумматора и дополнительный компаратор, выход которого соединен со входом узла заряда, положительный вход дополнительного компаратора соединен с выходом одного сумматора, а отрицательный вход - с вы.ходом усилителя и с одним из

входов другого сумматора, другой вход этого сумматора соединен с генератором опорного напряжения и с одним из входов первого сумматора, другой вход второго сумматора подключен к входу устройства и к OTpniiaтельному входу компаратора, прпчем положительный вход этого компаратора соединен с выходом первого сумматора.

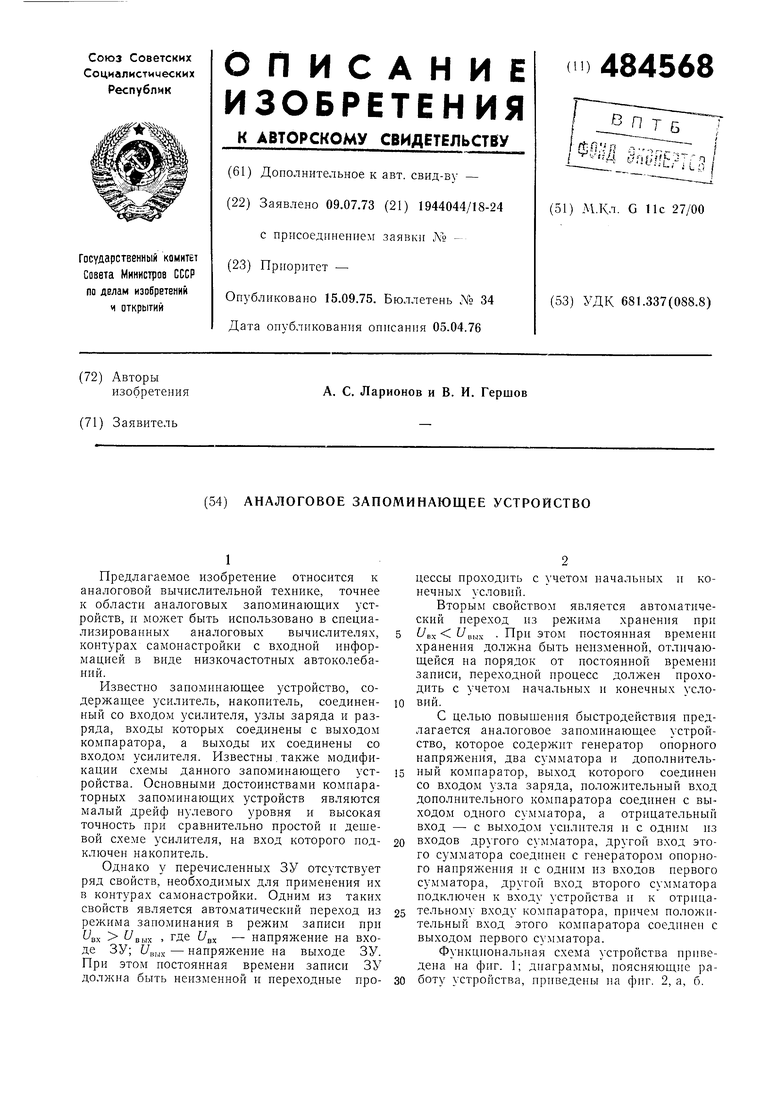

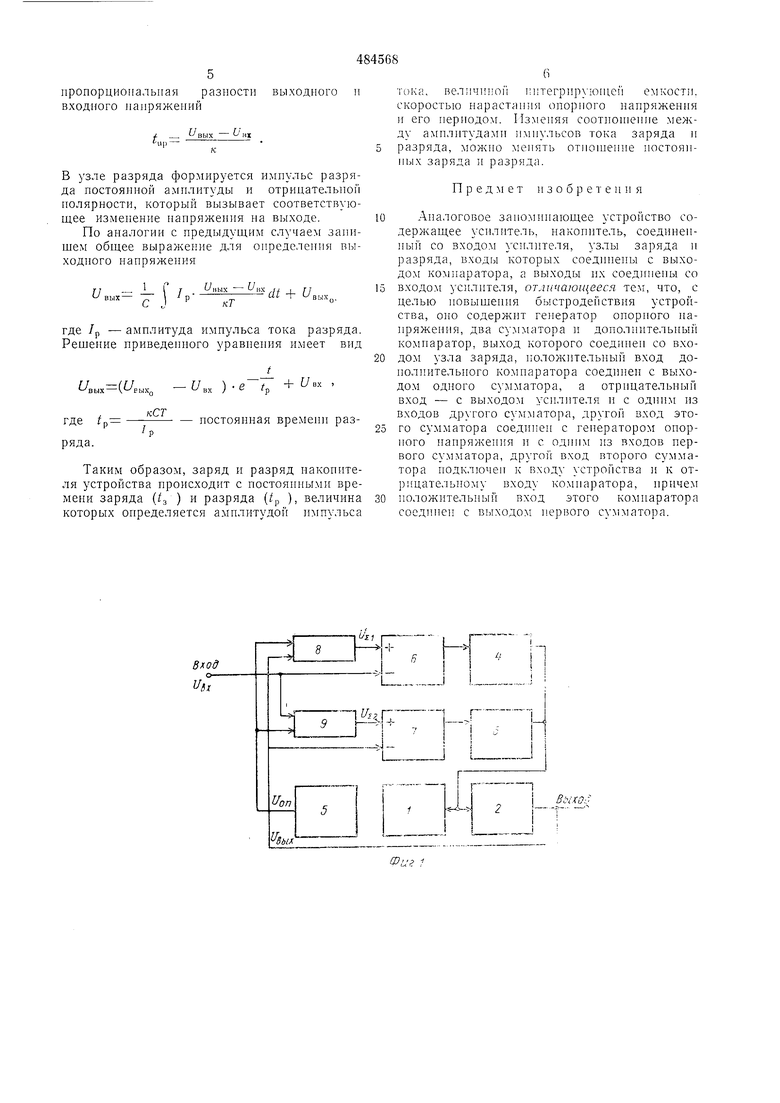

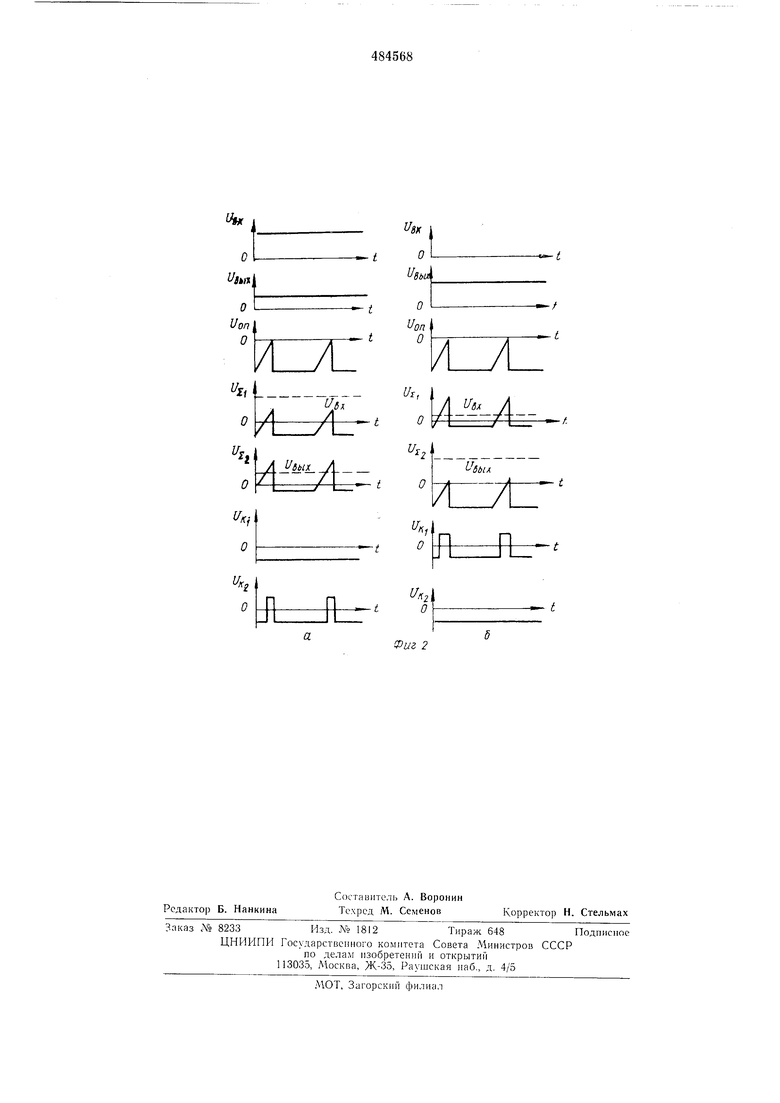

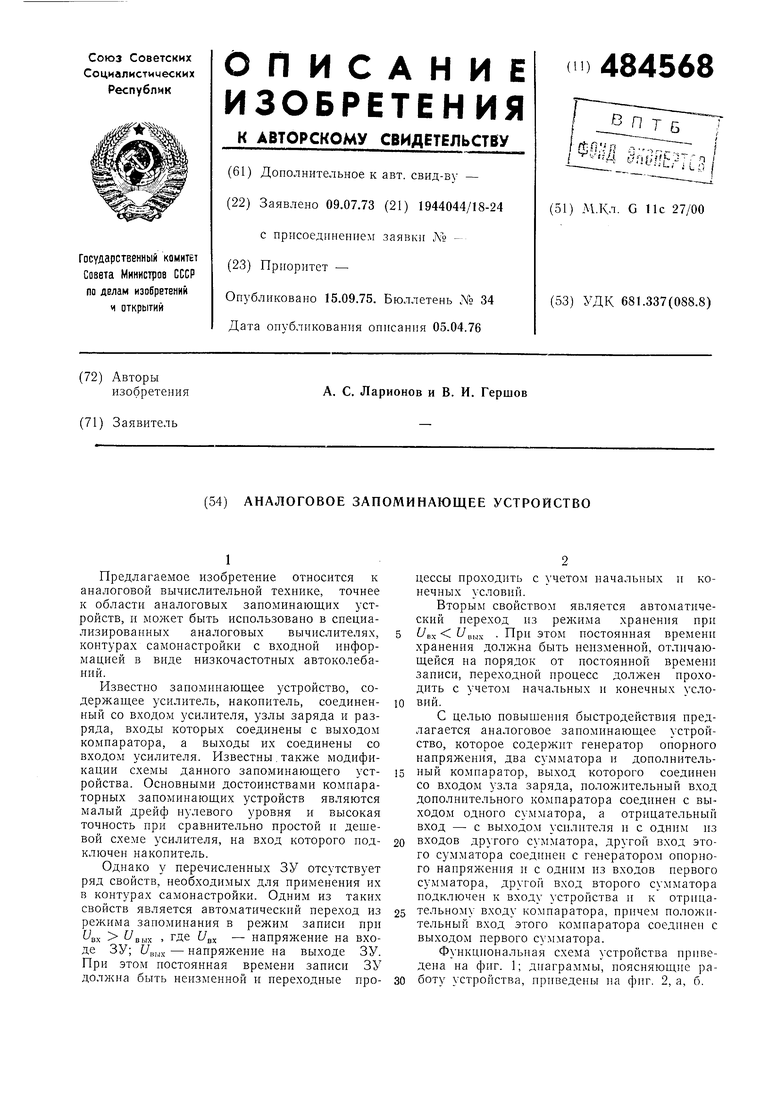

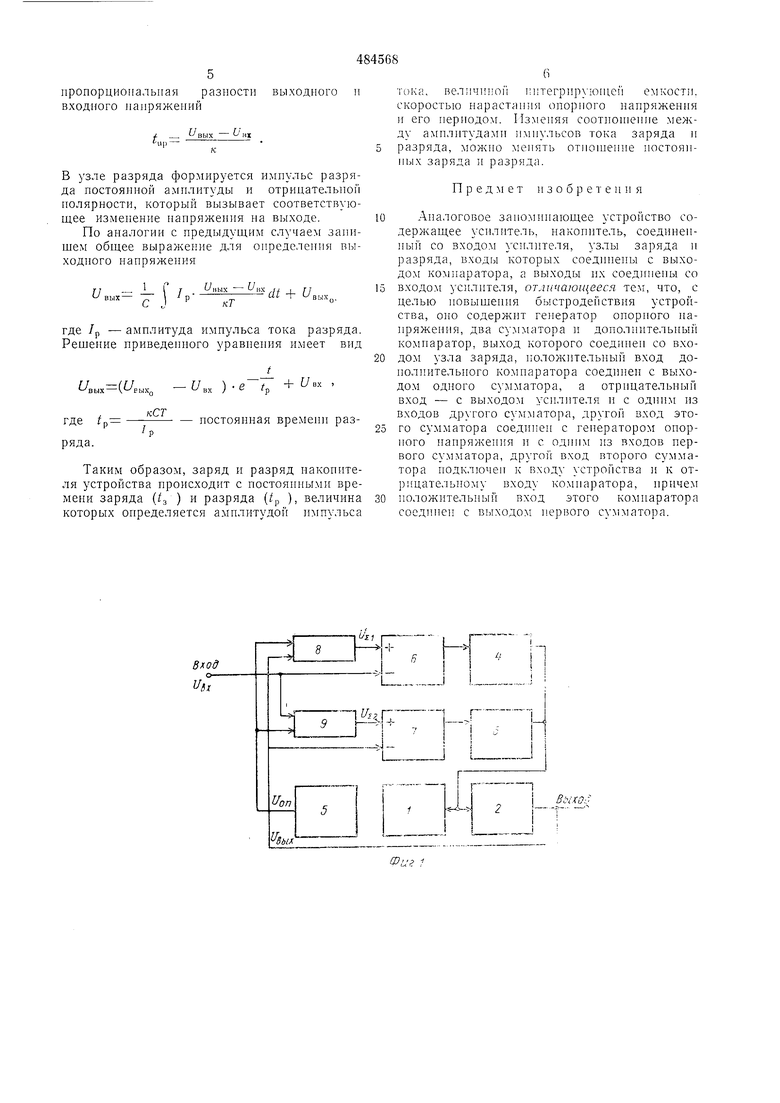

Функциональная схема устройства приведена на фиг. 1; диаграммы, поясняющие работу устройства, приведены па фиг. 2, а, б.

В состав аналогового запоминающего устройства, приведенного на фиг. 1, входят: паконнтель 1, нредставляюнип собой конденсатор с малыми токамн утечкн; усилитель 2 с входным сонротнв,тенцем 10°--10 Ом; узел заряда 3, представляюнип co6oi i токостабнлнзирующпй двухнолюснпк е ключом на входе; узел разряда 4 - токостабплизнрующнй двух 10Л1ОСник с ключом на входе; генератор 5 онорпого панря/кенн;г, формпруюнхпй однонолярные отрнцателыпле нмпульсы треугольной формы частоты 1000 Гц, скважностью 10; 6, 7 - компараторы, 8, 9 сумматоры.

Аналоговое заномннаюн1ее устройство работает следующим образом.

Для случая бвх вых диаграммы, яспяющне работу схемы, приведены фиг. 2а. Сигнал с генератора 5 опорного нряжеиня суммируется с сигналом /,,ых сумматоре 8 и постунает па положительный вход комнаратора 6, на отрицательный вход которого поступает сигнал /„х . Как видно из диаграммы фиг. 2 а, напряжепие на отрицательном входе компаратора 8 иоложительное и всегда больще амплитуды иаиряжеиия t/2 . В результате с выхода колша.ратора на унравлеппе ключом узла разряда ностунает ностояппое отрпиательнос нанряжеине и ключ все время разомкнут, ток с узла разряда не постунает на накоиите;п). С пл1ал /„,,суммируется с сигналом Lon на сумматоре 9 и с вглхода сумматора 9 ноступает н; положнтельньи вход кол1пара1-0)а 7. Ма отрнцательный вход комна 1атора 7 ностунает сигнал fy,;,,,;. . Как вндно нз днaгpa мы, сигнал У,,,.,х меньше амнлитуды сигнала Uj: па величину, равную f/cx- иых - В результате на выходе комнаратора 7 появляются положительные импульсы частоты 1000 Гц, длительность которых проиорннои.

нальна разности U

Положнтельные нмиульсы, ноетуиая па узел заряда, открывают ключ узла заряда. В результате на наконитель (конденсатор) начинают поступать импульсы тока иостоянной амплитуды, длительпость которых пронорциоиальиа разности t/B,; - (УВЫХ По мере заряда иакопительиой емкости разность /„х - t/вых умепьИJaeтcя. При t/px вых длительность импульсов заряда становится равной нулю, и ироцесс заряда прекращается. Для случая пх вых , как видно из днаграмм, поясняющих работу схемы, сигнал L,,,,,. , поступающнй на отрнцательный вход компаратора 7, всегда больше сигнала f/y.,, постунаюн1сго

па полож ггельный вход комнаратора 7. В результате е выхода комнаратора 7 на унравлснпс клJOЧO. узла заряда идет постоянное отрицательное напряженпе п ключ все время разо.гкпут. Ток с узла заряда не поступает иа наконительпый элемент. Сигнал t/ux , ностунающнй на отрицате.чьньн вх(х1 комнаратора 6, меньше сигиала Uy,, ностунающего на ноложительный вход комнаратора 6 на величину, равную f/ewx - вхВ результате е выхода ко.мнаратора 6 на управление ключом узла разряда ностунают

положительные импульсы, длительность которых пронорциональная разностп - DXПо мере разряда длнтельность ноложительных импульсов с компаратора 6 уменьшается. При f/,,,;-- L/в,,,х длительиость иоложительных нмпульсов с компаратора 6 станет 5авпой нулю.

Прнведем основные соотношения, характеризующие изменение напряжения иа выходе устройства в зависимости от соотношения

входного и выходного напряжений. В зависимости от соотношення входного н выходного панряжений реализуются два режима работы.

1. Режим заряда реализуется нри

ех вых . при этом компаратором 6 формируется длительность импульса, прямо пропорциональная разности входного и выходного напряжений.

- вых

где /г - скорость изменения онориого напряжения.

После узла заряда формируется имнульс тока иостоянной амнлнтуды длительностью t ,а положительной иоляриости, ностунающий в накопитель, вьшолияютций функции интегратора, напряжение с накопителя через

уснлнтель ноступает па выход устройства. Напряжение иа выходе устройства в этом случае оиисывается выражением

-1- Г

UKX - аых

j .dt+ и.

-

с

С

где С - величина интегрирующей емкости; /3 - амнлитуда импульса тока заряда; Т - период опорного напряжения; С/вых - напряжение на выходе устройства в момент переключения в режим заряда. Решнв приведенное линейиое дифференциальпое уравиепие отпосительио f/aux получим

f/оых (t/.x - в,„х„ ) (l - е )+ ,x,, , к с т

где /.j - - постоянная времени заряда.

J 3

Для упрощения получения конечного результата предполагается, что за время переходного процесса величина входного напряжения оставалась неизменной (реакция устройства на воздейетвие фуикции включения).

2. Режнм разряда реализуется при

пх при этом компаратором 6 формируется длительность импульса, прямо

пропорциональная разности выходного н входного на фяжений

вых их

J.

ир

в узле разряда формируется импульс разряда постоянной амплитуды и отрицате.тьнон полярности, который вызывает соответствующее изменение нанряження на выходе.

По аналогии с предыдущнм случаем запишем общее выражение для онределения выходного напряжения

- Г /р- t/,

С j кТ°где /р - амплитуда импульса тока разряда. Рещение приведепного уравнения имеет впд

tfjГ . р f + /вх

,, ВХ -р

кСТ

- постоянная времеии раз/,

Таким образом, заряд и разряд накопителя устройства происходит с постояпнымн времени заряда (/3 ) и разряда (/,, ), величина которых определяется амплитудой импульса

тока, величннон 1П тегрнруюгцеи емкости, скоростью нарастания опорного нанряжения II его периодом. Изменяя соотношенне между амплитудами импульсов тока заряда и разряда, можно менять OTiioHieniie постоянных заряда н разряда.

Предмет изобретения

Аналоговое запоминающее устройство содержащее уснлитель, накопитель, соединенный со входом усилителя, узлы заряда н разряда, входы которых соединены с выходом компаратора, а выходы их соедипены со

входом усилителя, отличающееся тем, что, с целью 1ювын1ення быстродействия устройства, оно содержит генератор опорного папряжения, два сумматора и дополнительный комнаратор, выход которого соединен со входом узла заряда, положительный вход дополнительного компаратора соединен с выходом одного сумматора, а отрнцательный вход - с выходом усилителя и с одинм нз входов другого сумматора, друго вход этого сумматора соединен с генератором опорного напряжения и с одним из входов первого сумматора, другой вход второго сумматора нодключеп к входу устройства и к отрицательному входу компаратора, причем

положительный вход этого комнаратора соединен с выходом н.ервого сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1559407A2 |

| ВСЕСОЮЗНАЯ ;П::Тг:гп10-1Ехн';-п^пр!'^'- 'ib;!:'!V.J . L i'i АI | 1971 |

|

SU293296A1 |

| Устройство для получения пилообразного напряжения | 1972 |

|

SU437972A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1015446A1 |

| Генератор трапецеидального сигнала | 1987 |

|

SU1432744A1 |

| Устройство для усреднения случайных импульсных сигналов | 1984 |

|

SU1218405A1 |

| Преобразователь аналогового сигнала в частоту с импульсной обратной связью | 1988 |

|

SU1587633A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1510087A1 |

| Аналого-цифровой интегратор | 1977 |

|

SU682908A2 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1552377A1 |

fe/i,

Us,

Авторы

Даты

1975-09-15—Публикация

1973-07-09—Подача