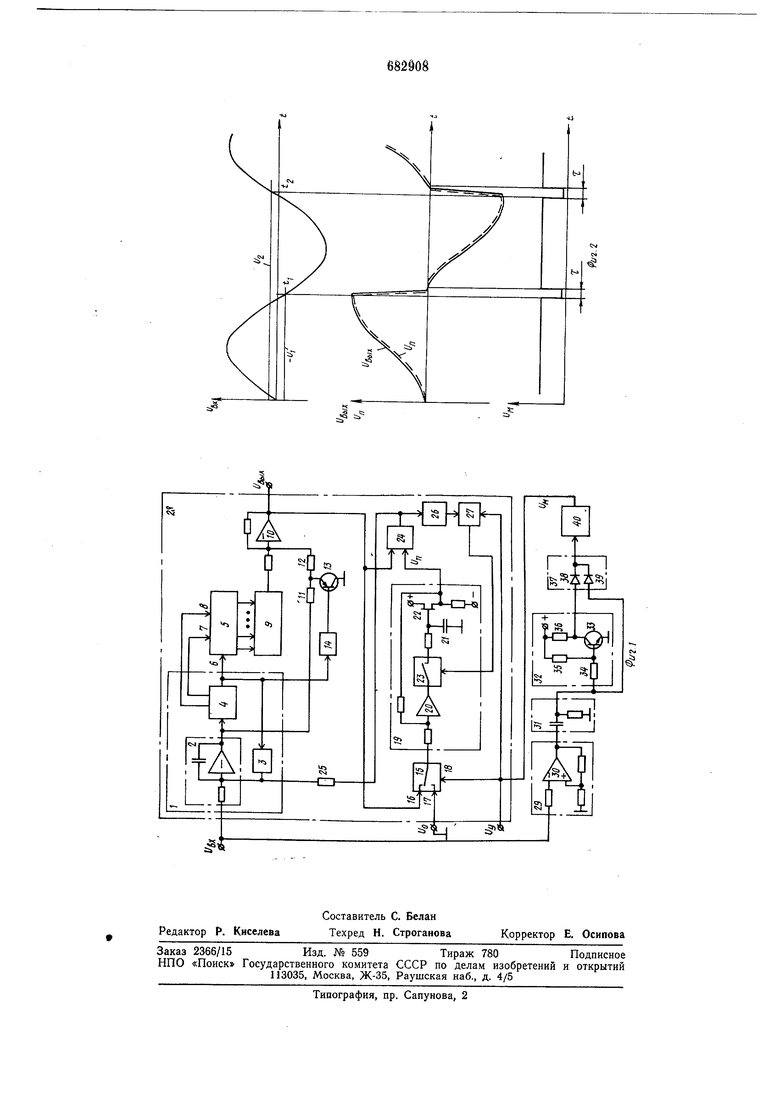

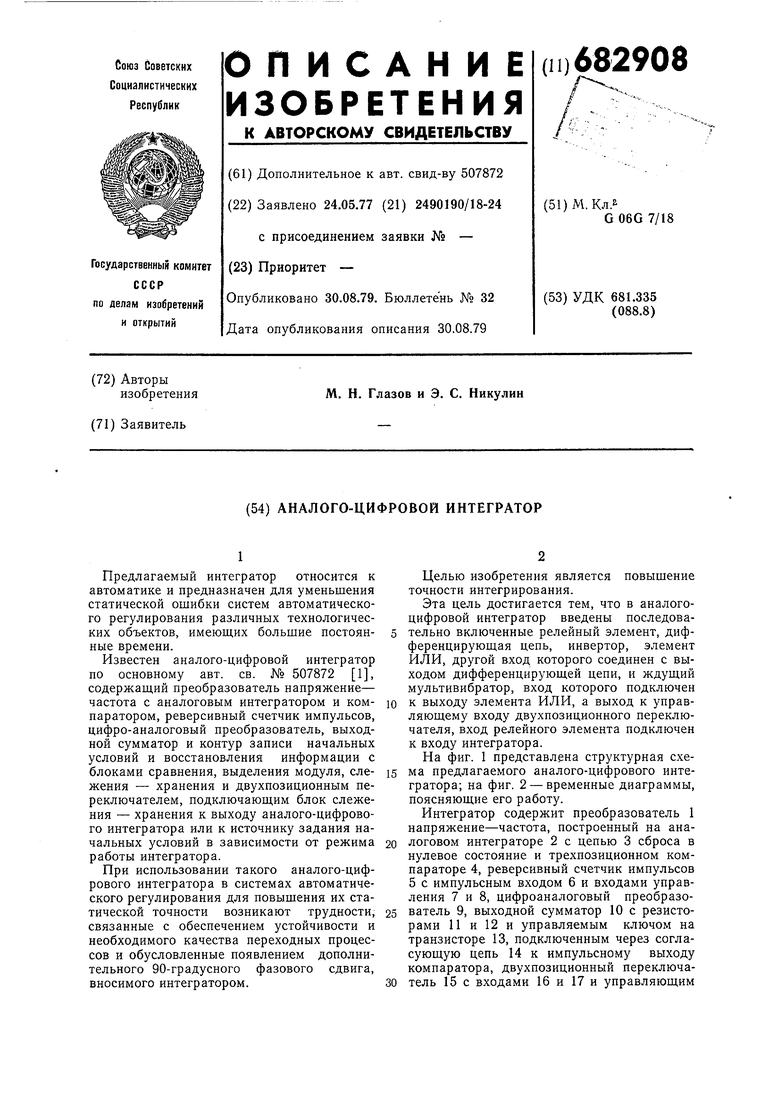

входом 18, блок слежения-хранения 19, содержащий усилитель 20, запоминающий конденсатор 21, истоковый повторитель на полевом транзисторе 22 и переключатель режима работы «слежение-хранение 23, трехпозиционный блок сравнения 24, резистор 25, блок выделения модуля 26 и логический элемент И-НЕ 27.

К аналого-цифровому интегратору 28 дополнительно подключены релейный элемент 29 на двухвходовом операционном усилителе 30, дифференцирующая цепь 31, инвертор 32 на транзисторе 33 и резисторах 34, 35 и 36, элемент ИЛИ 37 на диодах 38 и 39 и ждущий мультивибратор 40. Выход ждущего мультивибратора 40 соединен с управляющим входом 18 двухпозиционного переключателя 15, а вход релейного элемента 29 подключен к входу интегратора. В качестве источника задания начальных условий (Uo) в предложенном устройстве используется шина нулевого потенциала (вход 17 двухпозиционного переключателя 15 соединен с шиной нулевого потенциала).

Работает аналого-цифровой интегратор следующим образом. При наличии входного сигнала 7в1 преобразователь напряжение- частота 1 генерирует импульсы с частотой, пропорциональной t/вх. Пусть, например, , тогда на потенциальных выходах трехпозиционного компаратора 4, соединенных с входами управления 7 и 8 реверсивного счетчика 5, устанавливаются напряжения, настраивающие счетчик на сложение импульсов. Кодовые комбинации, возникающие в счетчике, преобразуются цифро-аналоговым преобразователем 9 в возрастающее напряжение, поступающее на вход сумматора 10. Импульсы на счетном входе 6 реверсивного счетчика 5 возникают в моменты, когда напряжение на выходе аналогового интегратора 2 достигает уровня срабатывания компаратора 4, после чего под действием выходного сигнала компаратора осуществляется быстрый сброс (разряд емкости) аналогового интегратора 2. В результате компаратор 4 выключается и процесс заряда емкости под действием f/вх повторяется. Поэтому за каждый период работы преобразователя 1 в счетчике 5 фиксируется приращение интеграла напряжения t/вх, т. е. имеет место квантование интеграла входного напряжения 17вх по уровню.

Для устранения погрешности квантования в схеме осуществляется суммирование выходного сигнала цифро-аналогового преобразователя 9 с выходным сигналом аналогового интегратора 2 с помощью сумматора 10. Устранение всплесков напряжения на выходе аналого-цифрового интегратора, возникающих в момент сброса аналогового интегратора 2, достигается с помощью резисторов 11 и 12 и транзистора 13, база которого через согласующую цепь 14 подключепа к импульсному выходу компаратора 4, благодаря чему сумматор 10 отключается от аналогового интегратора 2 на время разряда его емкости.

При неизменном знаке t/вх релейный элемент 29 удерживается в одном из устойчиных состояний, поэтому сигнал на выходе дифференцирующей цепи 31 отсутствует, на обоих входах элемента ИЛИ 37 действуют нулевые сигналы и ждущий мультивибратор 40 находится в устойчивом состоянии, при котором на его выходе имеется сигнал логической единицы. В результате переключатель 15 устанавливается в положение, при котором выход аналого-цифрового интегратора подключен к входу блока слежения- хранения 19. Этот блок при отсутствии сбоев счетчика 5 работает врелсиме слежения за выходным напряжением интегратора УВЫХ. Действительно, в режиме слежения на входах трехпозиционного блока сравнения 24 действуют практически равные напряжения Un и f/вых и выходные сигналы блоков сравнения 24 и выделения модуля 26 равны нулю. Поэтому на выходе логического элемента И-ПЕ 27 возникает единичный сигнал, поддерживающий переключатель 23 в замкнутом состоянии, что соответствует режиму слежения блока 19. Отметим, что в этом случае блок сравнения 24 не влияет на работу преобразователя «напрялсения-частота 1, т. к. ток через резистор 25 равен нулю.

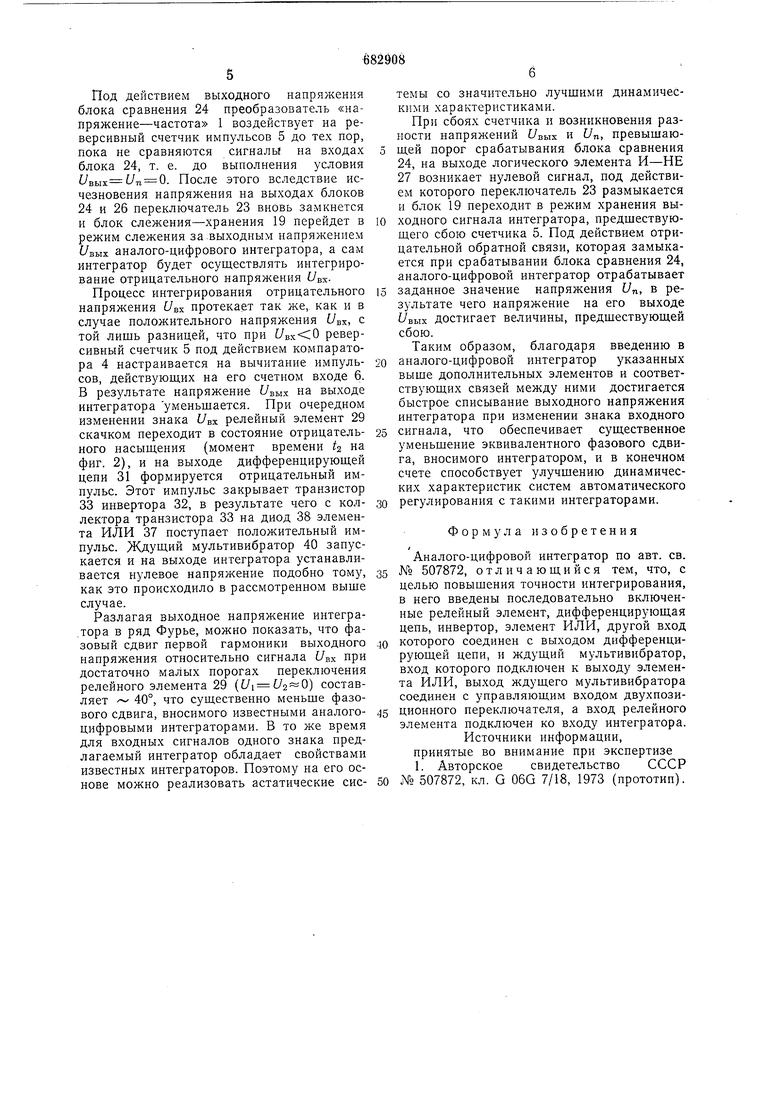

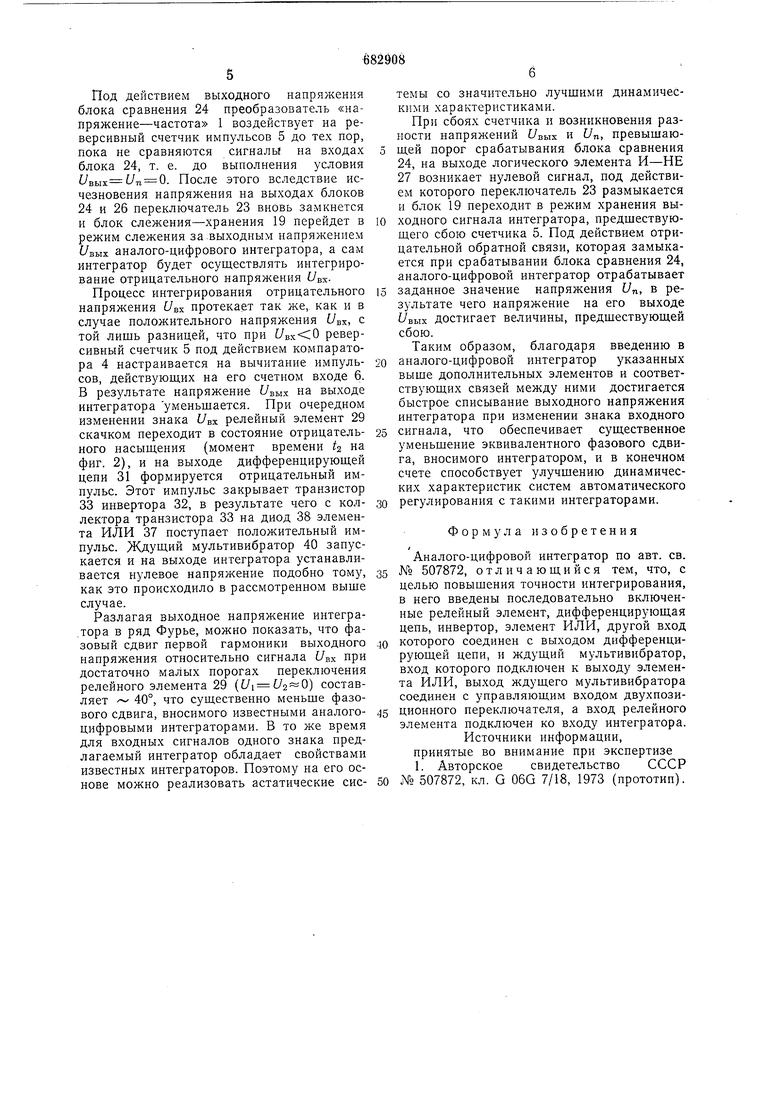

Рассмотрим теперь работу аналого-цифрового интегратора при изменении знака напряжения 6вх. В момент времени i (см. временные диаграммы на фиг. 2), когда /7вх достигает порога переключения t/i релейного элемента 29, последний скачком переходит в состояние положительного насыщения и на выходе дифференцирующей цепи 31 возникает положительный импульс, запускающий через схему ИЛИ 37 ждущий мультивибратор 40. На выходе ждущего мульти-, вибратора формируется импульс длительностью т (логический нуль), под действием которого элемент И-НЕ 27 вырабатывает единичный сигнал независимо от состояния блока сравнения 24. Поэтому блок слежения-хранения 19 остается в режиме слежения в течение времени задержки мультивибратора 40. При этом переключатель 15 переводится в положение, при котором к входу блока 19 подключается шина с нулевым потенциалом. В результате на выходе блока слежения-хранения 19 устанавливается нулевое напряжение (). Одновременно аналого-цифровой интегратор переходит в режим слежения за сигналом Un, поскольку из-за неравенства сигналов Un и t/вых блок сравнения 24 через резистор 25 замыкает контур отрицательной обратной связи, включающий в себя аналого-цифровой интегратор.

Под действием выходного напряжения блока сравнения 24 преобразователь «напряжение-частота 1 воздействует на реверсивный счетчик импульсов 5 до тех пор, пока не сравняются сигналы на входах блока 24, т. е. до выполнения условия 0. После этого вследствие исчезновения напряжения на выходах блоков 24 и 26 переключатель 23 вновь замкнется и блок слежения-хранения 19 перейдет в режим слежения за-выходным напряжением аналого-цифрового интегратора, а сам интегратор будет осуществлять интегрирование отрицательного напряжения t/ex.

Процесс интегрирования отрицательного напряжения С/вх протекает так же, как и в случае положительного напряжения t/вх, с той лишь разницей, что при реверсивный счетчик 5 под действием компаратора 4 настраивается на вычитание импульсов, действующих на его счетном входе 6. В результате напряжение t/вых на выходе интегратора уменьщается. При очередном изменении знака t/вх релейный элемент 29 скачком переходит в состояние отрицательного насыщения (момент времени 2 на фиг. 2), и на выходе дифференцирующей цепи 31 формируется отрицательный импульс. Этот импульс закрывает транзистор 33 инвертора 32, в результате чего с коллектора транзистора 33 на диод 38 элемента ИЛИ 37 поступает положительный импульс. Ждущий мультивибратор 40 запускается и на выходе интегратора устанавливается нулевое напряжение подобно тому, как это происходило в рассмотренном выше случае.

Разлагая выходное напряжение интегра.тора в ряд Фурье, можно показать, что фазовый сдвиг первой гармоники выходного напряжения относительно сигнала t/вх при достаточно малых порогах переключения релейного элемента 29 ( - 0) составляет 40°, что существенно меньше фазового сдвига, вносимого известными аналогоцифровыми интеграторами. В то же время для входных сигналов одного знака предлагаемый интегратор обладает свойствами известных интеграторов. Поэтому на его основе можно реализовать астатические сиетемы со значительно лучшими динамическими характеристиками.

При сбоях счетчика и возникновения разности напряжений /вых и L/n, превышающей порог срабатывания блока сравнения 24, на выходе логического элемента И-НЕ 27 возникает нулевой сигнал, под действием которого переключатель 23 размыкается и блок 19 переходит в режим хранения выходного сигнала интегратора, предществующего сбою счетчика 5. Под действием отрицательной обратной связи, которая замыкается при срабатывании блока сравнения 24, аналого-цифровой интегратор отрабатывает заданное значение напряжения Un, в результате чего напряжение на его выходе вых достигает величины, предшествующей сбою.

Таким образом, благодаря введению в аналого-цифровой интегратор указанных выше дополнительных элементов и соответствующих связей между ними достигается быстрое списывание выходного напряжения интегратора при изменении знака входного сигнала, что обеспечивает существенное уменьшение эквивалентного фазового сдвига, вносимого интегратором, и в конечном счете способствует улучшению динамических характеристик систем автоматического регулирования с такими интеграторами.

Формула изобретения

i

Аналого-цифровой интегратор по авт. св. № 507872, отличающийся тем, что, с целью повышения точности интегрирования, в него введены последовательно включенные релейный элемент, дифференцирующая цепь, инвертор, элемент ИЛИ, другой вход которого соединен с выходом дифференцирующей цепи, и ждущий мультивибратор, вход которого подключен к выходу элемента ИЛИ, выход ждущего мультивибратора соединен с управляющим входом двухпозиционного переключателя, а вход релейного элемента подключен ко входу интегратора.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 507872, кл. G 06G 7/18, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой интегратор | 1979 |

|

SU813456A2 |

| Интегратор | 1978 |

|

SU748438A1 |

| Аналого-цифровой интегратор | 1980 |

|

SU866563A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Аналого-цифровой интегратор | 1973 |

|

SU507872A1 |

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

| Аналого-цифровой интегратор | 1987 |

|

SU1444832A1 |

| Программная следящая система | 1981 |

|

SU1108394A1 |

| Аналого-цифровой интегратор | 1982 |

|

SU1037280A1 |

| Устройство для отображения параметров импульса на экране осциллографа | 1984 |

|

SU1169011A1 |

Авторы

Даты

1979-08-30—Публикация

1977-05-24—Подача