Изобретение относится к области автоматики и вычислительной техники и может найти применение в автоматических системах управления процессами, гибридных вычислительных комплексах, информационно-измерительных системах, работающих от датчиков время-имтульсной, цифр01вой и аналоговой информации.

Известны квадратично-множительные преобразователи, содержащие операционный усилитель с усредняющей цепью обратной связи, блок нвадратичной цифровой управляемой проводимости, управляемые двухпозиционные ключи и прецизионные резистор и конденсатор, выполняющие квадратично-множительную операцию с входными величинами, заданньгми в ;виде напряжения постоянного тока, длительности .прямоугольного импульсного напряжения и двоичным кодом с выходом в гаиде напряжения постоянного тока.

Однако в таких преобразователях необходимо использовать дополнительный операционный усилитель и два дополнительных прецизианных резистора для исключения ошибки из-за взаимного влияния блока квадратичной цифровой управляемой проводимости на квадратичную время-импульсную управляемую проводимость.

С целью повыщения точности и упрощения схемы ,в предлагаемом устройстве блок квадратичной цифровой управляемой проводимости включен между одной из обкладок конденсатора и переключаюЩИМ контактом первого двухпозиционного управляемого ключа, другие .контакты которого соединены соответственно со входом операционного усилителя и переключающим контактом второго двухпозиционлого ключа, связанного другими контактами со входом устройства и шиной нулевого потенциала. Это позволяет одновременно использовать квадратичную цифровую управляемую проводимость в качестве прецизионного резистора квадратичной время-импульсной зшравляемой проводимости.

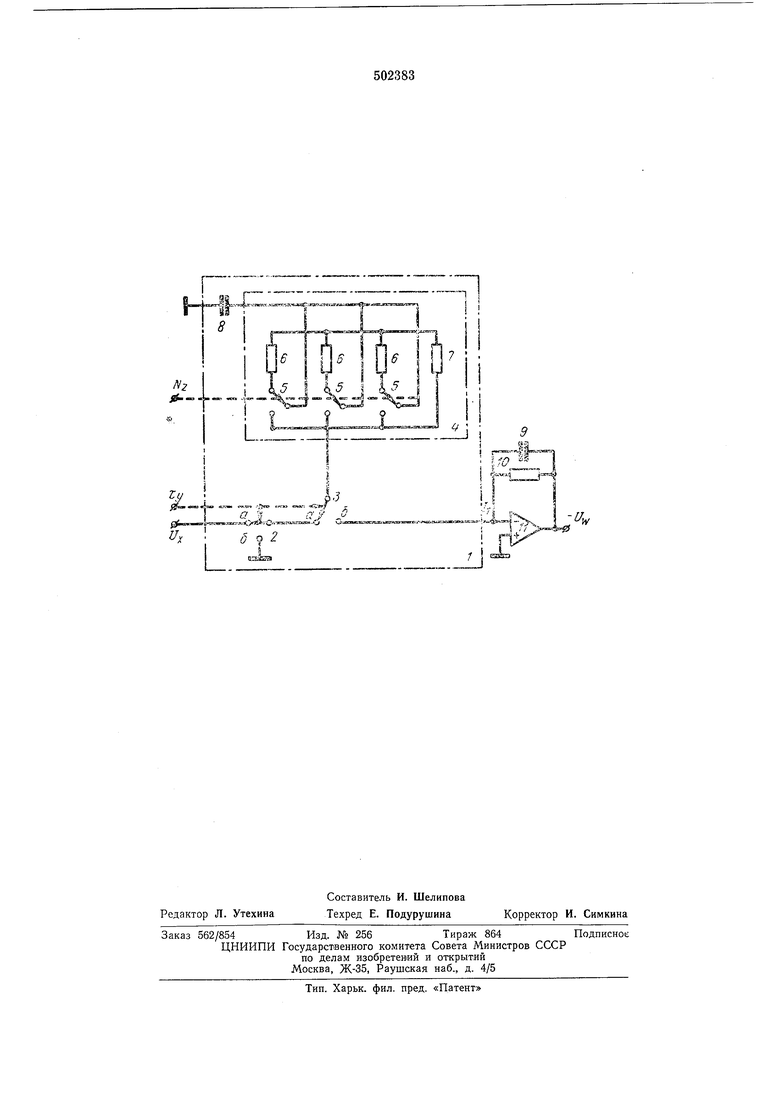

На чертеже приведена принципиальная схема преобразователя.

0,н выполнен в виде ком ненсационной схемы, входную цепь 1 которой образуют два двухпозиционных ключа 2 и 5, переключающие контакты которых управляются от прямоугольных .импульсов переменной длительности Ту, блок цифровой управляемой проводимости 4, состоящий из двухпозиционных ключей 5, управляемых от двоичного кода Л, разрядных прецизионных резисторов 6 и .прецизион.ного резистора 7, .проводимость которого Умакс const, и конденсатора 8.

Цепь обратной связи компенсационной схемы состоит из параллельно включенных конденсатора 9 и резистора 10, образующих

/ С-фильтр,/выделяющий среднее за период Т значение выходного .на-пряжения 11. Роль нульчиндикатора, автоматически поддержизающего баланс компенсационной схемы, зылолняет операционный усилитель 11. Входное яа-пряжение U подается на контакт а ключа 2. Контакт б ключа «3 соединен со входом усилителя 11. Выходное напряжение L,c снимается с выхода усилителя /). К шине нулевого потенциала подключены обкладки конденсатора 8 и контакт б ключа 2.

Баланс комшенсационной схемы осуществляется следующим образом. При поступлении кода NZ на управление разрядными двухПОЗИ1ЦИОННЫМИ ключами 5 квадратичная цифровая управляемая проводимость 4 изменяется -по закону

Я:

У, 0,5У,,акс 1 (1)

где Умакс const.

(Проводимость У4 включена между переключаю щнм контактом ключа 3 .и обкладкой конденсатора 8, поэтому при нахождении переключающего контакта ключей 2 и 5 в положении а в течение времени Ту происходит заэяд конденсатора 8 через проводимость Y, а при нахождении этих же контактов в течение времени Т-Ту в .положении б - разряд конденсатора 8.

Если выполняются условия практической неизменности величины проводимости У за время усталавки Туст среднего значения выходного напряжения U

dN dt

Г (2)

уст - 9л J

где п - число разрядов входного кода NZ, то среднее значение проводимости входной цели I (равно

Уг (3)

где Т - период .прямоугольного импульсного управляющего напряжения длительности т.

Учитывая выражение (1), получаем

Г-05Г И f -- Viri /

(4) ,0,5У„.кс|1 (л,,1 1 -J

Так как при -бала,нсеком1пенсад.ионной схемы среднее значение тока входной цепи и тока |Цбпи обратной связи равны между со.бой, то из урайнения баланса

150,5Умакс f/J 1 - (л/--Т1 h - f ;

yVMah-c / I 1

-{7()(5)

получают требуемую )множительно-квадра20 тичную характеристику преобразования

U.QbY,,,,,R,,( (

LV VMSKC / У

Формула и 3 о б р е т е.н и я

Квадратично-множ.ительный преобразователь, содержащий операционный усилитель с

усредняющей цепью обратной связи, блок квадратичной цифровой управляемой проводимости, двухпозиционные управляемые ключи и конденсатор, одна .из обкладок которого подключена к щнне нулевого потенциала, о тл и ч а ю щ и йс я тем, что, с целью повышения ТОЧНОСТ1И и упрощения схемы преобразователя, :блок квадратичной цифровой управляемой .проводимости между второй обкладкой конденсатора и переключающим контактом первого двух|Позиционного ключа, другие контакты которого соединены соответственно со входом операционного усилителя и переключающим контактом второго двухпозиционного ключа, связанного другими контактам.и со входом устройства и шиной нулевого потенциала.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРО-ШИРОТНОЕ МНОЖИТЕЛЬНО-КВАДРАТИЧНОЕУСТРОЙСТВО | 1973 |

|

SU430402A1 |

| Время-импульсное множительно- делительное устройство | 1979 |

|

SU773640A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1398099A1 |

| Аналоговое множительно-делительноеуСТРОйСТВО | 1979 |

|

SU805343A1 |

| Аналого-цифровой интегратор | 1981 |

|

SU1013978A1 |

| Цифро-аналоговый полиномиальный преобразователь | 1976 |

|

SU681554A1 |

| Цифро-аналоговый множительно- ТРигОНОМЕТРичЕСКий пРЕОбРАзОВАТЕль | 1978 |

|

SU822223A1 |

| Широтно-импульсное множительное устройство | 1980 |

|

SU868783A1 |

| Время-импульсное множительно-делительное устройство | 1976 |

|

SU608171A1 |

| Время-импульсное вычислительное устройство | 1983 |

|

SU1123038A1 |

Авторы

Даты

1976-02-05—Публикация

1974-06-25—Подача