(54) ШИРОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

I

Изобретение относится к аналбго-вой вычислительной технике, в частности к множительным устройствам.

Известны широтно-импульсные множительные устройства, в которых результат перемножения представляется в виде разности длительностей импульсов, содержащий интеграторы, компараторы и ключи .1.

Основной недостаток этих устройствсложность преобразования выходного сигнала в цифровой код.

Наиболее близким по технической сущности к предлагаемому устройству является широтно-импульсное множительное устройство, которое содержит широтно-импульсный модулятор, состоящий из последовательно соединенных интегратора, ко входу которого подключен источник входного сигнала, и компаратора, ко входу которого подключен другой источник входного сигнала, дополнительный компаратор и два ключа 2.

В этом множительном устройстве результат перемножения входных сигналов представляется в виде относительной разностц длительностей четырех разнополярных импульсов, что уменьшает точность преобразования из-за

увеличения погрешности дискретности и влияния фронтов выходных импульсов, а также уменьшает быстродейстЕие устройства.

Цель изобретения - повышение точности и быстродействия.

Поставленная цель достигается тем, что в широтно-импульсном множительном устройстве, содержащем источник первого сомножителя, широтно-импульсный модулятор, сос.тоящий из последовательно соединенных интегратора и основного компаратора, первый вход которого является входом второго сомножителя устройства, второй вход основного компаратора подключен к шине нулевого потенциала, а выход подключен к первому суммирующему входу интегратора, дополнительный компаратор, первый вход которого подключен к выходу интегратора, и два ключа, второй вход дополнительного комшаратора подключен к.шине нулевого потенциала, а выход - к управляющим

25 входам первого и второго ключей,

прямой выход источника первого сомножителя через первый ключ подключен ко второму суммирующему входу интегратора, инверсный выход источника

30 первого сомножителя через второй

ключ подключен к третьему суммирующему входу HFJTerpaTopa, выход основного компаратора является выходом устройства.

В результате выходной сигнал устройства формируется в виде двух азнополярЯнх примыкающих импульсов, относительная разность длительностей которых пропорциональна произведению .входных сигналов, что уменьшает погрешности дискретности при преобразовании и погрешности, связанные с длительностью фронтов. Быстродействие увеличивается за счет уменьшения в два раза минимально возможного периода измерения.

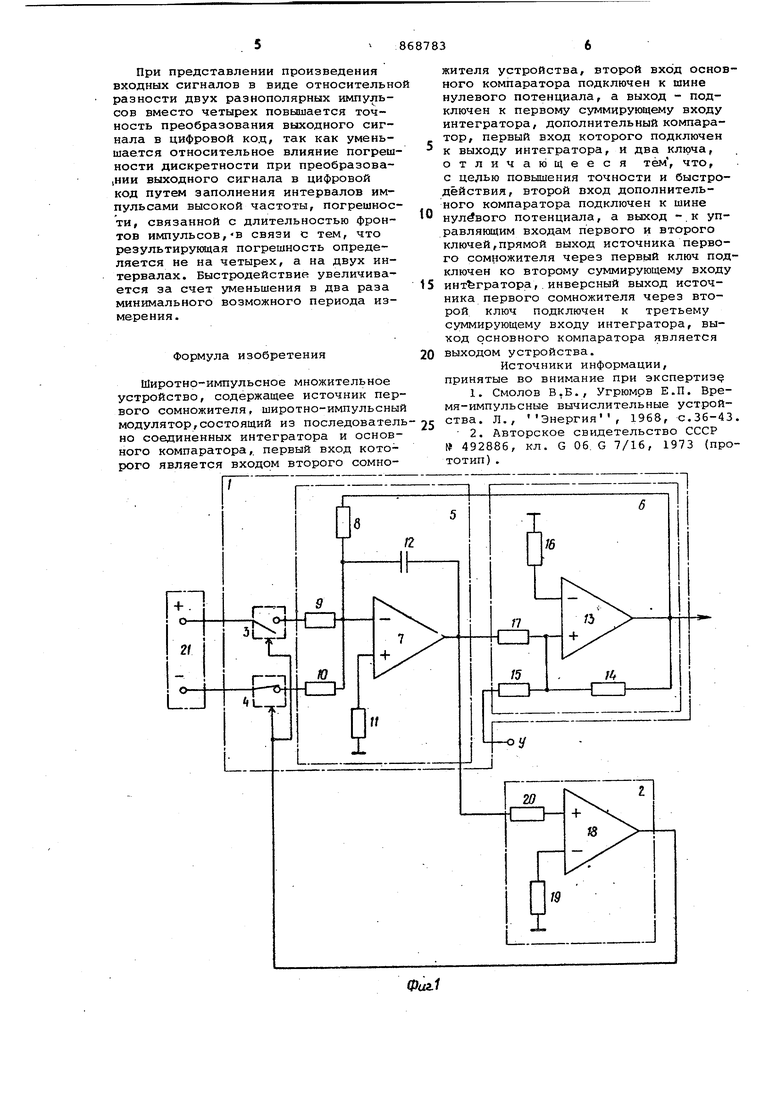

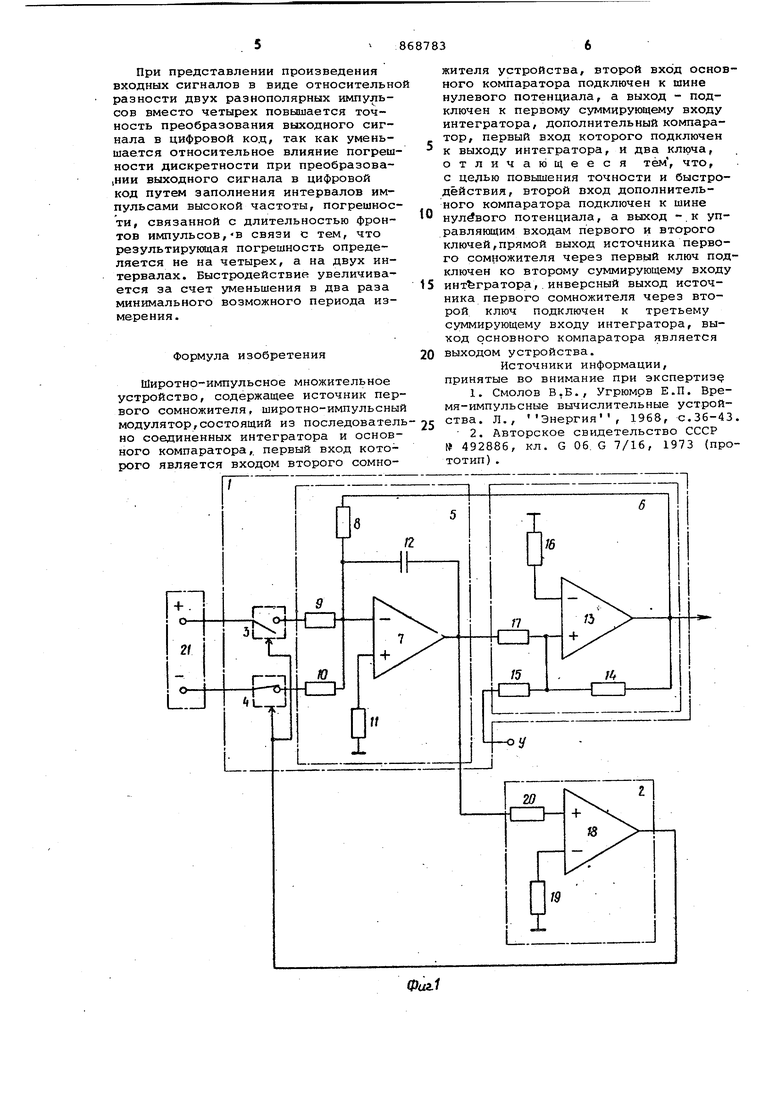

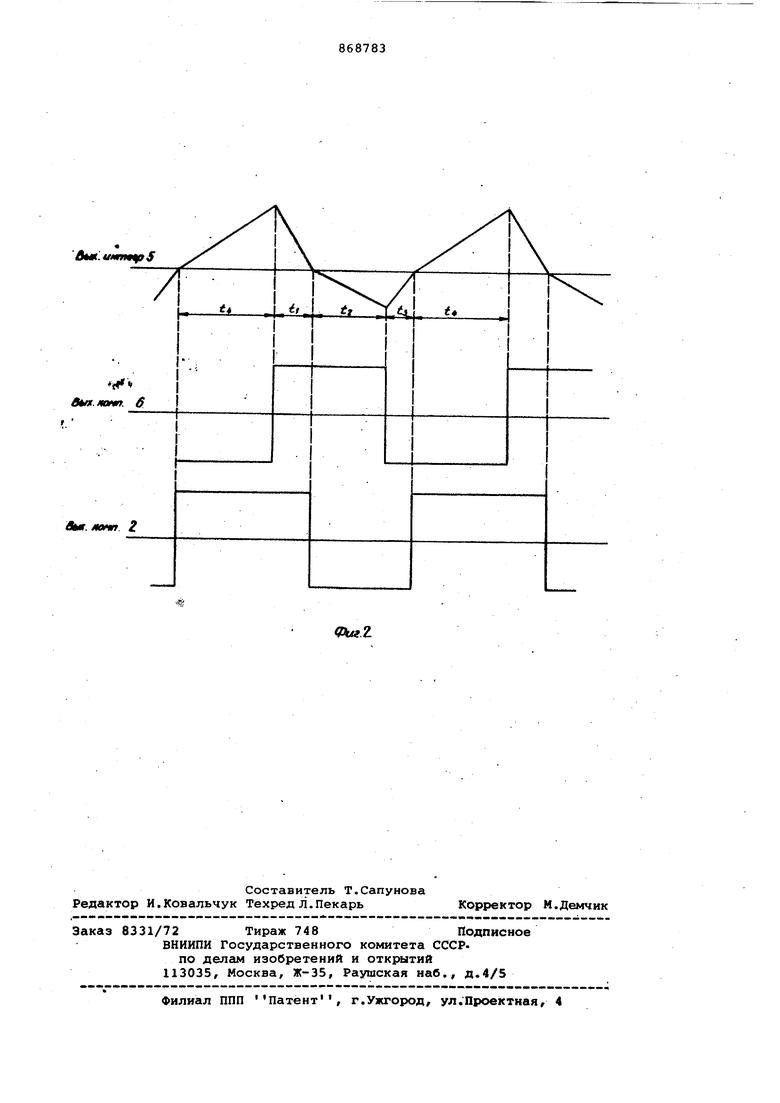

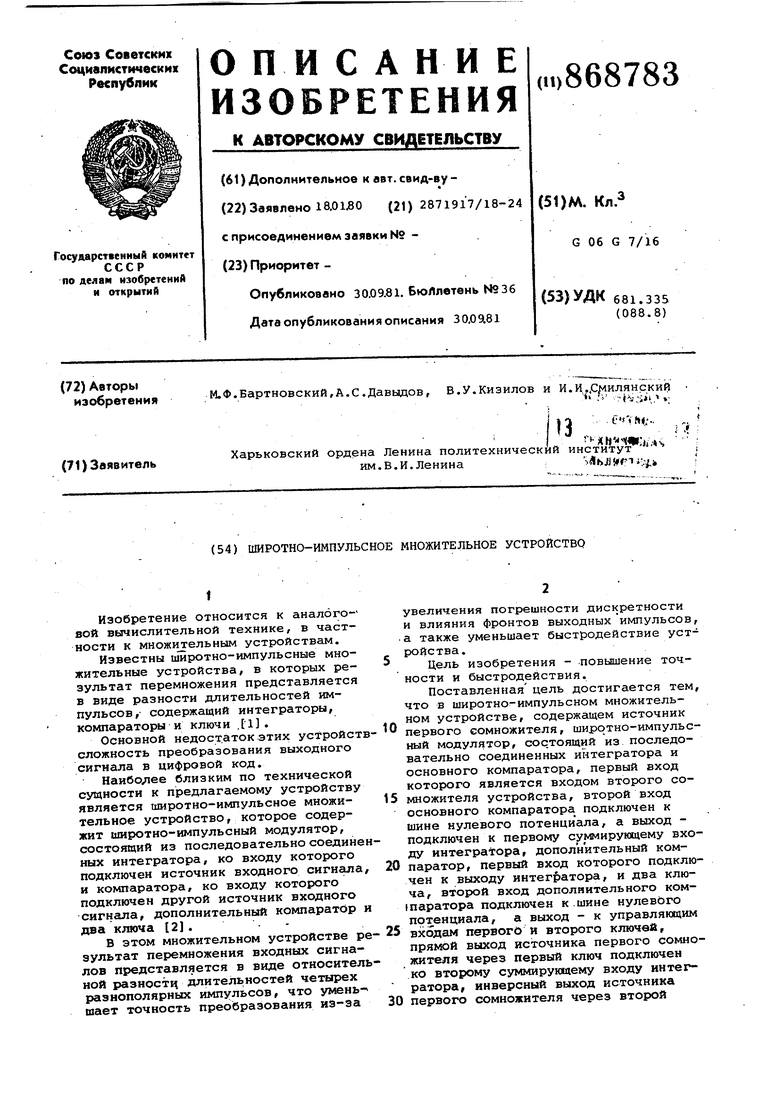

На фиг.1 приведена принципиальная схема широтно-импульсного множительного устройства; на фиг.2 - временные диаграммы работы множительного устройства.

Широтно-импульсное множительное устройство содержит широтно-импульсный модулятор 1, компаратор 2 и ключи 3 и 4 на полевых транзисторах с каналом различной проводимости. Широтно-импульсный модулятор 1 содержит интегратор 5 и основной компаратор 6. Интегратор 5 выполнен на операционном усилителе 7, к инвертирующему входу которого подключены первые выводы резисторов 8-10, вторы выводы которых образуют первый, второй и третий суммирующие входы ий-. тегратора соответственно, выход операционного усилителя б является выходом множительного устройства, неинвертирующий вход операционного усилителя 7 через резистор 11 подключен к шине нулевого потенциала, между инвертирующими входом и выходом операционного усилителя включен конденсатор 12, основной компаратор 6 выполнен на операционном усилителе 13 и резисторах 14-17, дополнительный компаратор, выполнен на операционном усилителе 18 и резисторах 19 и 20. Выход интегратора 5 подключен к первому входу компаратора 2, который переключается при переходе через ноль напряжения на выходе интегратора 5. Выходной сигнал компаратора 2 управляет работой ключей 3 и 4, работагадих в противофазе. Через ключи 3 и 4 ко второму и третьему суммирующим входам интегратора подключены выходы источника 21 парафазного вход ного сигнала первого сомножителя,

Широтно-импульсное множительное устройство работает следующим- образом.

При отсутствии входных сигналов интегратор 5 и компаратор б работают в автоколебательном режиме как релаксационный генератор. На выходе интегратора 5 формируется симметричное пилообразное напряжение, а на выходе компаратора 6 - напряжение прямоугольной формы. Дополнительный

компаратор 2 переключается при переходе через ноль напряжения на выходе интегратора 5. На выходе компаратора 2 формируется напряжение -прямоугольной формы, которое подается на управление ключами 3 и 4. При отсутствии входных сигналов относительная разность длительностей импульсов на выходе компаратора б равна нулю. Если на вход интегратора подан входной сигнал-сомножитель

0 tX, а на вход компаратора б сигналсомножитель У, то происходят следующие изменения в работе схемы. Скорость измерения напряжения на выходе интегратора будет равна

5

-4r(Uo-x)

при положительных напряжениях на выходах компараторов б и 2;

0

,-х)

при положительном напряжении на выходе компаратора 6 и отрицательном напряжении на выходе компарато5ра 2;

-feWo X)

при отрицательных напряжениях на выходах компараторов 6 и 2

-(Uo-X)

0

при отрицательном

- о напряжении на выходе компаратора б и положительном напряжении на выходе компаратора 2,

где TQ постояннная времени интегрирования ; Uo выходное напряжение компаратора б.

Длительности участков, на которых напряжение на выходе интегратора изменяется с постоянной скоростью (фиг..2) , равны

н-„

ГЦ

Uc-V . . Uc4Y

V-TOO ;

где УС; - порог срабатывания кЬмпаратора 6.

Длительности положительного V и отрицательного импульсов на выходе компаратора 6 равны у

: -ti -fcaiСа 5- -Ч

Относительная разность длительностей положительного и отрицательного Cij импульсов за период Т генерируемого напряжения

Г.Уа. , У

.D:/i.-t -fil -ti-ft4. UoUc,

Таким образом, относительная разность длительностей двух примыкающих импульсов на выходе компаратора 6 оказывается пропоргдаональной произведению входных сигналов. При представлении произведения входных сигналов в виде относительн разности двух разнополярных импульсов вместо четырех повышается точность преобразования выходного сигнала в цифровой код, так как уменьшается относительное влияние погреш ности дискретности при преобразова,нии выходного сигнала в цифровой код путем заполнения интервалов импульсами высокой частоты, погрешнос ти, связанной с длительностью фронтов импульсов,«в связи с тем, что результирующая погрешность определяется не на четырех, а на двух интервалах. Быстродействие увеличивается за счет уменьшения в два раза минимального возможного периода измерения. Формула изобретения Широтно-импульсное множительное устройство, содержащее источник пер вого сомножителя, широтно-импульсны модулятор,состоящий из последовател но соединенных интегратора и основного компаратора,, первый вход которого является входом второго сомножителя устройства, второй вход основного компаратора подключен к шине нулевого потенциала, а выход - подключен к первому суммирующему входу интегратора, дополнительный компаратор, первый вход которого подключен к выходу интегратора, и два ключа, отличающееся тем , что, с целью повышения точности и быстродействия, второй вход дополнительного компаратора подключен к шине нулевого потенциала, а выход - к управляющим входам первого и второго ключей,прямой выход источника первого сомножителя через первый ключ подключен ко второму суммирующему входу интегратора,.инверсный выход источника первого сомножителя через второй ключ подключен к третьему суммирующему входу интегратора, выход основного компаратора является выходом устройства. Источники информации, принятые во внимание при экспертизу 1. Смолов В.В., Угрюмрв Е.П. Время-импульсные вычислительные устройства. Л., Энергия, 1968, с.36-43. 2. Авторское свидетельство СССР № 492886, кл. G 06. G 7/16, 1973 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Широтно-импульсное множительное устройство | 1980 |

|

SU934493A1 |

| Широтно-импульсное множительное устройство | 1980 |

|

SU886009A1 |

| Время-импульсное множительное устройство (его варианты) | 1981 |

|

SU1013977A1 |

| Множительно-делительное устройство широтно-модулированных сигналов | 1983 |

|

SU1095196A1 |

| Электронный счетчик электроэнергии | 1979 |

|

SU866491A1 |

| Время-импульсное множительно-делительное устройство | 1982 |

|

SU1032459A1 |

| Множительно-делительное устройство | 1978 |

|

SU721828A1 |

| Многофункциональный широтно-импульсный модулятор | 1980 |

|

SU866729A1 |

| Широтно-импульсное множительное устройство | 1981 |

|

SU1015395A1 |

| Времяимпульсное множительное устройство | 1988 |

|

SU1642481A1 |

Авторы

Даты

1981-09-30—Публикация

1980-01-18—Подача