(54) РАСПРЕДЕЛИТЕЛЬ НА ТРАНЗИСТОРАХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Оптоэлектронный модуль | 1984 |

|

SU1274155A1 |

| Шкальный индикатор | 1990 |

|

SU1767339A1 |

| Линейный импульсный модулятор | 1989 |

|

SU1626362A2 |

| Устройство для отображения информации на газоразрядной индикаторной панели переменного тока | 1985 |

|

SU1295439A1 |

| Формирователь импульсов | 1979 |

|

SU819942A1 |

| Реверсивный распределитель импульсов | 1976 |

|

SU656209A1 |

| Устройство для запуска распределителяТЕлЕМЕХАНичЕСКОй СиСТЕМы | 1979 |

|

SU841003A1 |

| Шкальный индикатор напряжения | 1987 |

|

SU1552109A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В БИПОЛЯРНЫЙ КОД | 2002 |

|

RU2218660C2 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1979 |

|

SU855639A1 |

1

Изобретение относится к телемеханике.

Известны распределители на транзисторах по авт.св. №283292, содержащие мостовые импульсные элементы задержки в Каждой ячейке. Однако они имеют низкую помехоустойчивость при работе приемного и передающего распределителей с большими уровнями помех.

Цель изобретения - повышение помехоустойчивости.

Достигается это благодаря тому, что в распределитель на транзисторах введены схема совпадения, триггер и два ключевых транзистора, причем коллектор одного из них соединен с эмиттерами транзисторов нечетных ячеек, а также с первым входом схемы совпадения и через резистор с шино питания, а коллектор другого ключевого транзистора соединен с эмитаерами транзисторов четных ячеек, а также через резистор - с шиной питания и через диод в прямом направлении - с входом первой ячей:КИ, к которому через диод в обратном на/1равлении подключен выход триггера. Один lia входов этого триггера соединен с входом установки в ноль и подключен через соответствующие диоды к соогветс гиукпакм выходам всех нечетных ячеек, Ha4iriifiH с ;третьей, а второй вход триггера одключен к выходу схемы coвпaдef ня, другой вхол .которой подключен к входу синхронизации; кроме того, входы источника тактотзых импульсов подключены к базовым выводакг ключевых транзисторов, эмиттеры кспо(Я)1х

подсоединены к обшей шине.

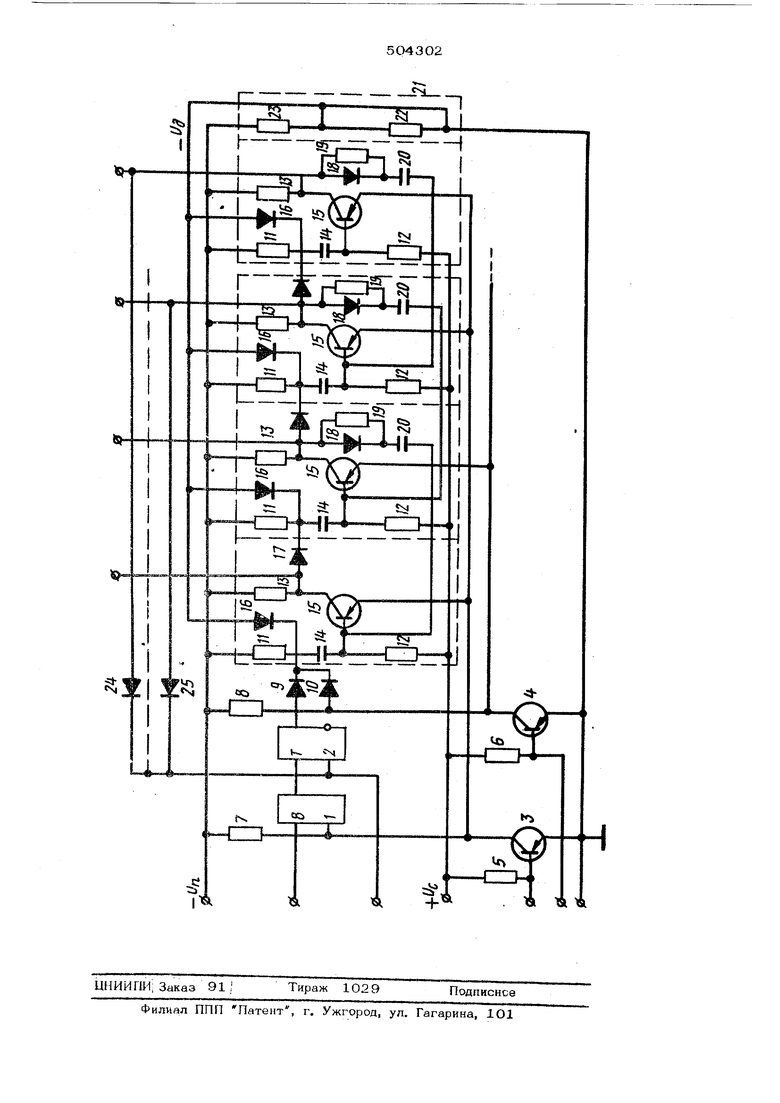

На чертеже представлена припиициальная схема устройства.

j Предлагаемое устройство содержит схе:му 1 совпадения, триггер 2, ключевые гранзисторы 3, 4, резисторы 5-8, диоды 9 и 10, ячейки, каждая из которых содержит резисторы 11-13, конденсатор 14, TIKIH;зистор 15, диоды 16-18, резистор 19, конденсаторы 2 О и 21, резисторы 22 и

:23, диоды 24, 25 и ячейки выполнены ч,- :мостовых импульсных элементах задержки, ;каждая из которых имеет времяпадамшул) |ветвь, образованную г1Оследовате;гьно cotvoi,ненными резистором 11 и конденсато()ок( Il;

базовый резистор 12, транзистор 15, пореключаюший 16 и развязывающий 17 диоды, Обшая ветвь моста импульсных мостовых эломантов выполнена в виде делителя напряжения из резисторов 22 и 2Э, включенного между коллекторной и нулево тинами питания. Между коллектором траиэисторя каждой ячейки распределителя и базой транзистора к.пждой предыдущей ячей ки включены цепочкн, содержащие последо вательно включенные диод 18 шунтирован ный резистором 19, и конденсатор 20. В исходном состоянии триггер 2 установлен а. нулевое состояние, при этом на анод 9 подан нулевой потенциал, запирающий диодно-резистивную схему совпадения и предотвращающий заряд конденсатора 14 в первой 5Г1ейке распределителя. Конденсаторы 14 остальных ячеек заряжены до .нaпpяжeF ия Ug общего делителя иппряження. Отрицательные прямоуголь ны, импульсы источника тактовых (продви гающих) импульсов поочередно открывают и закрывают ключев1 ю транзисторы 3 и 4. Однако сигналы на выходах распределителя отсутствуют, так как транзисторы 15 всех ячеек заперты положительным напряжением смешения Uc, подаваемым на их базы через рез 1сторы 12. На диоды 24, 25 с коллекторов запертых транзисторов подан высокий отрииа1ельный потенциал. Запуск распределителя производится подачей на вход схемы совпадения отрицательного импульса синхронизации (фази- ргдаание по циклам) в момент времени, ког да на коллкзкторе тр анзистора 3 присутствует высокий отрицательный потенциал, а гютеипиал нл коллекторе транзистора 4 близок к нулю. Импульс запуска, пройдя входную схему совпадения 1, переключает триггер 2 в единичное состояние, подготавливая диодно-резистивную схему совпадения для прохождения тактовых импульсов. При поступлении следующего тактового импульса (фазирование по импульсам) происходит смена потенциалов на гол лекторах ключевых транзисторов в результате чего с транзистора 4 на диод 10 по дается отрицательный импульс, открывающ диодно-розистивную схему совпадения, а

эмиттер первой ячейки распределителя оказывается подкл1(;ченным через переход коллектор-эмиттер открытого ключевого траизмстора 3 к нулевой шине питания. Конден- сатор 14 первой ячейки распределителя начинает заряжаться по цепи: нулевая шина питания, переход эмиттер-колдтектор транзистора 3, переход эмиттер-база транзистора IB, конденсатор 14, резистор 11,

вием надежной работы распределителя является выполнение условия, при котором время до заряда конденсатора 14 должно быть меньше длительности тактового импульса. Таким образом, при подаче импульса синхронизации фазирования по циклам и тактовых импульсов по pacnpeaej.nтелю продвигается положительный импульс, равный по длительности тактовому. щина коллекторного питания - 17 , При втом транзистор 15 первой ячейки переходит в режим насыщения и подает положительный импульс не разряд конденсатора следующей ячейки, который в свою очерець разряжается через упомянутые переходы транзисторов 3 и 15, развязываюиггШ диод 17, конденсатор 14 и резистор 12 второй ячейки. Так как постоянная времени цепи разряда выбирается значительно меньше постоянной заряда, то конденсатор 14 второй ячейки, разрядившись практически полностью, остается в этом состоянии до тех пор, пока открыт транзистор первой ячейки. I Пусть параметры мостового элемента задержки выбраны такими, что за время действия тактового импульса напряжение на конденсаторе 14 не достигает уровня опорного напряжения, подаваемого на переключающей диод 16. В этом случае длительность импульса на выходе нечетной ячейки распределителя будет равна длительности тактового . С подачей тактового импульса ;:снова происходит смена потенциалов на коллекторах ключевых транзисторов, импульс на выходе первой ячейки прекращается, а конденсатор 14 этой ячейки разряжается через открытый транзистор 4, диод 1О, резистор 12. Одновременно с этим начинается формирование выходного импульса второй ячейки и разряд конденсатора 14 третьей ячейки. Все зарядно-разрядные процессы во второй н третьей ячейках аналогичны описанному. По окочании тактового импульса конде юатор 14 второй ячейки продолжает заряжаться чероз резисторы 11 и 12 с относительно большей постоянной времени, однако транзистор этой же ячейки остается закрытым благодаря присутствию на его эмиттере запираю щего напряжения, снимаемого с коллектора закрытого ключевого транзистора, 4. Конденсатор 14 первой ячейки в этот момент .и в дальнейшем разряжен, так как диоднорезистиБная схема совпадения запирается положительными импульсами транзистора 4 и нулевым потенциалом триггера 2. Так предотвращается ложный запуск в пределах цикла. Необходимым и достаточным услоФ о р м у л я изобретения

Р|1г:пределитель на транзисторах по авт. св. №283292, отличающийся |Твм, что, с целью повьшвния помехоустойчивости, в него введены схема ссфпадения, триггер и два ключевых транзистора, прячем коллектор одного из них соединен с (эмиттерами транзисторов нечетных ячеек, а также с первым входом схемы совпадения и через резистор с шиной плтания, а коллектор другого ключевого транзнстора соединен с эмиттерами транзисторов четных ячеек, « также через резистор - с шиной питания и через диод в 11«11пг ь « ленки - с входом нерпой ячейки, к кспчфо-му через диод в обратном нвправпенки иоя ключен выход триггера, один на рхопст ко5 jTOporo соединен с входов устнновки и нодь ;Н подключен через соответствуюипш диоды к соответствующим выходам рсех нечетных ячеек, начиная с третьрЛ, л вто|рой вход триггера подключен к выходу 10 |схвмы совпадения, другой вход которой подключен к входу синхронкаация; кроме JTOro, входы источника тактовых импульсор подключены к базовым вь водам ключевых |транзисторсв, эмиттеры KOTOpi.ix модгоед 19 йены к обшей шине. «

Авторы

Даты

1976-02-25—Публикация

1973-06-08—Подача