1

Изобретение относится к области импульсной техники и может быть использовано в различных устройствах автоматики и вычислительной техники.

Известны реверсивные распределители импульсов, содержащие коммутатор питания и импульсные ячейки 1, однако эти устройства имеют сложную схему.

Известен реверсивный распределитель импульсов, содержаплий коммутатор питания и последовательно включенные импульсные ячейки памяти, входы считывания которых подключены к шинам тактовых сигналов, а выход каждой из ячейки подключен к входу предыдуп1ей и последуюн1ей ячеек 2.

Недостатками устройства являются сложность и невысокая стабильность выходных сигналов.

Цель изобретения - упрощение и повы1пение стабильности выходных сигналов.

Для этого в реверсивном распределителе импульсов, содержаи1ем коммутатор питания и последовательно включенные импульсные ячейки памяти, причем вход считывания всех нечетных импульсных ячеек памяти подключен к первой шине тактовых сигналов, а выход каждой ячейки соединен с входом

предыдущей и последующей ячеек, коммутатор питания выполнен четырехканальным, а импульсные ячейки памяти образуют четыре группы. Выходы каналов коммутатора питания соединены с соответствующими входами групп импульсных ячеек памяти, один из входов коммутатора подключен к щине реверса, а к входам считывания всех четных ячеек подключена пина второго тактового сигнала.

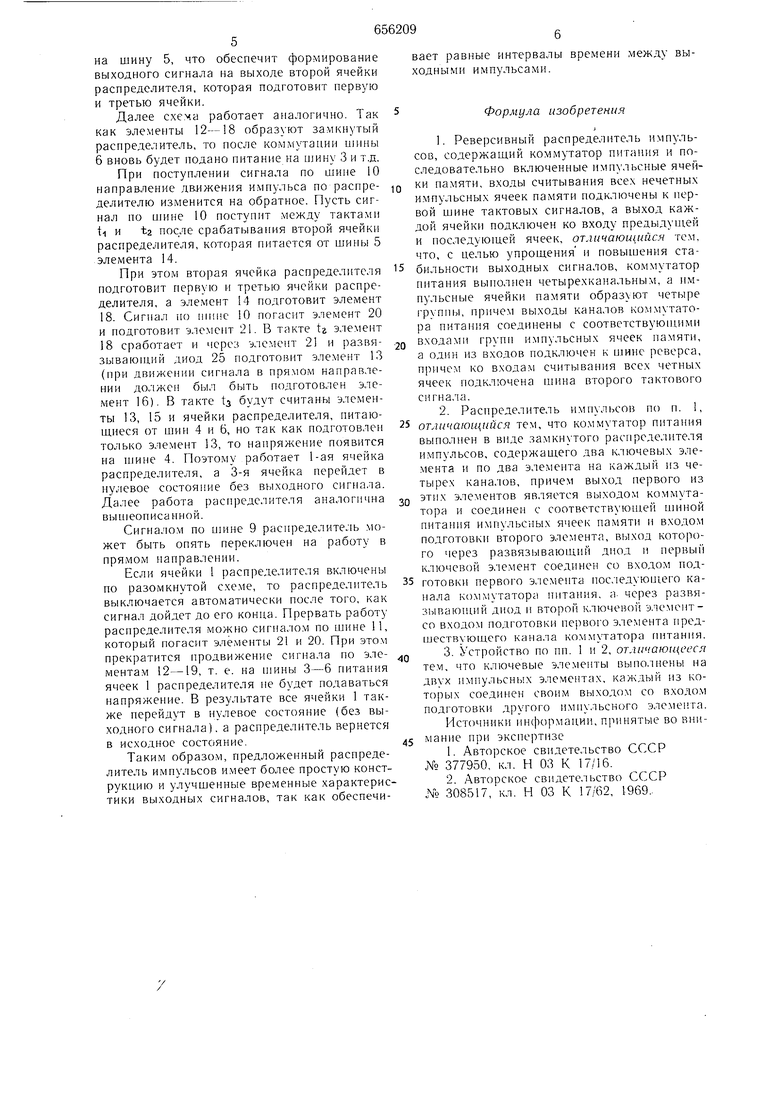

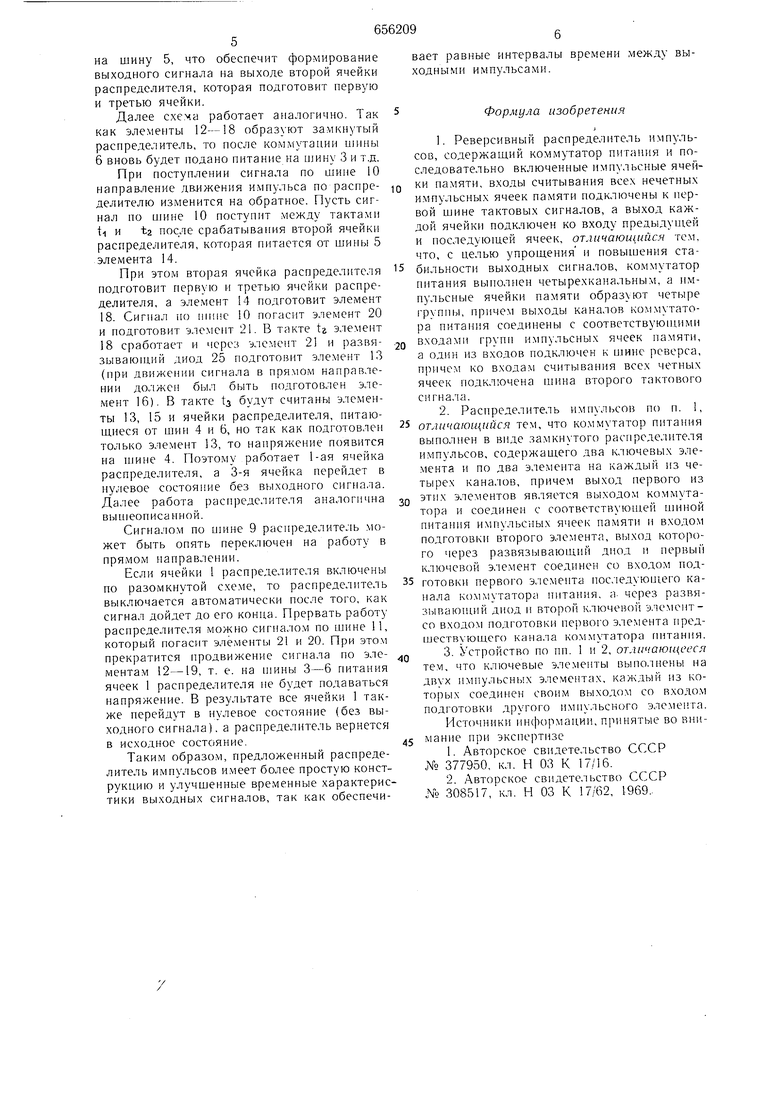

Коммутатор питания представляет собой замкнутый распределитель импульсов, содержапшй два ключевых э,1емента и по два элемента на каждый из четырех каналов. Выход первого из этих элементов является выходом коммутатора и соединен с соответствуюп1ей птпой питания импульсных ячеек памяти и входом подготовки второго элемента. Выход второго элемента через развязывающий диод и первый ключевой элемент соединен со входом подготовки первого элемента последуюп1,его канала коммутатора питания, а через развязывающий диод и второй ключевой элемент - со входом подготовки первого элемента предществующего канала коммутатора питания. Ключевые элементы выполнены на двух импульсных элементах, каждый из которых соединен своим выходом со входом подготовки другого импульсного элемента. На фиг. 1 представлена принципиальная электрическая схема предложенного распределителя импульсов; на фиг. 2 - принципиальная электрическая схема коммутатора питания. Распределитель импульсов содержит основные ячейки 1, к которым подключены шины 2 выходных сигналов. Кроме того, выход каждой ячейки 1 соединен с входом подготовки предшествующей и последующей основных ячеек распределителя. В случае разомкнутого распределителя исключение составляют начальная и конечная ячейки: вход начальной ячейки распределителя подключен только к входу подготовки последующей (второй)ячейки, а выход конечной ячейки - только к входу подготовки предпоследней. Входы питания эмиттеров транзисторов ячеек 1 собраны в четыре шины: к шине 3 подключены эмиттеры нулевой (начальной), четвертой, восьмой и т. п. ячеек распределителя; к шине 4 - эмиттеры первой, пятой, девятой и т. п. ячеек распределителя; к шине 5 - эмиттеры второй, шестой, десятой и т. п. ячеек распределителя; к шине 6 - эмиттеры третьей, седьмой, одиннадцатой и т. п. ячеек распределителя. Шины 3-6 соединены с соответствующими выходами коммутатора 7 питания. На вход подготовки начальной ячейки распределителя и на вход включения коммутатора 7 заведена щина 8. Кроме того, на входы коммутатора 7 заведены щины 9 и 10 переключения направления движения и шина 11 выключения распределителя. Четырехканальный коммутатор 7 питания построен на элементах 12-23. Выходы элементов 12-15 соединены соответственно с шинами 3-6 питания ячеек 1 распределителя импульсов. Кроме того, выход каждого из элементов 12-15 заведен на вход подготовки элементов 16-19 соответственно. Выход элемента 16 соединен со входом подготовки элемента 13 через развязывающий диод 24 и ключевой элемент 20 и со входом подготовки элемента 15 через развязывающий диод 25 и ключевой элемент 21. Аналогично выходы элементов 17-19 соединены со входами подготовки элементов 14, 15 и 12 соответственно через диоды 24 и ключевой элемент 20, а через диоды 25 и ключевой элемент 21 - со входами подготовки элементов 12-14. Выход элемента 20 соединен со входом подготовки элемента 22, выход которого заведен на вход подготовки элемента 20. Выход элемента 21 соединен со входом подготовки элемента 23,

В такте ti будут считаны элементы 12 и 14 и питающиеся от шин 3 и 5 ячейки распределителя, в том числе нулевая и вторая ячейки. Так как элемент 12 не подготовлен, то питание на шину 3 подано не будет и нулевой элемент распределителя перейдет в нулевое состояние .без сигнала на выходе. В то же время элемент 14 сработает, подготовит элемент 18 и подаст питание ВЫХОД которого заведен на вход подготовки элемента 21. Шина 8 включения распределителя заведенана входы подготовки элементов 12 и 22. Шина 11 вь ключения распределителя соединена со входами гап1ения элементов 21 и 20. Шины 9 и 10 переключения направления движения заведены соответственно на: вход гашения элемента 21 и вход подготовки элемента 20; вход гашения элемента 20 и вход подготовки элемента 21. На считывающие входы элементов 12 и 14 и всех ячеек 1 распределителя, запитанных от шин 3 и 5, заведена шина тактового сигнала ti. На считывающие входы элементов 13 и 15 и всех ячеек 1 распределителя, запитанных от шин 4 и 6, заведена шина тактового сигнала (3. На входы считывания элементов 16, 18, 21 и 20 заведена шина тактового сигнала ta, а на входы считывания элементов 17, 19, 21 и 20 - шина сигнала 14.. На входы считывания элементов 22 и 23 заведены шины тактовых сигналов 1з и ti. В выключенном состоянии все элементы распределителя не подготовлены, т. е. установлены на «О. Сигнал по шине 8, поступающий, например, в такте ti, подготавливает элементы 22, 12 и начальную ячейку 1 распределителя. В такте ti элемент 22 подготовит элемент 20. В то же время будут считаны элементы 12 и 14 и соответств Ю1пие ячейки 1 распределителя. Но так как подготовленным был только элемент 12, то он сработает - подготовит элемент 16 и подаст питание на щину 3. Одновременно сработает начальная (нулевая) ячейка 1 распределителя и сформирует выходной сигнал, подготовив также первую ячейку распределителя. В такте tj сработают элементы 16 и 20. Элемент 16 через развязывающий диод 24 и элемент 20 подготовит элемент 13. В то же время элемент 20 подготовит элемент 22, который в такте ts вновь подготовит элемент 20. В такте ta сработают элементы 13 и первая ячейка распределителя, которая, сформировав выходной сигнал, подготовит нулевую (начальную) и вторую ячейки. Элемент 13 подготовит элемент 17, который в такте t4 через диод 24 и элемент 20 подготовит элемент 14. В то же время элемент 20 подготовит элемент 22, а тот вновь подготовит элемент 20. на шину 5, что обеспечит формирование выходного сигнала на выходе второй ячейки раснределителя, которая подготовит первую и третью ячейки. Далее схема работает аналогично. Так как элементы 12-18 образуют за.мкнутый распределитель, то после коммута 1ии шины 6 вновь будет подано питание на 3 и т.д. При поступлении сигнала по шине 10 направление движения импульса по распределителю изменится на обратное. Пусть сигнал по шине 10 поступит .между тактами ti и ta после срабатывапия второй ячейки распределителя, которая питается от шины 5 элемента 14. При этом вторая ячейка распределителя подготовит первую и третью ячейки распределителя, а элемент 14 подготовит элемент 18. Сигнал но ппше 10 погасит элемент 20 и подготовит элемент 21. В такте 1г элемент 18 сработает и через элемент 21 и развязываюнхий диод 25 подготовит элемент 13 (при движении сигнала в прямом направлении должен был быть подготовлен элемент 16). В такте t будут считаны элементы 13, 15 и ячейки распределителя, питаюшиеся от шин 4 и 6, но так как подготовлеи только элемент 13, то напряжение появится на Н1ине 4. Поэтому работает 1-ая ячейка распределителя, а 3-я ячейка иерейдет в нулевое состояние без выходного сигнала. Далее работа распределителя аналогична вьцпеоиисаиной. Сигналом по Н1ине 9 распределитель может быть опять переключен на работу в прямом направлении. Если ячейки I распределителя включены по разомкнутой схе.ме, то распределитель выключается автоматически после того, как сигнал дойдет до его конца. Прервать работу раснределителя можно сигналом по шине 11, который погасит эле.менты 21 и 20. При этом прекратится продвижение сигиала по элементам 12-19, т. е. на ишны 3-6 питания ячеек 1 раснределителя не будет подаваться напряжение. В результате все ячейки 1 также перейдут в нулевое состояние (без выходного сигнала), а распределитель вернется в исходное состояние. Таким образом, предложенный раснределитель импульсов и.меет более простую конструкцию и улучшенные временные характеристики выходных сигналов, так как обеспечивает равные интервалы времени между выходными импульсами. Формула изобретения 1.Реверсивный распределитель и.мпульсов, содержащий коммутатор питания и последовательно включенные импульсные ячейки памяти, входы считывания всех нечетных и.мпульсных ячеек памяти подключены к первой шине тактовых сигналов, а выход каждой ячейки подключен ко входу предыдуи1ей и последующей ячеек, отличающийся те.м. что, с целью упрощения и повышения стабильности выходных сигналов, коммутатор питания выиолпен четырехканальным, а импульсиые ячейки памяти образуют четыре группы, причем выходы каналов коммутатора питания соедииены с соответствуюпгнми входами групп импульсных ячеек памяти, а один из входов подключен к шине реверса, причем ко входам считывания всех четных ячеек подключена шина второго тактового сигнала. 2.Раснределитель импульсов по п. 1, отличающийся тем, что коммутатор питания выполнен в виде замкнутого раснределителя импульсов, содержащего два ключевых элемента и по два элемеита на каждый из четырех каналов, причем выход первого из этих элементов является выходом коммутатора и соединен с соответствующей шиной питания импульсных ячеек памяти и входом подготовки второго элемента, выход которого через развязывающий диод и первый ключевой элемент соединен со входом подготовки первого элемента последующего канала коммутатора питания, а через развязывающий диод и второй ключевой элементсо входом подготовки первого элемента предилествуюшего канала коммутатора гп1тания. 3.Устройство по пи. 1 и 2, отличающееся тем, что ключевые элементы вьшолнены на двух импульсных элементах, каждый из которых соединен своим выходом со входо.м подготовки другого имиульсного элемента. Источники ин(|к)рмации., принятые во внимание при экспертизе 1.Авторское свидетельство СССР ,N0 377950, кл. Н 03 К 17/16. 2.Авторское свидетельство СССР № 308517, кл. Н 03 К 17/62, 1969..

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1971 |

|

SU308517A1 |

| Реверсивный счетчик | 1980 |

|

SU907813A1 |

| Устройство для адресования грузов установок непрерывного транспорта | 1978 |

|

SU716934A1 |

| УСТРОЙСТВО для АДРЕСОВАНИЯ ПОДВИЖНЫХ ОБЪЕКТОВ ПОДЪЕМНО-ТРАНСПОРТНЫХ И ШАХТНЫХ УСТАНОВОК | 1970 |

|

SU270348A1 |

| Устройство для адресования подвижных объектов | 1977 |

|

SU676987A2 |

| Устройство для контроля движения транспортного средства при переходе с одного пути на другой | 1972 |

|

SU500129A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ГИДРОФИЦИРОВАННОЙ ШАХТНОЙ КРЕПЬЮ | 1973 |

|

SU362143A1 |

| СЛЕДЯЩАЯ ЛИНИЯ ЗАДЕРЖКИ | 1993 |

|

RU2085026C1 |

| Реверсивный двухтактный распределитель | 1982 |

|

SU1056245A1 |

| Запоминающее устройство | 1979 |

|

SU830576A1 |

Авторы

Даты

1979-04-05—Публикация

1976-04-07—Подача