(54) УСТРОЙСТВО ДЛЯ ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации | 1982 |

|

SU1030829A2 |

| Устройство для приема многоканальных сообщений с кодоимпульсной модуляцией | 1982 |

|

SU1084855A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Устройство для приема телеметрической информации | 1978 |

|

SU734785A1 |

| Устройство для приема телеметрической информации | 1981 |

|

SU1008763A1 |

| Многоканальная телеизмерительная система | 1986 |

|

SU1310870A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Адаптивная телеизмерительная система | 1987 |

|

SU1494023A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Телеизмерительная система | 1978 |

|

SU734786A1 |

1

Устройство относится к области передачи информации и может быть использовано в многоканальных телеизмерительных системах.

Известны устройства для приема дискретной информации, содержащие детектор, соединенный с блокОМ выделения синхросигналов, подключенный к хронизатору, блок коррекции ошибок и последовательно соединенные преобразователь информационного кода и цифроаналоговый преобразователь, соединенный с коммутатором каналов.

Недостатком известных устройств является малая степень уплотнения информации при многоканальной передаче.

Целью изобретения является расширение функциональных возможностей устройства.

Это достигается тем, что в предлагаемое устройство введены блок памяти, первый и второй блоки запрета, блок выделения маркера кода, триггер, блок коррекции ошибок числа п.рОП1уш,ен1Ных ка:нало1В, преобразователь кода числа пропущенных каналов, дешифратор кода числа пропущеннььх каналов, блока стробпрования н элемент «И, причем к первому входу блока памяти подключен выход детектора, а ко второму - выход первого блока запрета, первый вход которого через хронизатор и блок выделения синхросигналов подключен к входу устройства, а второй вход первого блока запрета соединен с выходом

блока стробирования, вход которого подключен к выходу дешифратора кода числа пропущенных каналов, первый вход которого через преобразователь кода числа пропущенных каналов и блок коррекции ошибок числа пропущенных капалов подключен к выходу элемента «И, первый вход которого соединен с выходом триггера и первым в.чодом второго блока запрета, а второй вход элемента «И подключей к выходу блока памяти, второму входу второго блока запрета и к входу блока выделения маркера кода, выход которого соединен с первым входом триггера, второй вход которого подключен к вторым входам дешпфратора кода числа пропущенных каналов, преобразователя кода числа пропущенных каналов, к входам детектора, преобразователя информационного кода, цифроаналогового преобразователя и коммутатора капалов.

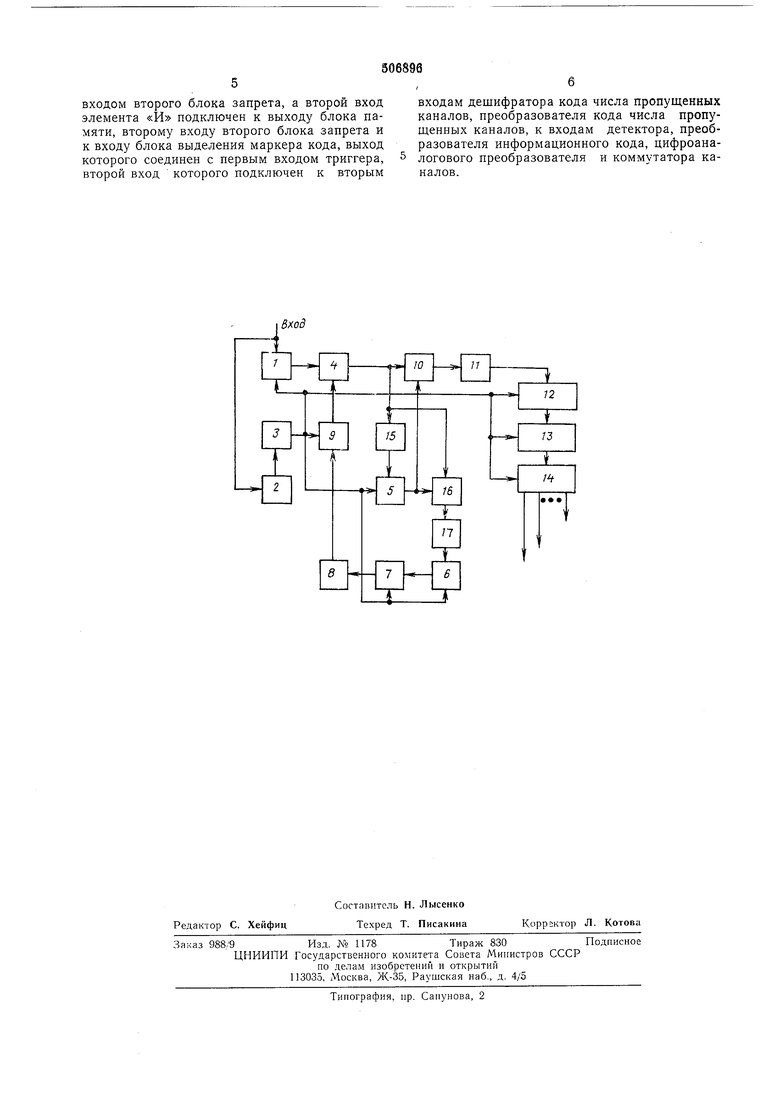

Схема описываемого устройства показана на чертеже.

Устройство содерл1ит детектор 1, блок 2 выделения синхросигнала, хронизатор 3, блок памяти 4, триггер 5, преобразователь 6 кода

числа пропущенных каналов, дешифратор 7 кода чпсла пропущенных каналов, блок 8 стробирования, блоки запрета 9, 10, блок 11 коррекции ошибок, преобразователь 12 информационного кода, цифроаналоговый преобразователь (ЦАП) 13, коммутатор 14 каналов, блок 15 выделения маркера кода, элемент «И 16, блок 17 коррекции ошибок числа пропущенных каналов.

Устройство работает следующим образом.

Полный телеметрический сигнал подается в детектор 1 и блок 2. Первый по искаженному сигналу, действующему на его входе, определяет, какие символы передавались (папример, символ «О или «1). Во втором из полного телеметрического сигнала производится выделепие сигпалов синхронизации (кадра), которые синхронизируют местный хронизатор 3 по фазе. С выхода опознавателя (детектора) 1 полный телеметрический сигнал поступает в блок памяти 4.

Хронизатор 3 вырабатывает стабильные импульсы с периодом, равным длительности информационного кода (или временному канальному интервалу). При появлении па его входе первого каиального имлульса производится сброс в пулевое состояние триггера 5, преобразователя 6 и дешифратора 7. При этом стробсигнал на выходе блока 8 отсутствует и блок запрета 9 оказывается открытым по сигнальному входу для первого канального импульса, который, проходя через эту схему, поступает па считывающий вход блока памяти 4, вследствие чего с выхода последнего на сигнальный вход блока запрета 10 выдается ипформациовный код первого канала. Поскольку на запрещающем входе блока запрета 10 сигнал с выхода триггера 5 отсутствует, то информационный код первого капала, проходя через эту схему, поступает на вход блока 11. Здесь возмржные ошибки изза действия помех обнаруживаются и исправляются. В преобразователе 12 помехоустойчивый код преобразуется в простой код, а при помощи ЦАП 12 превращается в аналоговую величину. Коммутатор 14, синхронизируемый теми же канальными импульсами от хронизатора 3, выдает значение аналоговой величины в первый капал. Пусть теперь в телеметрическом сигнале за информационным кодом первого каиала передавались маркер и код одного пропущенного канала (па передающей стороне выборка по второму каналу избыточной). Второй канальный импульсе выхода хронизатора 3 выдает на выход блока паадяти 4 ма-ркер и код числа пропущенных каналов (один канал). Первый, попадая в блок выделения маркера 15, вырабатывает сигнал, переводя триггер 4 в «единичное состояние. Сигнал, снимаемый с выхода триггера 5, запрещает прохождение маркера и кода числа пропущеиных каналов через блок запрета 10 и последовательно соединенные с ним блоки на вход коммутатора 14 каналов. Последний ,работая как бы вхолостую, не изменяет предыдущее значение аналоговой информации у получателя второго канала. Одновременно с этим сигнал триггера 5 открывает элемент «И 16, через который код числа пропущенных каналов поступает на блок 17, а атем - на преобразователь 6. При этом

«а оДИНОчиоМ выходе дешифратора 7, подключенного входами к выходам преобразователя 6, возникает управляющий сигнал, который должен бы был запустить блок 8 отроба переменной длительности на время канального интервала, чтобы закрыть схему запрета 9. Но необходимость в этом отсутствует, так как код числа пропущенных каналов в кадре располагался во втором канальном интервале и был

«вырезан оттуда с помощью блока запрета 10. Поэтому первый выход дешифратора (сигнал одного пропущенного канала) к входу блока строба 8 вообще не подключается. Если бы число пропущенных каналов в кадре было

два, в этом случае управляющий сигнал возник бы на втором выходе дешифратора 7 и блок 8 выдал бы импульс длительностью в один канальный интервал, закрывая блок запрета 9 для прохождения третьего канального

импульса от хропизатора 3 к считывающему входу блока памяти 4 и заставляя отработать вхолостую коммутатор 14 и по третьему каналу. Таким образом, информационный код будет храниться в блоке памяти 4 до тех пор,

пока не будут отработаны коммутатором 14

вхолостую все пропущенные каналы. В этом и

заключается как бы «растягивание сжатого

телеметрического сигнала.

Установка триггера 5, преобразователей 6 и

12, дешифратора 7 и ПАП 13 в исходное состояние производится канальными импульсами от хронизатора 3.

Формула изобретения

Устройство для приема дискретной информации, содержащее детектор, соединенный с блоком выделения синхросигналов, подключенный к хронизатору, блок коррекции ошибок, через последовательно соединенные преобразователь информационного кода и цифроаналоговый преобразователь, соедипенный с коммутатором каналов, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него введены блок памяти, первый и второй блоки запрета, блок выделения маркера кода, триггер, блок коррекции ошибок числа пропущенных каналов, преобразователь кода числа пропущенных

каналов, дешифратор кода числа пропушеппых каналов, блок стробирования и элемент «И, причем к первому входу блока памяти подключен выход детектора, а -ко второму - выход первого блока запрета, первый вход

которого через хронизатор и блок выделепия синхросигналов подключен к входу устройства, а второй вход первого блока запрета соединен с выходом блока стробирования, вход которого подключен к выходу дешифратора

кода числа пропущенных каналов, первый вход которого через преобразователь кода числа пропущенных каналов и блок коррекции ошибок числа пропущенных каналов подключен к выходу элемента «И, первый вход которого соединен с выходом триггера и первым

входом второго блока запрета, а второй вход элемента «И подключен к выходу блока памяти, второму входу второго блока запрета и к входу блока выделения маркера кода, выход которого соединен с первым входом триггера, второй вход которого подключен к вторым

входам дешифратора кода числа пропущенных каналов, преобразователя кода числа пропущенных каналов, к входам детектора, преобразователя информационного кода, цифроаналогового преобразователя и коммутатора каналов.

Авторы

Даты

1976-03-15—Публикация

1974-12-02—Подача