РЬобретение относится к интегральным иолупроводниковым схемам, в частности к интегральным транзисторам.

Известны интегральные транзисторы с изолирующей диффузионной коллекторной областью на подложке 1.

Известна конструкция транзистора, выполненная на подложке первого типа ирозодимости с коллекторной областью второго типа проводимости, базовой областью того же типа проводпмости, что и подложка, и эмиттером второго типа проводимоети,2. .

Известные интегральные транзисторы ири работе в ключевом режиме, наприме) в качестве инвертора, входят в насыщение, что существенно снижает их быстродействие.

Цель изобретения - органические насыщения интегрального транзистора.

Это достигается соединением базовой области с подложкой соединительным участком, ширина которого не превышает удвоенной ширины слоя объемного заряда в полупроводнике подложки.

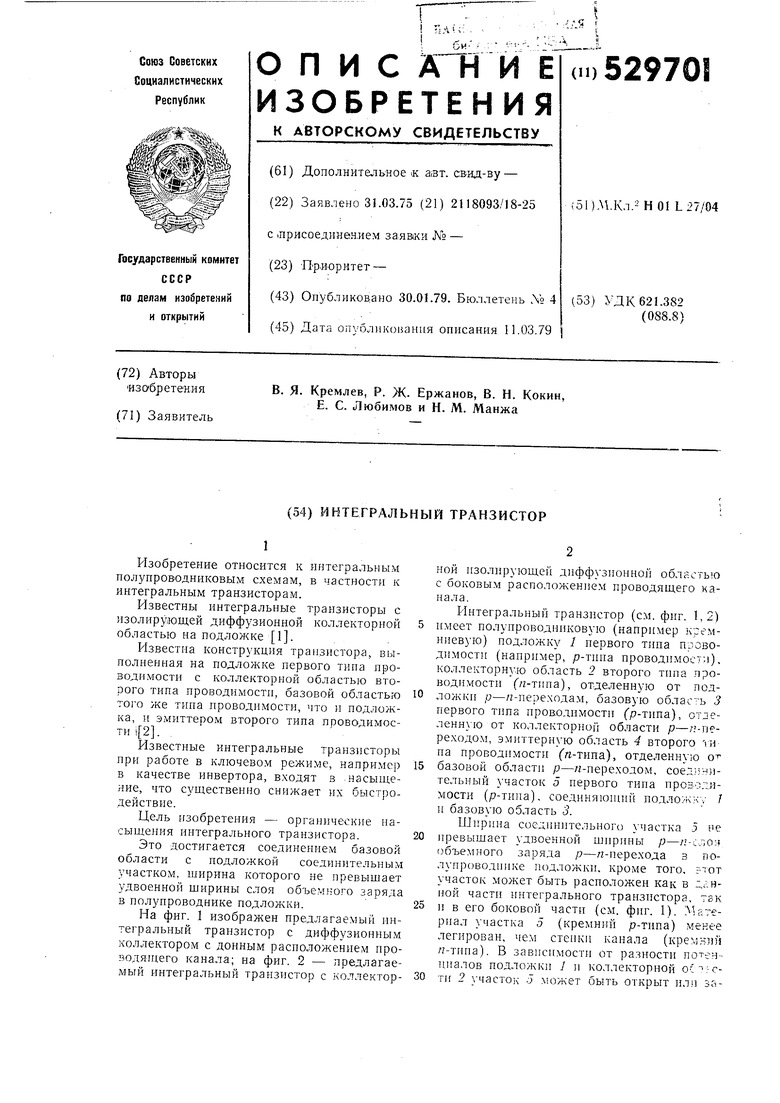

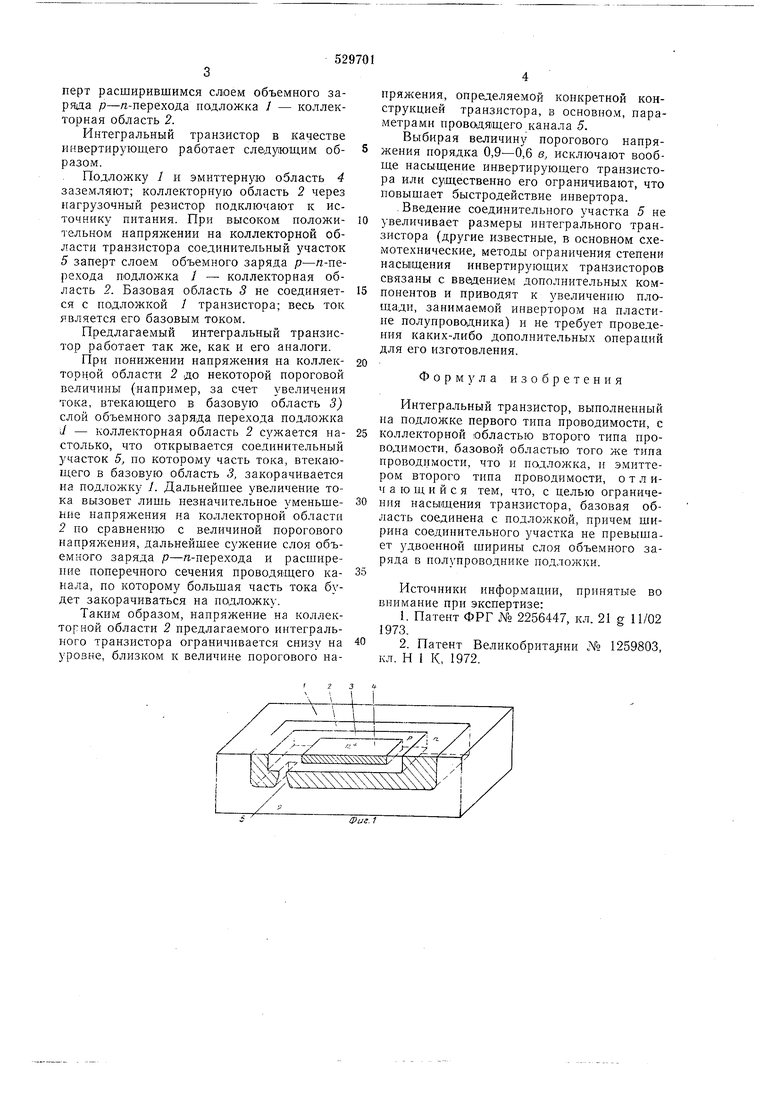

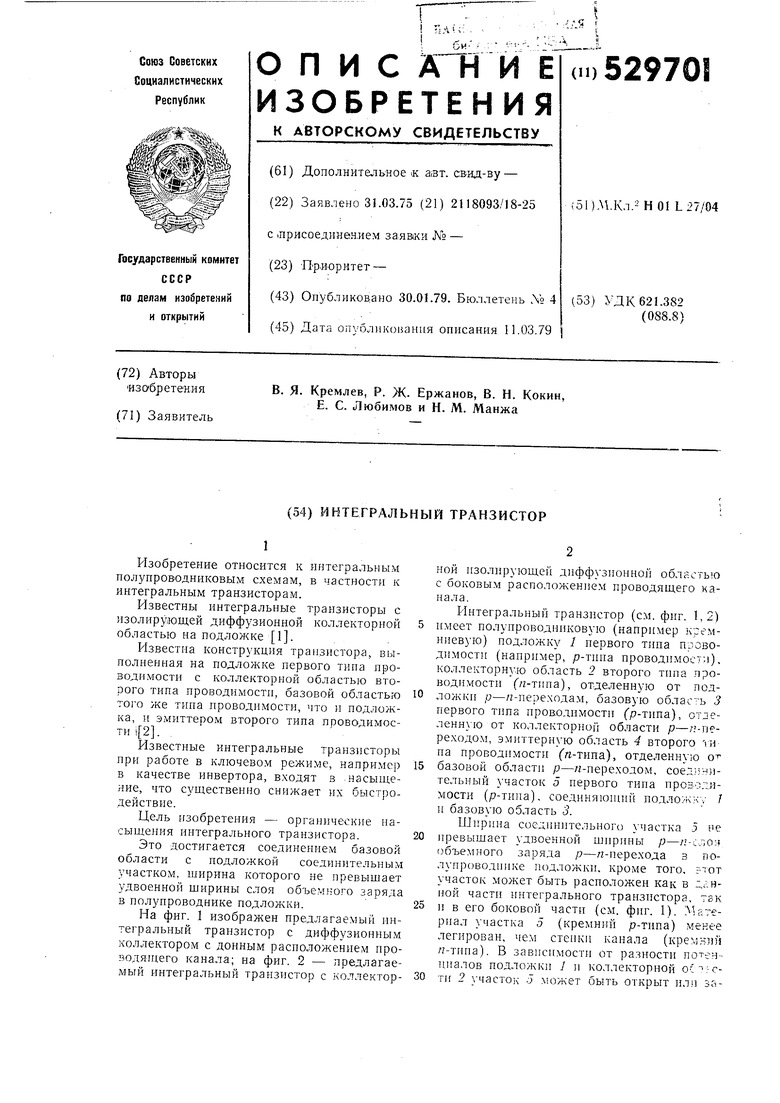

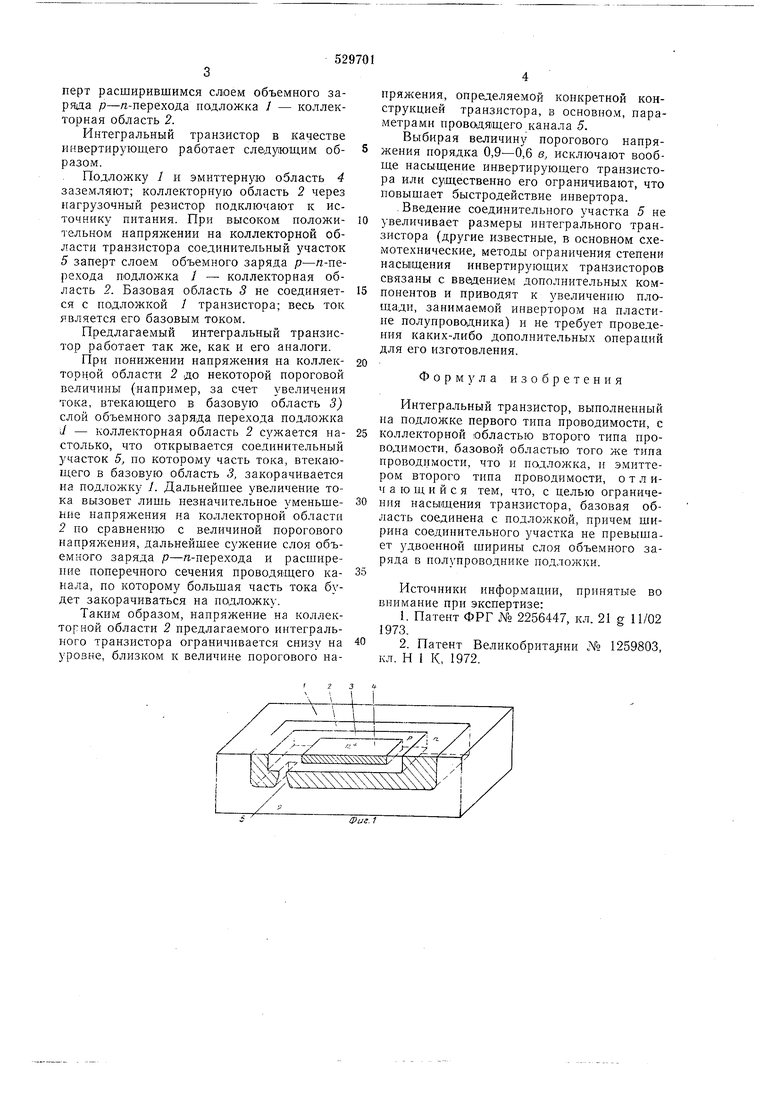

На фиг. I изображен предлагаемый интегральный транзистор с диффузионным коллектором с донным расположением проводящего канала; на фиг. 2 - предлагаемый интегральный транзистор с коллекторной изолирующей диффузионной областью с боковым расположением проводящего канала.

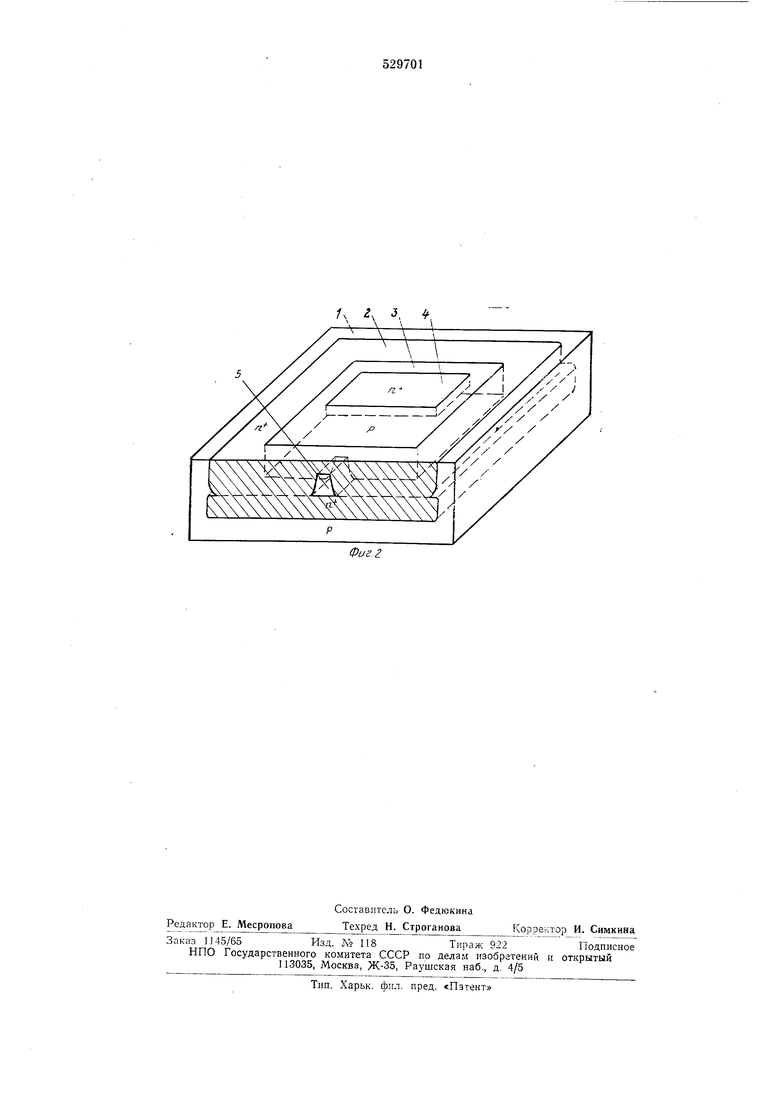

Р1нтегральный транзистор (см. фиг. 1,2) имеет полупроводниковую (например кремн 1евую) подложку / первого типа пооводимостп (наирпмер, р-типа проводпмост;)), коллекторную область 2 второго тина проводпмости (/2-тппа), отделенную от подложки р-я-переходам, базовую область 3 первого тппа проводпмости (р-тппа), отлеленн ю от коллекторной области р-/.-переходом, эмиттерную область 4 второго па проводимости (га-типа), отделенную о базовой области р-л-переходом, соединительный участок 5 первого тииа проволимости (/ -типа), соединяющий подложху / и базовую область 3.

Ширина соедппптельного участка 5 се превышает удвоенной шприны р-л-сло; (объемного заряда р-л-перехода в полупроводнике подложки, кроме того, тот участок может быть расио.тожен как в д -:нпой части интегрального транзпстора, так п в его боковой части (см. фиг. 1). Материал участка 5 (кремний р-типа) менее легирован, чем стенкп канала ( л-тпиа). В зависимости от разности потенпиалов подложки 7 и коллекторной оС ;стп 2 участок J иэжет быть открыт ил)) заперт расширившимся слоем объемного заряда р-л-перехода подложка / - коллекторная область 2. Интегральный транзистор в качестве инвертируюш,его работает следующим образом. . Подложку 1 и эмиттерную область 4 заземляют; коллекторную область 2 через нагрузочный резистор подключают к источнику питания. При высоком положительном напряжении на коллекторной области транзистора соединительный участок 5 заперт слоем объемного заряда р-«-перехода подложка / - коллекторная область 2. Базовая область 3 не соединяется с подложкой 1 транзистора; весь ток является его базовым током. Предлагаемый интегральный транзистор работает так же, как и его аналоги. При понижении напряжения на коллекторной области 2 до некоторой пороговой величины (например, за счет увеличения тока, втекающего в базовую область 3) слой объемного заряда перехода подложка 1 - коллекторная область 2 сужается настолько, что открывается соединительный участок 5, по которому часть тока, втекающего в базовую область 3, закорачивается на подложку /. Дальнейшее увеличение тока вызовет лишь незначительное уменьшение напряжения на коллекторной области 2 по сравнению с величиной порогового напряжения, дальнейшее сужение слоя объемного заряда р-п-перехода и расширение поперечного сечения проводящего канала, по которому большая часть тока будет закорачиваться на подложку. Таким образом, напряжение на коллекторной области 2 предлагаемого интегрального транзистора ограничивается снизу на уровне, близком к величине порогового на(Риг.1 пряжения, определяемой конкретной конструкцией транзистора, в основном, параметрамн ирово1дящего канала 5. Выбирая величину порогового напряжения порядка 0,9-0,6 в, исключают вообще насыщение инвертирующего транзистора или существенно его ограничивают, что повышает быстродействие инвертора. . Введение соединительного участка 5 не увеличивает размеры интегрального транзистора (другие известные, в основном схемотехнические, методы ограничения степени насьщения инвертирующих транзисторов связаны с введением дополнительных компонентов и приводят к увеличению площади, занимаемой инвертором на пластине полупроводника) и не требует проведения каких-либо дополнительных операпий для его изготовления. Формула изобретения Интегральный транзистор, выполненный на подложке первого типа проводимости, с коллекторной областью второго типа проводимости, базовой областью того же типа проводимости, что и подложка, и эмиттером второго типа проводимости, отличающийся тем, что, с целью ограничения насыщения транзистора, базовая область соединена с подложкой, причем ширина соединительного участка не превыщает удвоенной ширины слоя объемного заряда в полупроводнике подложки. Источники информации, принятые во внимание при экспертизе: 1.Патент ФРГ № 2256447, кл. 21 g 11/02 1973. 2.Патент Великобритании JNfg 1259803, кл. Н I К, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральный логический элемент | 1977 |

|

SU602055A1 |

| Интегральный инвертор | 1975 |

|

SU519102A1 |

| ИСТОЧНИК ТОКА | 2016 |

|

RU2620592C1 |

| ПОЛЕВОЙ ТРАНЗИСТОР | 1993 |

|

RU2120155C1 |

| ИНТЕГРАЛЬНЫЙ ТОКОМАГНИТНЫЙ ДАТЧИК СО СВЕТОДИОДНЫМ ИНДИКАТОРОМ | 2005 |

|

RU2300824C1 |

| БИПОЛЯРНЫЙ ТРАНЗИСТОР | 1982 |

|

SU1091783A1 |

| ПОЛУПРОВОДНИКОВЫЙ МАГНИТНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2284612C2 |

| ПЛАНАРНЫЙ МАГНИТОТРАНЗИСТОРНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2010 |

|

RU2422943C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ВЫСОКОВОЛЬТНОГО ИНТЕГРАЛЬНОГО ТРАНЗИСТОРА | 2012 |

|

RU2492546C1 |

| ПОЛУПРОВОДНИКОВАЯ СТРУКТУРА | 1990 |

|

RU1699313C |

Авторы

Даты

1979-01-30—Публикация

1975-03-31—Подача