(54) БИИМПУЛЬСНЫЙ ПРИЕМНИК

| название | год | авторы | номер документа |

|---|---|---|---|

| Биимпульсный приемник | 1982 |

|

SU1078634A1 |

| ФОРМИРОВАТЕЛЬ ОПОРНОЙ СИНХРОЧАСТОТЫ | 1969 |

|

SU244378A1 |

| Формирователь опорной частоты | 1972 |

|

SU457183A1 |

| Устройство для передаси и приема биимпульсного сигнала | 1974 |

|

SU608408A1 |

| Устройство синхронизации | 1983 |

|

SU1107314A1 |

| Биимпульсный регенератор | 1980 |

|

SU892742A1 |

| УСТРОЙСТВО ПРИЕМА БИИМПУЛЬСНЫХ СИГНАЛОВ | 1969 |

|

SU253115A1 |

| Биимпульсный регенератор | 1982 |

|

SU1104670A2 |

| Устройство для выделения опорного сигнала | 1982 |

|

SU1030985A1 |

| Система передачи цифровой информациибииМпульСНыМ СигНАлОМ | 1976 |

|

SU815953A1 |

1

Изобретение относится к технике передачи информации по кабельным, волноводным и оптическим линиям связи.

Известен биимпульсный приемник, содержащий интегратор, двухполупериодный выпрямитель и резонансный контур 1.

Известен также бнимпульсный приемник, содержащий накопитель, состоящий из двух последовательно соединенных вычитающих блоков с включенными параллельно каждому из; них линиями задержки и интегратора без сброса, соединенный со стробирующим блоком, управляющий вход которого соединен с формирова елем стробирующих импульсов 2.

Однако эти биимпульсные приемни.ки имеют низкую помехоустойчивость.

С целью повышения помехоустойчивости в предлагаемом биимпульсном приемникеJ. содержащем накопител состояшлй из двух последовательно соединенных вычитающих блоков с включенными параллельно каждому из них ЛИНИЯМИ задержки и интегратора без сброса и-- соединенный со стробирующим блоком, управляющий вход которого соединен с формирователем стробирующих импульсов, выход накопителя соединен с формирователем стробирующих импульсов через последовательно соединенные двухполупериодный выпрямитель и резонансный контур

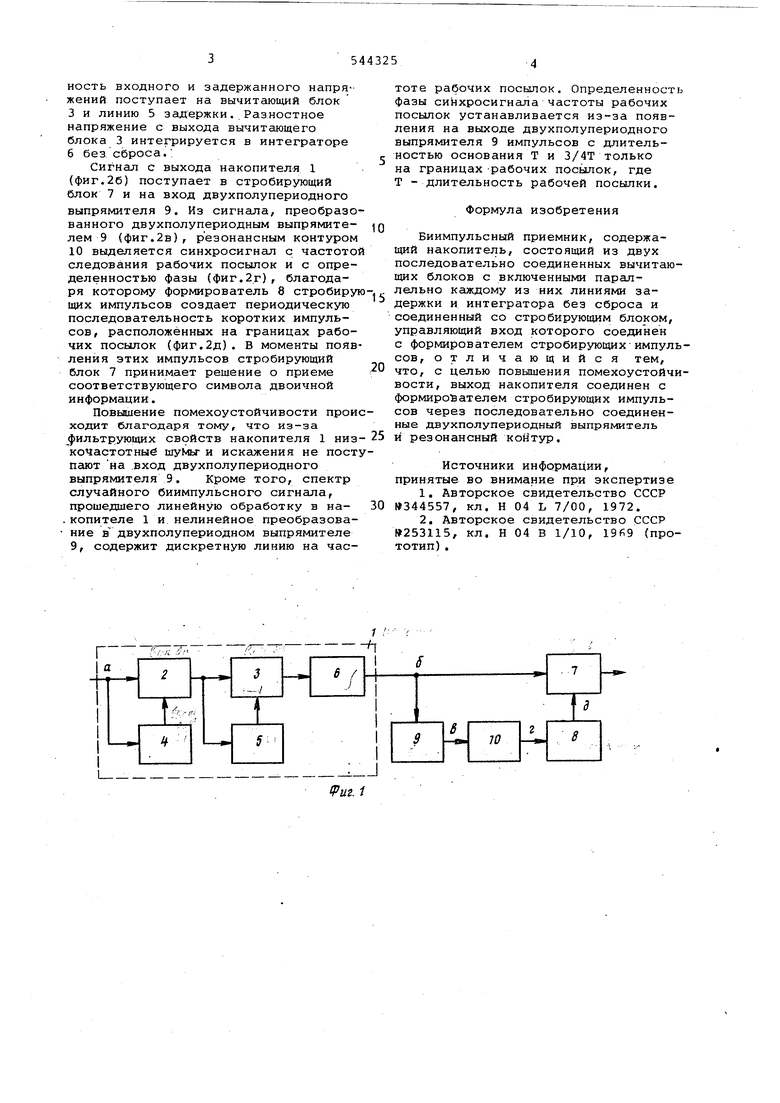

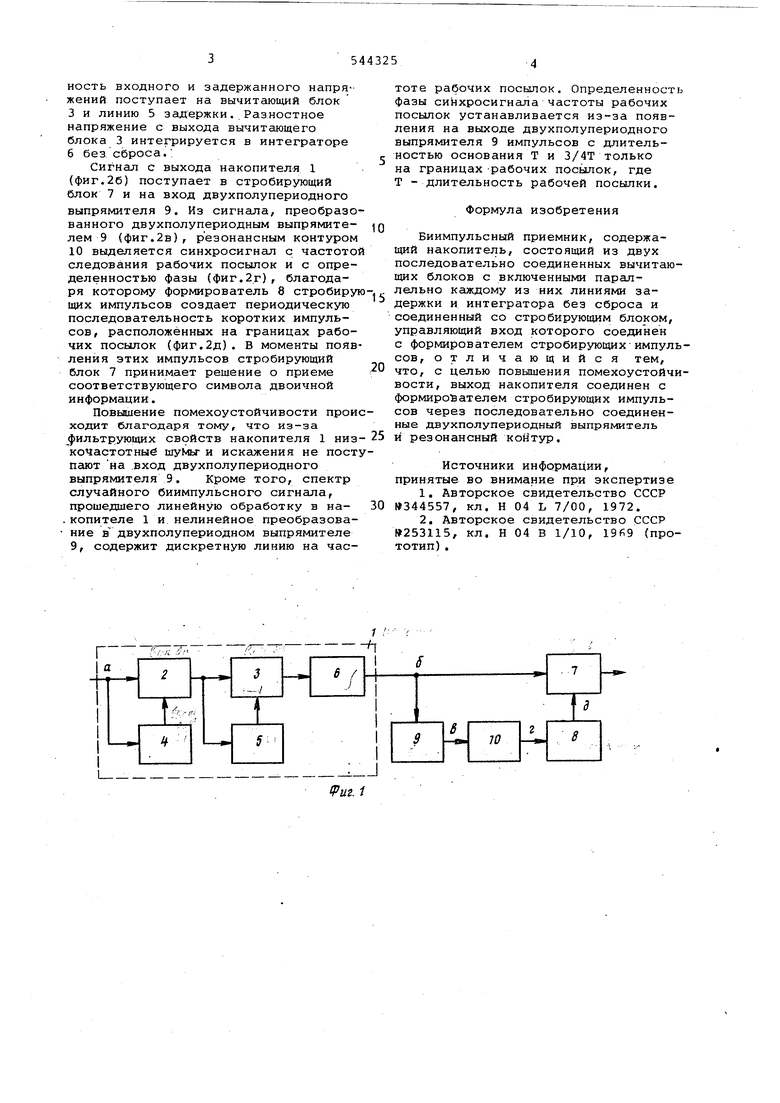

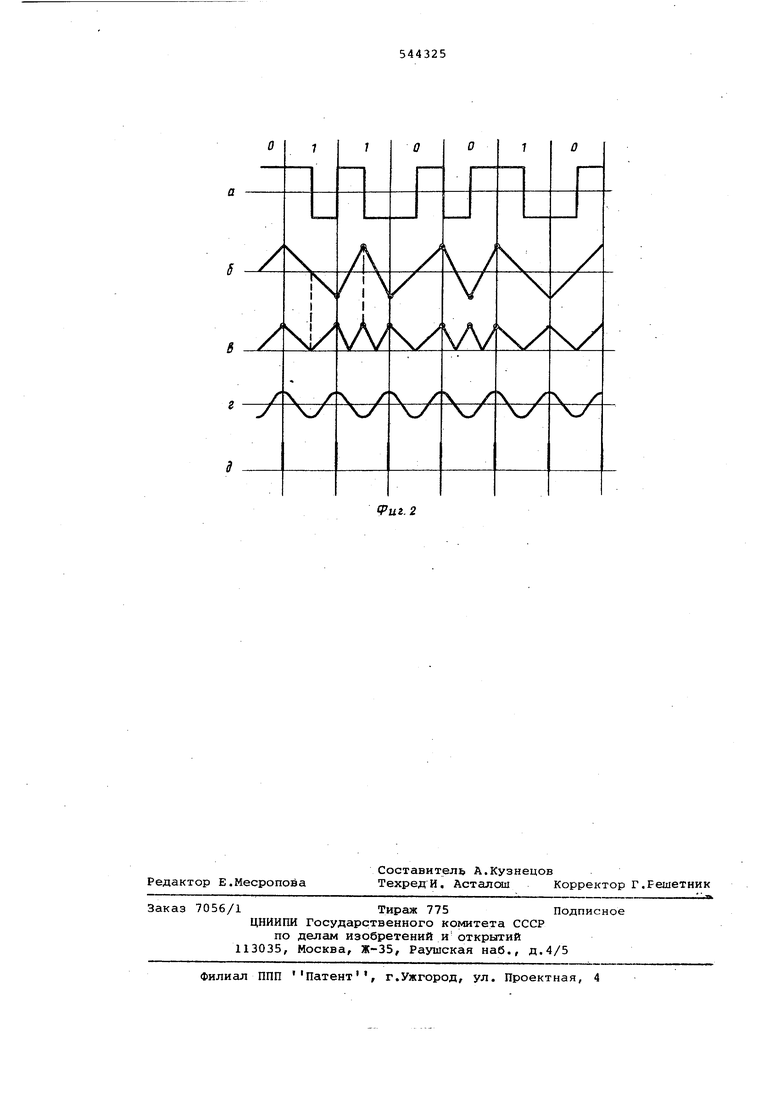

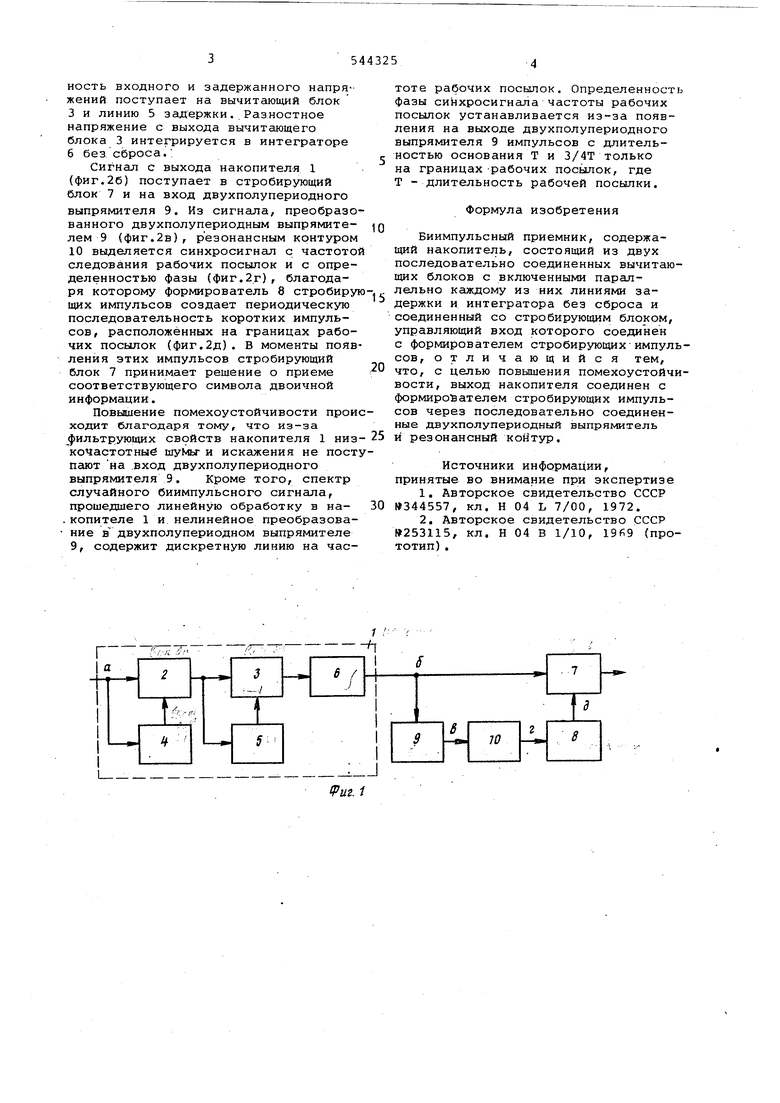

На фиг.1 изображена функциональная схема предлагаемого биимпульсного приемника; на фиг.2 - временные диаграммы, поясняющие его работу.

0

Биимпульсный приемник содержит накопитель 1, состоящий из двух последовательно -соединенных вычитающих блоков 2 и 3 с включенными параллельно каждому из линиями 4

5 и 5 задержки и интегратора 6 без сброса, соединенный со стробирующим блоком 7, управляющий вход которого соединен с формирователем 8 стробирующих импульсов, причем

0 выход накопителя 1 соединен с форьшрователем стробирующих импульсов через последовательно соединенные двухполупериодный выпрямитель 9 и резонансный контур 10.

5

Биимпульсный приемник работает следующим образом.

Сигнал, прошедший по линии связи (фиг,2а), подается на вычитающий

0 блок 2 и на линию 4 задержки. Разность входного и задержанного напряений поступает на вычитающий блок 3 и линию 5 задержки..Разностное напряжение с выхода вычитающего блока 3 интегрируется в интеграторе без сброса.

Сигнал с выхода накопителя 1 (фиг.26) поступает в стробирующий блок 7 и на вход двухполупериодного выпрямителя 9. Из сигнала, преобразованного двухполупериодным выпрямителем 9 (фиг.2в), резонансным контуром 10 выделяется синхросигнал с частотой следования рабочих посылок и с определенностью фазы (фиг,2г), благодаря которому формирователь 8 стробирующих импульсов создает периодическую последовательность коротких импульсов, расположённых на границах рабочих посылок (фиг.2д). В моменты появления этих импульсов стробирующий блок 7 принимает решение о приеме соответствующего символа двоичной информации.

Повышение помехоустойчивости происходит благодаря тому, что из-за фильтрующих свойств накопителя 1 низкочастотные шуМы- и искажения не посту пеиот на .вход двухполупериодного выпрямителя 9, Кроме того, спектр случайного биимпульсного сигнгила, прошедшего линейную обработку в накопителе 1 и нелинейное преобразование в двухполупериодном выпрямителе 9, содержит дискретную линию на частоте рабочих посылок. Определенност фазы синхросигнала частоты рабочих посылок устанавливается из-за появления на выходе двухполупериодного выпрямителя 9 импульсов с длительностью основания Т и 3/4Т только на границах -рабочих посылок, где Т - длительность рабочей посылки.

Формула изобретения

Биимпульсный приемник, содержащий накопитель, состоящий из двух последовательно соединенных вычитающих блоков с включенными параллельно каждому из них линиями задержки и интегратора без сброса и соединенный со стробирующим блоком, управляющий вход которого соединен с формирователем стробирующих-импулсов, отличающийся тем, что, с целью повышения помехоустойчвости, выход накопителя соединен с формирователем стробирующих импульсов через последовательно соединенные двухполупериодный выпрямитель и резонансный контур.

Источники информации, принятые во внимание при экспертизе

II

if

/

Риг.2

Авторы

Даты

1979-11-25—Публикация

1973-06-14—Подача