со

Изобретение предназначено для использования в технике связи, а так же в системах цифровой магнитной записи.

Известен формирователь опорной части из случайной последовательности биимпульсных посылок, содержащий двухполупериодный выпрямитель и резонансный контур, причем к входу двухполупериодного выпрямителя подключен блок вычитания, на первый вход которого подана последовательность биимпульсных посылок непосредственно, а на второй через линию задержки, при этом между двухполупериодным выпрямителем и резонансным контуром включен блок временной селекции 1Д .

Однако устройство обладает низкой помехоустойчивостью.

Наиболее близким к предлагаемому является устройство синхронизации, содержащее формирователь нулевых пересечений, выход которого подключе к установочному входу первого делителя частоты на два, к счетному входу которого подключен выход формирователя сигнала коррекции, а выход первого делителя частоты на два через блок ФАПЧ подключен к входу формирователя синхросигнала, а также последовательно соединенные ключ, генератор пилообразного напряжения и пороговый блок, выход которого подключен к входу формирователя сигнала коррекции, а к входу ключа подсоединен выход формирователя нулевых пересечений С 21,

Однако известное устройство синхронизации обладает низкой точностью синхронизации при дрейфе частоты следования синхросигнала.

Цель изобретения - повышение точности синхронизации при дрейфе частоты следования сигнала.

Для достижения поставленной цели в устройство синхронизации, содержащее формирователь нулевых пересечений , выход которого подключен к установочному входу первого делителя частоты на два, к счетному входу которого подключен выход формирователя сигнала коррекции, а выход первого делителя частоты на два через блок tФАПЧ)подключен к входу формирователя синхросигнала, введены последовательно соединенные делитель частоты на U/2 (где п/2 1, 2,3,...,

h/2), второй делитель частоты на два и элемент И, выход которого подключен к входу формирователя сигнала коррекции, а к второму входу элемента И подключен выход делителя частоты п/2, к установочному входу второго делителя частоты на два подключен выход формирователя нулевых пересечений, а к счетному входу делителя частоты на п/2-подключен дополнительный выход блока ФАПЧ.

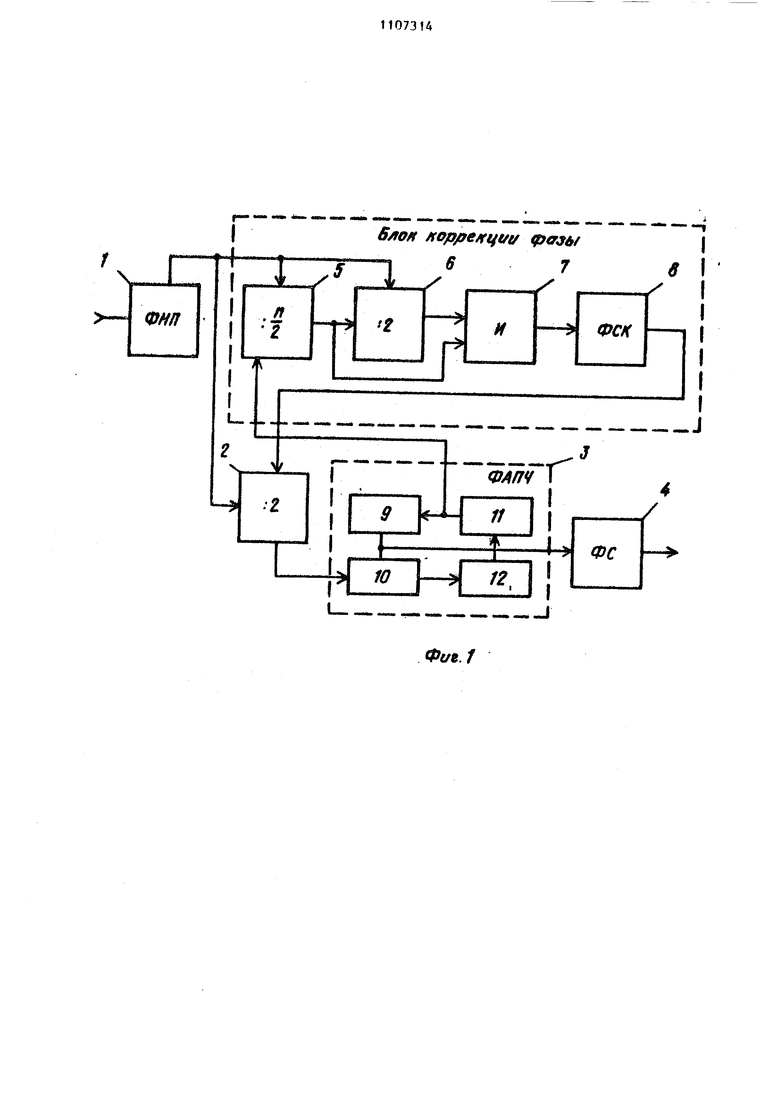

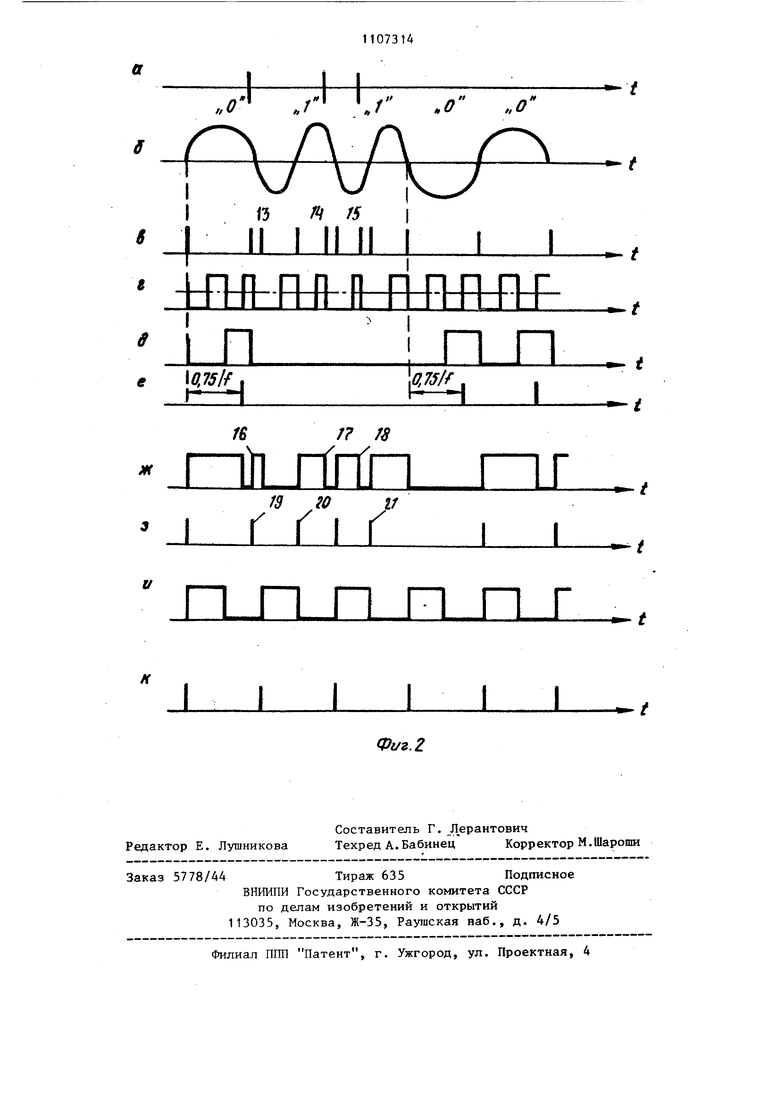

На фиг. 1 представлена структурная электрическая схема устройства синхронизации, на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство синхронизации содержит формирователь 1 нулевых пересечений, делитель 2 частоты на два, блок 3 ФАПЧ, формирователь 4 синхросигнала, делитель 5 частоты на ц/2, второй делитель 6 частоты на два, элемент И 7, формирователь 8 сигнала коррекции, блок 3 ФАПЧ содержит делитель 9 частоты на два фазовый детектор 10 генератор 11, управляемый напряжением, фильтр 12.

Устройство синхронизации работает

следующим образом.

Фазоманипулированный сигнал (фиг. 2J) поступает на вход формирователя

1нулевых пересечений, выходные импульсы которого (фиг. 2Ь) воздействуют на счетный вход первого делителя

2частоты на два и установочные входы делителя 5 частоты на П/2, и второго делителя 6 частоты на два. На счетный вход делителя 5 частоты на два поступает с дополнительного выхода блока 3 ФАПЧ сигнал частотной

в г раз превышающий частоту импульсов, синхронизации. Сигналы делителя 5 частоты на п/2 (фиг. 2г) и второго делителя 6 частоты на два (фиг. 2д) объединяются элементом И 7. ПолЬжительный период на выходе элемента И 7, вызывающий появление в формирователе 8 сигнала коррекции (фиг. 3 возникает при величине паузы между смежными импульсами формирователя 1 нулевых пересечений не менее 0,75/ (где 5 - среднее значение частоты следования информационных посылок). Поскольку это условие выполняется для сигналов, соответствующих двоичному нулю, и не выполняется для двоичных единиц, импульсы коррекции появляются лить при поступлеНИИ на вход устройства jiyneBUx сиг налов . При принятом в блоке коррекции фа способе детектирования сигнала (логическое детектирование) двоичным нулем считается сигнал, интервал меж ду смежными точками пересечения которого с нулевой линией при отсутствии искажений равен точно 1/- . За двоичную единицу принимаются два примыкающих друг к другу интервала, каждый из.которых равен при отсутствии искажений 0,5/f . При наличии временных искажений за порог различия нуля от единицы принимается уровень 0,75/f , как одинаково удаленный от средних длительносте нулей и единиц. В результате воздействия импульсов коррекции на установочный вход первого делителя 2 частоты на два, каждый неискаженный нуль устанавливает фиксированную фазу делителя, устраняя таким обарзом скачки фазы возникающие в результате воздействия помех на делитель. Каждая информационная единица в зывает появление двух сигналов нулевых пересечений на выходе формирователя 1 нулевых пересечений, разделенных интервалами 0,5/f так, что цель коррекции в этом случае не срабатывает, и на .выходе первого делителя 2 частоты на два образуется один Пс-риод частоты F . При информаци онном нуле сброс в исходное состояние названного делителя происходит по сигналу коррекции. Таким образом, на вход блока ФАПЧ поступают сигналы с частотой f и фиксированной фазой положительных перепадов вне зависимости от вида входной информации. При воздействии помех (фиг. 2А) формирователь 1 нулевых пересечений выдает импульсы, как при пересечении информационным сигналом нулевой лини так и в момент появления импульсной помехи (фиг. 2fc). Импульсы, порожденные помехами (импульсы 13-15, фиг. 2&), осуществляют дополнительные сбросы делителя 5 частоты на П/2 и второго делителя 6 частоты на два в нуль (фиг. 2 г , А. ) н вызывают появление лишних перепадов в выходном напряжении первого делителя 2 частоты на два (импульсы 16-18 фиг. 2) . Сигналы, сформированные из положительных перепадов (импульсы 1921 фиг. 2з), диаграмма не формируется в устройстве и приведена с целью пояснить по какому из фронтов первого делителя 2 частоты на два производится подстройка по фазе), воздействуют на блок ФАПЧ как помехи, которые приведут только к отклонению фазы выходного сигнала блока ФАПЧ (фиг. 2и) от начальной, но не изменят числа синхроимпульсов с выхода формирователя 4 синхросигнала (фиг. 2v) . По- следнее объясняется тем, что сигнал коррекции от первого же не пораженного информационного нуля(фиг. 2е) поступает на установочный вход первого делителя 2 частоты на два и устанавливает (или подтверждает) правильное значение его фазы по отношению к фазе информационных символов. Цепь коррекции вырабатывает сигнал коррекции строго по истечении 0,75 периода средней частоты следования и не зависит от дрейфа параметров элементов его составляющих и изменения средней частоты следования информации. Точность поддержания порога различения определяется соотношением 2п ° Предлагаемое устройство синхронизации характеризуется однозначностью начальной фазы синхросигнала после вхождения устройства в синхронизм, неизменностью числа синхросигналов между кодами групповой синхронизации, а так же исключением потерь информагщи, обусловленных спонтанными скачками фазы в процессе приема сигнала.

6/tOft Kopjye/ftft/t/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации | 1978 |

|

SU790356A1 |

| Устройство для воспроизведения цифровых сигналов с магнитного носителя | 1990 |

|

SU1737508A1 |

| Синхрогенератор | 1987 |

|

SU1555908A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Устройство фазовой автоподстройки частоты | 1984 |

|

SU1352645A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство синхронизации | 1982 |

|

SU1083392A1 |

| Устройство синхронизации | 1983 |

|

SU1095435A1 |

| Устройство для ступенчатой развертки луча электронно-лучевой трубки | 1980 |

|

SU1023639A1 |

УСТРОЙСТВО СИНХРОНИЗАЦИИ, содержащее формирователь нулевых пересечений, выход которого подключен к установочному входу первого делителя частоты на два, к счетному входу которого подключен выход формирователя сигнала коррекции, а выход первого делителя частоты на два через блок фазовой автоподстройки частоты (ФАПЧ) подключен к входу формирователя синхросигнала, о т л и ч а rant е е с я тем, что, с целью повьшения точности синхронизации при дрейфе частоты следования сигнала, введены последовательно соединенные делитель частоты на п/2 (где п/2 « 1,2,3,..., п/2), второй делитель частоты на два и элемент И, выход ко торого подключен к входу формирователя сигнала коррекции, а к второму входу элемента И подключен выход делителя частоты на п/2, к установочному входу которого, а также к (Л установочному входу второго делитес ля частоты на два подключен выход формирователя нулевых пересечений, а к счетному входу делителя частоты на 1Л /2 подключен дополнительный выход блока ФАПЧ.

..«««..-.«-J

Фи.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Формирователь опорной частоты | 1972 |

|

SU457183A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство синхронизации | 1978 |

|

SU790356A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-08-07—Публикация

1983-12-09—Подача