1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при исследовании устройств и систем автоматического управления на физических моделях и аналого1вых вычислительных машинах с учетом случайных возмущений.

Известны генораторы -случайных чисел, основанные «а нересчете случайных импульсов за фнксированный интервал времени. Один из известных генераторов случайных чисел сод&ржит источник случайного потока имлульсов, ключ, счетчик, регистр памяти, источник регулярных импульсов.

Основным недостатком этото генератО|ра является то, что он не позволяет воспроизводить задаваемые закОПЫ распределения случайных чисел.

Наиболее близким техническим рен1ением к изобретению является ге-иератор случайных чисел, содержащий первичный источник случайных импульсов, выход которого через блок формирования подключен к первому входу элемента И, распределитель импульсов, вход которого соединен с выходом блока управления, матричный переключатель, выход которого является выходом генератора.

Недостаточные стабильность и точность такого генератора объясняются наличием амплитудного селектора, выполняемого на пороговых устройствах, чувствительных к внешним возмущениям.

Цель изобретения - повышение стабильности и точности генератора.

Для этого предлагаемый генератор дополнительно содержит последовательно включенные между выходом элемента И и входом матричного переключателя счетчик, регистр памяти и дешифратор, при этом второй вход

элемента И соединен с выходом элемента -памяти, первый вход -которого соединен с четвертым выходом распределителя импульсов, первый, второй и третий выходы которого соответственно соединены с вторыми входами

элемента иамяти, регистра памяти и счетчика.

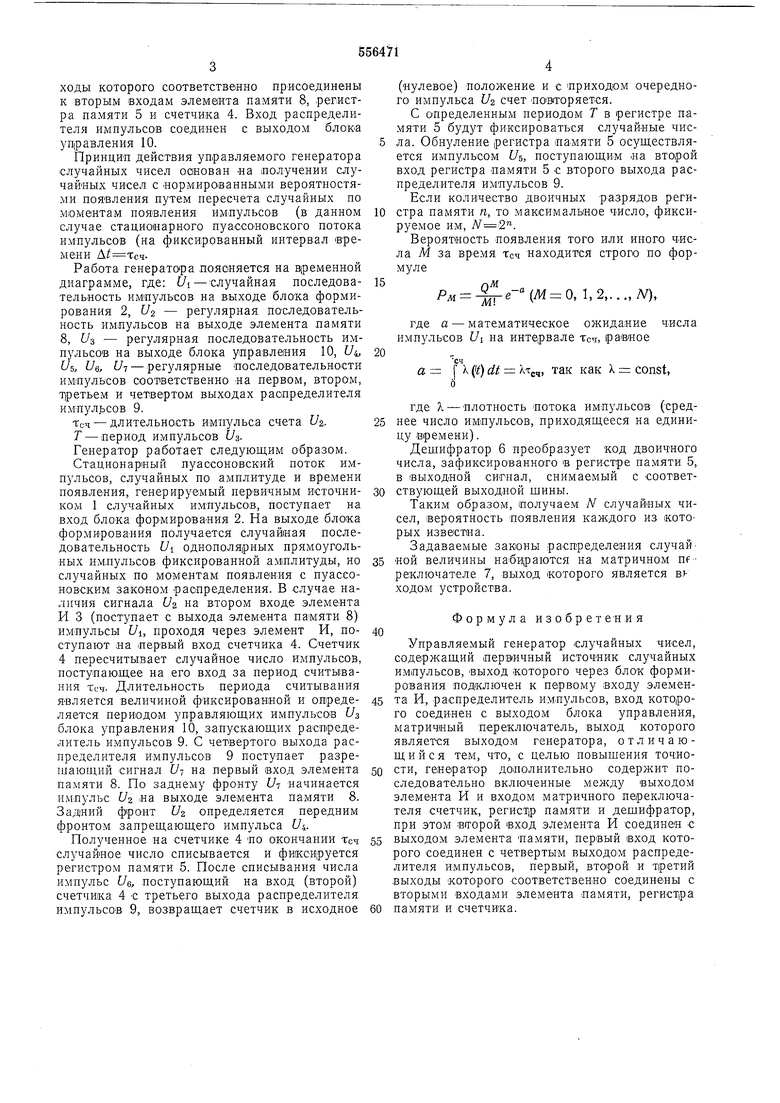

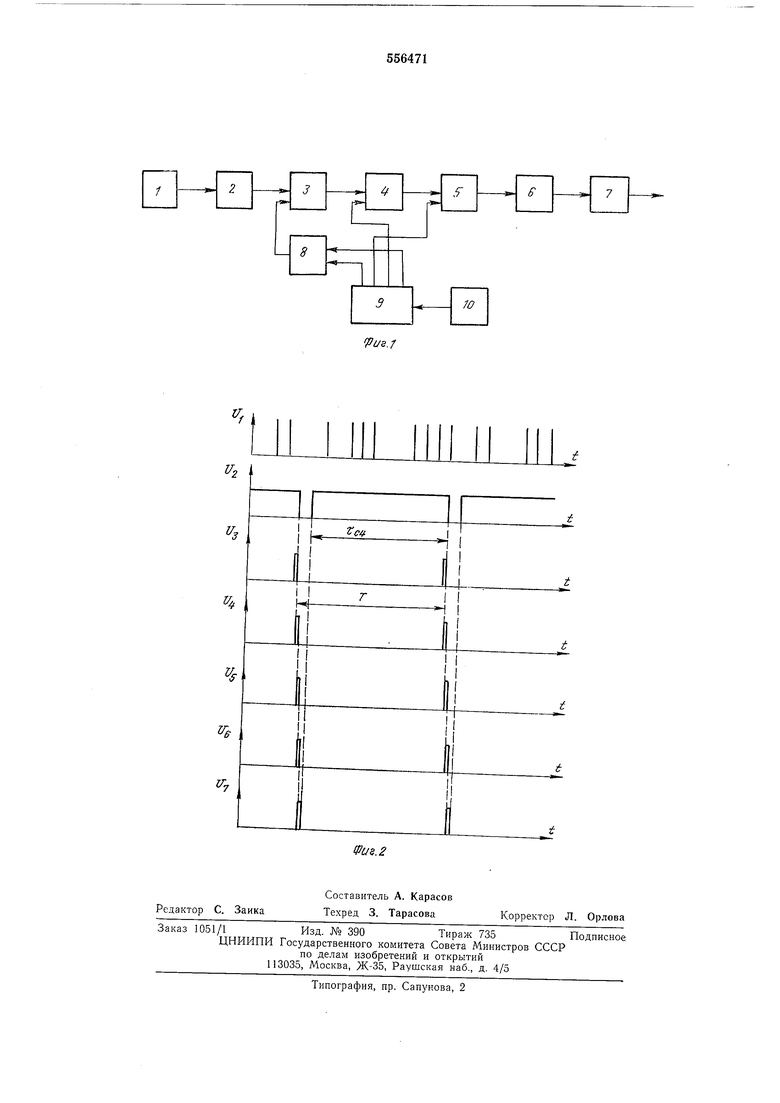

На фиг. 1 изображена структурная схема предлагаемого генератора случайных чисел; на фиг. 2 - временная диаграм-ма работы генератора.

Устройство включает в себя -последов-ательно -соединенные первичный источник 1 случайных импульсов, блок формирования 2, элемент И 3, счетчик 4, регистр памяти 5, дешифратор 6 и матричный пере-ключатель 7. Второй вход элемента И соединен с выходом элемента памяти 8, первый вход которого .присоединен к четвертому выходу распределителя импульсов 9, первый, второй и третий выходы которого соответственно присоединены к вторым входам элеме;нта памяти 8, .регистра памяти 5 и счетчика 4. Вход распределителя импульсов соединен с выходом блока уцравления 10. Принцип действия управляемого генератора случайных чисел основан «а получении случайных чисел с -нормированными вероятностями появления путем пересчета случайных по моментам появления импульсов (в данном случае стационарного пуассоновского потока импульсов (на фиксированный интервал времени А/ ТСЧРабота генератора поясняется на временной диаграмме, где: f/i - случайная последовательность импульсов на выходе блока формирования 2, f/2 - регулярная последовательность импульсов на выходе элемента памяти 8, f/3 - регулярная последовательность импульсов на выходе блока управления 10, t/4, f/s, 6, f/7 - регулярные последовательности импульсов соответственно на первом, втором, третьем и четвертом выходах распределителя импульсов 9. tc4 - длительность импульса счета Uz. Т - период импульсов UzГенератор работает следующим образом. Стационарный луаосоновскпй поток импульсов, случайных по амплитуде и времени появления, генерируемый первичным источником 1 случайных импульсов, поступает на вход блока формирования 2. На выходе блока формирования получается случайная последовательность f/i однополярных прямоугольных импульсов фиксированной амплитуды, но случайных по моментам появления с пуассоновским законом распределения. В случае наличия сигнала Uz на втором входе элемента И 3 (поступает с выхода элемента памяти 8) импульсы Ui, проходя через элемент И, поступают на первый вход счетчика 4. Счетчик 4 пересчитывает случайное число импульсов, поступающее на его вход за период считывания тсч. Длительность периода считывания является величиной фпксированной и определяется периодом управляющих импульсов f/з блока управления 10, запускающих распределитель импульсов 9. С четвертого выхода распределителя импульсов 9 поступает разрешающий сигнал Uj на первый вход элемента памяти 8. По заднему фронту U-; начинается импульс f/2 на выходе элемента памяти 8. Задний фронт f/2 определяется передним фронтом запрещающего импульса U. Полученное на счетчике 4 по окончании тсч случайное число списывается и фиксируется регистром памяти 5. После списывания числа импульс Ue, поступающий на вход (второй) счетчика 4 с третьего выхода распределителя импульсов 9, возвращает счетчик в исходное (нулевое) положение и с приходом очередного импульса t/2 счет повторяется. С определенным периодом Т в регистре памяти 5 будут фиксироваться случайиые числа. Обнуление регистра памяти 5 осуществляется импульсом и, поступающим «а второй вход регистра памяти 5 с второго выхода распределителя импульсов 9. Если количество двоичпых разрядов регистра памяти п, то максимальное число, фиксируемое им, . Вероят1ность появления того или иного числа М за время Точ находится строго по формуле . ,- /лл - e-(M 0,l,2,...,N), где а - математическое ожидание числа импульсов Ui на интервале Тсч, равное f4 ). с/) dt - Хтд,, так как X const, о где X - плотность потока импульсов (среднее число импульсов, приходящееся на единицу -времени). Дещифратор 6 преобразует код двоичного числа, зафиксированного в регистре памяти 5, в выходной сигнал, снимаемый с соответствующей выходной шины. Таким образом, получаем Л случайных чисел, вероятность появления каждого из которых известна. Задаваемые законы распределения случайной величины набираются на матричном nf реключателе 7, выход которого является в.ходом устройства. Формула изобретения Управляемый генератор случайных чисел, содержащий первичный источник случайных импульсов, выход которого через блок формирования подключен к первому входу элемента И, распределитель импульсов, вход которого соединен с выходом олока управления, матричный переключатель, выход которого является выходом генератора, отличающийся тем, что, с целью повышения точности, генератор дополнительно содержит последовательно включенные между выходом элемента И и входом матричного переключателя счетчик, регистр памяти и дешифратор, при этом второй вход элемента И соединен с выходом элемента памяти, первый вход котоого соединен с четвертым выходом распределителя импульсов, первый, второй и третий ыходы которого соответственно соединены с вторыми входами элемента памяти, регистра амяти и счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайныхчиСЕл | 1979 |

|

SU822162A1 |

| Многоканальный генератор случайных чисел | 1975 |

|

SU534775A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU962935A1 |

| Устройство для моделирования процессов изменения параметров электронных схем | 1980 |

|

SU924712A1 |

| Управляемый генератор потоков случайных событий | 1975 |

|

SU543964A1 |

| Устройство для тренировки операторов | 1989 |

|

SU1647621A1 |

| Генератор случайного потока случайных чисел | 1980 |

|

SU926656A1 |

| Устройство для моделирования деятельности человека-оператора | 1990 |

|

SU1783541A1 |

| Устройство для имитации помех | 1978 |

|

SU758545A1 |

| Устройство для моделирования отказов в сложных системах | 1987 |

|

SU1432549A2 |

Авторы

Даты

1977-04-30—Публикация

1974-10-07—Подача