: Изобретение относится к вычислительной технике Иоможет быть использовано при исследовании и оценке надежности по постепенным перемещающимся отказам низкочастотных электронных схем, находящихся под влиянием внешних воздействий, на стадии, их проектирования, опытной отработки .: и крупносерийного производства.

Известны устройства для физического моделирования процессов изменения выходных параметров электронных схем, содержащие блоки задания начальных значений параметров и скоростей их изменения, а также блоки памяти чисел и коэффициентов, сумматоры, регистЕЖл, блоки умножения, элементы И, ИЛИ, наборные поля 1.

Недостатком известных устройств является низкая точность моделироваНИН изменения параметров электронных схем.

Наиболее близким по технической сущности к предлагаемому является устройство для моделирования процессов изменения параметров электронных схем, содержащее датчик равномерно рс1спределенных случайных чисел, дешифратор, блоки задания начальных значений параметров и блоки

задания скоростей изменения параметров, элемент ИЛИ, элемент И, генератор, счетчики Пс-мяти, элемент обратной связи, коммутатор, блок управления, датчик равнсмерно распределенных случайных чисел, датчик нормально распределенных случайных чисел, блоки памяти чисел, блоки памяти коэффициентов, блоки умножения,

10 сумматоры, регистры, генераторы тактовых импульсов переменной частоты, реверсивные счетчики 2.

Недостатком известного устройства является низкая точность модели15рования.

Цель изобретения - увеличение точности моделирования процессов изменения параметров электронных схем.

Поставленная цельдостигается бла20годаря тому, что в устройство для моделирования процессов изменения параметров электронных схем, содержащее датчик равномерно распределенных случайных чисел, выход которого

25 соединен со входом дияифратора, выход которого подключен к первым входам блоков задания начальных значений параметров и к первым входам блоков задания скорости изменения

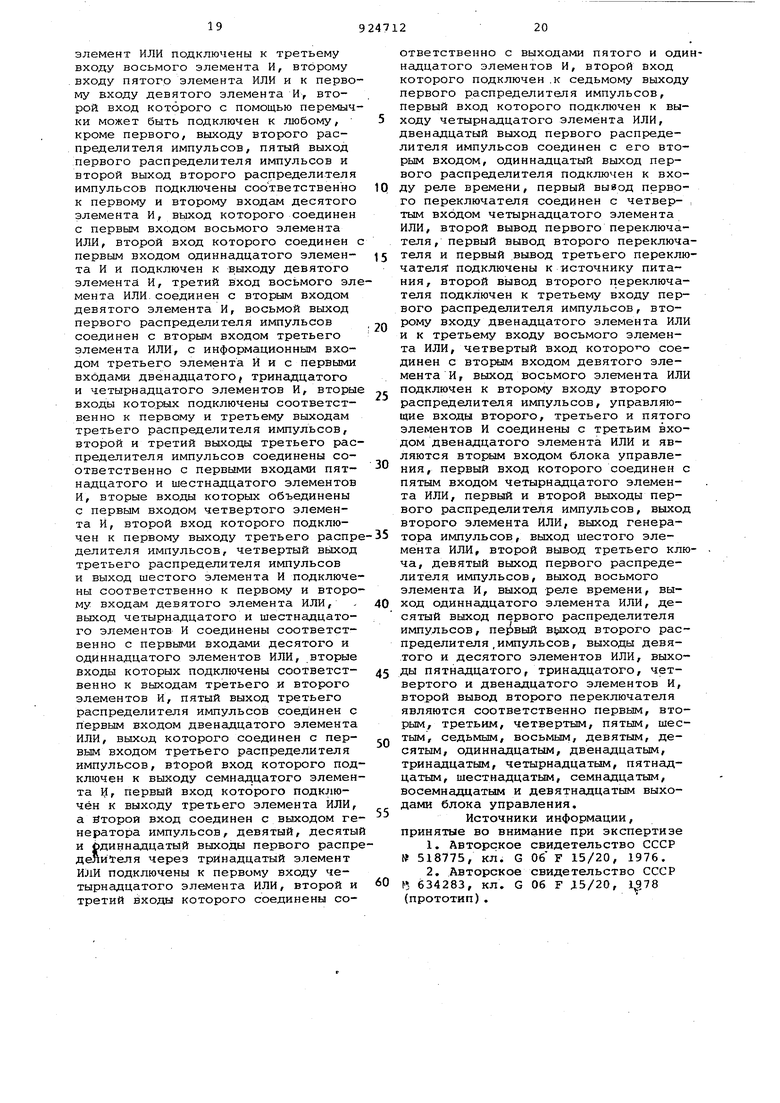

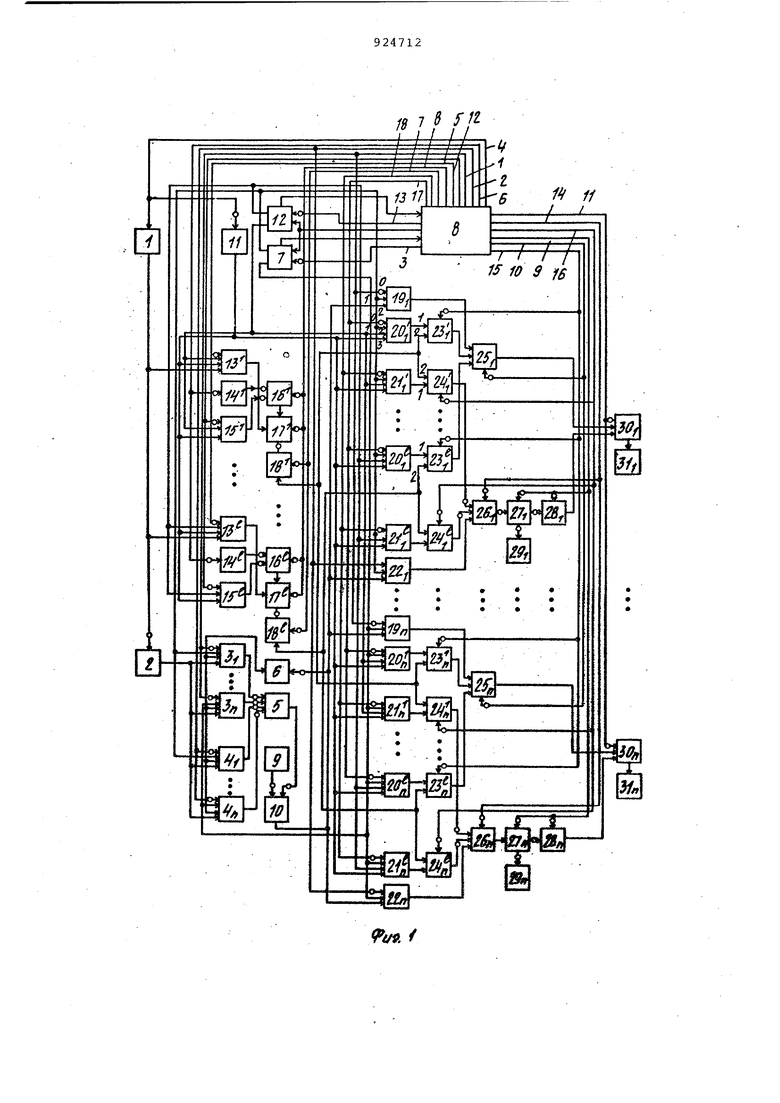

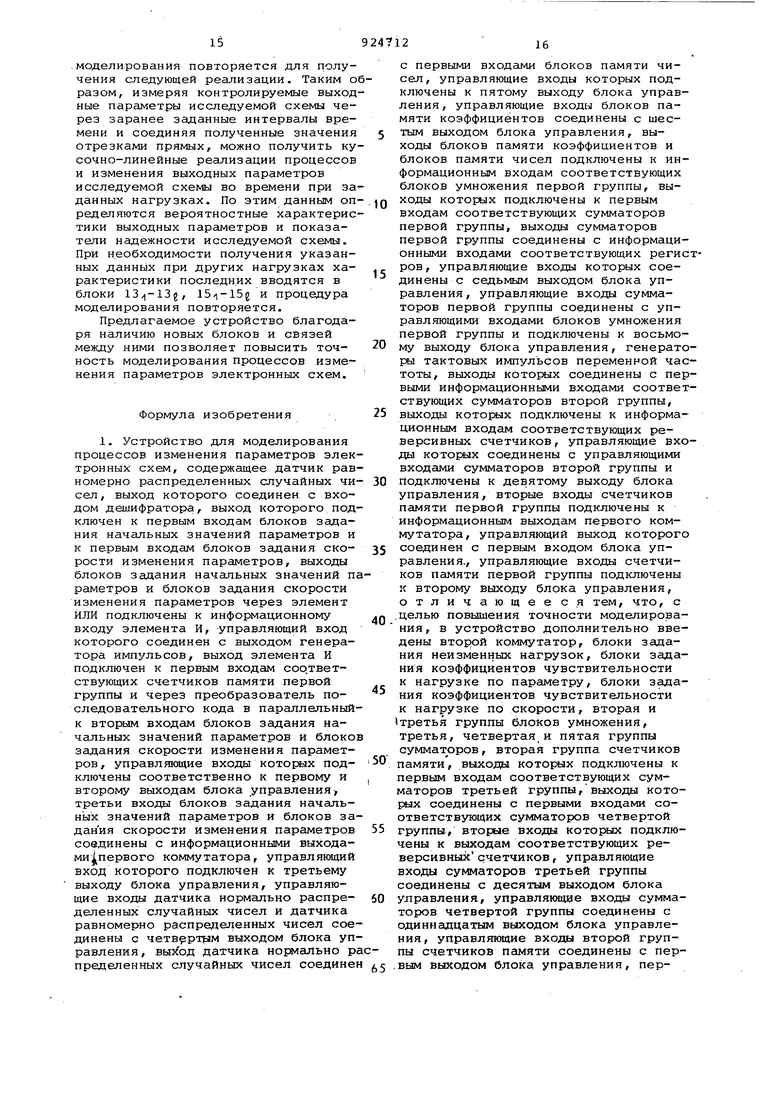

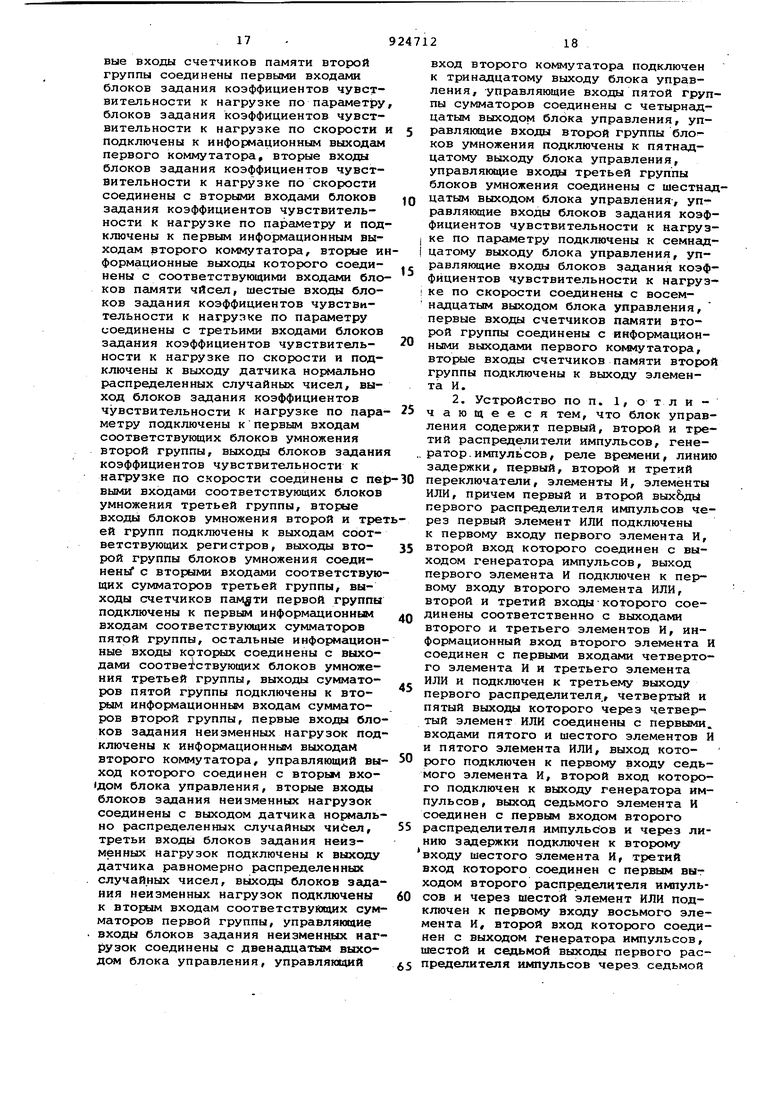

30 параметррв, выходы блоков задания начальных значений параметров и блоков задания скорости изменения параметров через элемент ШШ подключен к информационному входу элемента И, управляющий вход которого соединен с выходом генератора импульсов, выход элемента И подключен к первым входам соответствующих счетчиков iпамяти первой группы и через элемент обратной связи ко вторым входам блоков задания начальных значений параметров и блоков задания скорости изменения параметров., управляющие входы которых подключены к выходу блока управления, третьи входы блоко задания начальных значений параметров и блоков задания скорости изменения параметров соединены с выходом первого коммутатора, управляющий вхо Которого соединен с управляющим входом датчика нормально распределенных случайных чисел и подключен к выходу блока управления, выход датчика нормально распределенных случайных чисел соединен с первыми входами блоков памяти чисел, управляющие входы которых соединены с управляющими входами блоков памяти коэффициентов и подключены к выходу блока управления, выходы блоковпамяти коэффициентов и блоков памяти чисел подключе ны к информационным входам соответствующих блоков умножения первой группы, выходы которых подключены к первым входам соответствующих сумматоров первой группы, выходы сумматоров первой группы соединейы с информационными входами соответствую щих регистров,- управляющие входы которых соединены с управляющими входами сумматоров первой группы, с управляющими входами блоков умножения первой группы и подключены к выходу блока управления генератогжл тактовых импульсов переменной частоты, выходы которых соединены с первыми информационными входами соответствующих сум маторов второй группы, выходы которых подключены к информационным входам соответствующих реверсивных счет чиков, управляющие входы которых сое динены с управляющими входами сумматоров второй группы и подключены к выходу блока управления, вторые входы счетчиков памяти первой группы подключены к выходу первого коммутатора, управляющие входы счетчиков памяти первой Группы соединены с выходом блока управления, дополнител но введены второй коммутатор, блоки заданиянеизменных нагрузок, блоки задания коэффициентов чувствительности к нагрузке по параметру, блоки задания коэффициентов чувствитель ности к нагрузке по скорости, вторая и третья pyппы блоков умножения третья;, четвёртая и пятая группы сумматоров, вторая группа счетчиков памяти, выходы которых подключены к первым входам соответствующих сумматоров третьей группы, выходы кото-, рых соединены с первыми входами соответствующих сумматоров .четвертой группы, вторые входы которых подключены к вы додам соответствующих реверсивных счетчиков, .управляющие входы сумматоров третьей и четвертгэй групп и второй группы счетчиков памяти соединены с выходом блока синхронизации, первые входы счетчиков .памяти второй группы соединены с первыми (Входами блоков задания.коэффициентов чувствительности к нагрузке по параметру, блоков задания коэффициентов чувствительности к нагрузке по скорости и подключены к выходу первого коммутатора, вторые входы блоков Заданна коэффициентов чувствительности к погрузке по скорости соединены со вторыми входами блоков задания коэффициентов чувствительности к нагрузке по параметру и подключены к выходу второго коммутатора, третьи входы блоков задания коэффициентов чувствительности к нагрузке по параметру соединены с третьими входами блоков задания коэффициентов чувствительности к нагрузке по скорости и подключены к выходу датчика нормально распределенных случайных чисел, выход блоков задания коэффициентов чувствительности к нагрузке по параметру подключены к первым входам соответствующих блоков умножения второй, группы, выходы блоков задания коэффициентов.чувствительности к нагрузке по скорости соеди 1ены с п.ервыми входами соответствующих блоков умножения третьей группы, вторые входы блоков умножения второй и третьей групп подключены к выходам соответствующих регистров, выходы второй группы блоков умножения соединены со. вторыми входами соответствующих сумматоров третьей группы, выходы счетчиков памяти первой группы подключены к первым.информационным входам соответствующих сугиматоров пятой группы, остальные информационные входы которых соединены с выходами соответствующих блоков умножения третьей группы, выходы сумматоров пятой группы подключены ко вторым информационным.входам сумматоров второй группы,первые входы блоков задания неизменных нагрузок подключены к выходу второго коммутатора,вторые входы блоков задания неизменных нагрузок соединены с выходом датчика нормально распределенных случайных чисел, третьи входы блоков задания неизменных нагрузок подключены к. ВЫХОДУ датчика равномерно распределенных случайных чисел выходы блоков задания неизменных нагрузок подключены ко вторым входам соответствующих сумматоров первой группы, управляющие входы блоков, задания неизменных нагрузок соединены с управляющими входами второго коммутатора с управляющими входами пятой группы сумматоров с управляющими входами второй и третьей групп блоков умножения , управляющими входами блоков задания коэффициентов чувствительности к нагрузке по параметру, управляющими входами блоков задания коэффициентов чувствительности к нагрузке по скорости, управляющими входами блоков задания неизменных нагрузок и подключены к выходу бло1ка синхронизации, первые входы счет- 5 чиков памяти второй группы соединены с выходом первого коммутатора, вторы входы счетчиков памяти второй группы подключены к выходу элементов И. Блок управления содержит первый, второй и третий распределители импульсов, генератор импульсов, реле .времени, линию задержки, первый, вто рой и третий переключатели, элементы И, элементы ИЛИ, причем первый и второй выходы первого распределителя импульсов через первый элемент .ИЛИ подключены к первому входу первого элемента И, второй вход которого соединен с выходом генератора импульсов, выход первого элемента И подключен к первому входу второго элемента ИЛИ, второй и третий входы которого соединены соответственно с выходами второго и третьего элемен тов И, информационный вход второго элемента И соединен с первыми входами четвертого элемента И и третьего элемента ИЛИ и подключен к третьему выходу первого раагределителя, четвертый и пятый выходы которого через четвертый элемент ИЛИ соединены с первыми входами пятого и шестого элементов И и пятого элемента ИЛИ/ выход которого подключен к первому входу седьмого элемента И, второй вход которого подключен к выходу генератора импульсов, выход седьмого элемента и соединен с первым входом второго распределителя импульсов и через линию задержки подключен ко второму входу шестого элемента И, третий вход которого соединен с первым выходом второго распределителя импульсов и через шестой, элемент ИЛИ подключен к первому входу восьмого элемента И, второй вход которого соединен с выходом генератора импульсов, шестой и седьмой выходы первого распределителя импульсов через седьмой элемент ИЛИ подключены к третьему входу восьмого элемента второму входу пятого элемента ИЛИ и к первому входу девятого элемента И, второй вход которого с помощью перемычки может быть подключен к любому, кроме первого, выходу второго распределителя импульсов, пятый выход первого распределителя импульсов и второй выход второго распределителя импульсов подключены соответственно к первому и второму входам десятого элемента И, выход которого соединен с первым входом восьмого элемента ИЛИ, второй .вход которого соединен с первым входом одиннадцатого элемента И и подключен к выходу девятого элемента И, третий вход восьмого элемента ИЛИ соединен со вторым входом девятого элемента И, восьмой выход первого распределителя импульсов соединен вторым входом третьего элемента «ИЛИ, с информационным входом третьего элемента И и с первыми входами-, двенадцатого, тринадцатого и четырнадцатого элементов И, вторые входы которых подключены соответственно к первому, второму и третьему входам третьего распределителя импульсов, второй и третий входы третьего распределителя импульсов соединены соответственно с первыми входами пятнадцатого и шестнадцатого элементов И, вторые входы которых объединены с первым входом ч,етвертого элемента И, второй вход которого подключен к первому выходу третьего распределителя импульсов, четвертый выход третьего распределителя импульсов и выход шестого элемента И подключены соответственно к первому и второму входам девятого элемента ИЛИ, выходы четырнадцатого и шестнадцатого элементов И соединены соответственно с первыми входами десятого и одиннадцатого элементов ИЛИ, вторые входы которых подключены соответственно к выходам второго и третьего элементов И, пятый вьаход третьего распределителя и fflyльcoв соединен с первым входом двенадцатого элемента ИЛИ, выход кото{зого соединен с первым входом третьего распределителя импульсов, второй вход которого подключен к выходу семнадцатого элемента И, первый вход которого подключен к выходу третьего элемента ИЛИ, а второй вход соединен с выходом генератора импульсов, девятый, десятый и одиннадцатый выходы первого распределителя через тринадцатый элемент ИЛИ подключены к первому входу четырнадцатого элемента ИЛИ, второй и третий входы которого соединены соответственно с выходами пятого и одиннадцатого элементов И, второй вход которого подключен к седьмому выходу первого распределителя импульсов, первый вход которого подключен к выходу четырнадцатого элемента ИЛИ, двенадцатый выход первого распределителя импульсов соединен с его вторым входом, одиннадцатый выход первого распределителя подключен ко входу реле времени, первый выход первого переключателя соединен с четвертым входом четырнадцатого элемента ИЛИ, второй вывод первого переключателя, первый вывод второго переключателя и первый вывод третьего переключателя подключены к источнику питания, второй вывод второго переключателя подключен к третьему входу первого распределителя импульсов, второму входу двенадцатого элемента ИЛИ и к третьему входу восьмого элемента ИЛИ, четвертый вход которого соединен со вторым входом девятого элемента И, выход восьмого элемента ИЛИ подключен ко второму входу второго распределител импульсов, управляющие входы второго, третьего и пятого элементов И соединены с третьим входом двенадцатого элемента ИЛИ и являются входом блока управления, первый вход которого соединен с пятым входом четырнадцатого элементов ИЛИ/ первый и второй выходам первого распределителя импульсов, выход второго элемента ИЛИ, выход генератора импульсов, выход шестого элемента ИЛИ, второй вывод третьего ключа, девятый выход первого распределителя импульсов, выход восьмого элемента И, выход ре ле времени, выход одиннадцатого эле мента ИЛИ, десятый выход первого распределителя импульсов, первый вы ход второго распределителя импульсов , выходы девятого и десятого эле ментов ИЛИ, выходы пятнадцатого, три надцатого, четырнадцатого и двенадцатого элемедтов И, второй вывод второго переключателя являются соответственно первым, вторым, третьим, четвертым/ пятым, шестым, седьмым, восьмым, девятым, десятым, одиннадцатым, двенадцатым, тринадцатым, четырнадцатым, пятнадцатым, шестнадцатым, семнадцатым, восемнадцатым и девятнадцатым выходами блока управления. На фиг. 1 представлена схема блока управления на фиг. 2 - схема блока коммутаторов. Устройство содержит датчик 1 равномерно распределенных случайных чисел, дешифратор 2, блок зад1ания начальных значений параметров, блоки 4/1-4 г, задания скоростей изменения параметров, элемент ИЛИ 5, элемент б обратной связи, коммутатор- 7, блок 8 управления, генератор 9, /элемент И 10, датчик 11 нормально распределенных случайных чисел, коммутатор 12, блоки 13 i-13g задания неизменных нагрузок, блоки памяти коэффициентов, блоки 15-,-15g памяти чисел, блоки умножения, накапливающие сумматоры регистры l8,-l8g, счетчики памяти, блоки20 -20 задания коэффициентов чувствительности к нагрузке по параметру, блоки задания коэффициентов чувствительности к нагрузке по СКОРОСТИ, счетчики памя:ри,блоки умножения,блоки 24х|-24п умножения,сумматоры 25-1 -25л ,сумматоры 26-,-2б„/сумматоры 27,-27ц ,реверсивные счетчики , генераторы , тактовых импульсов переменной частоты,сумматоры- , наборные поля . Блок 8 управления содержит генератор 32 тактовых импульсов, элемент ИЛИ 33, элемент И 34, элемент ИЛИ 35, элемент И 36, элемент ИЛИ 37, элемент И 38, элемент ИЛИ 39, элемент И 40, элементы ИЛИ 41 и 42, распределитель 43, элементы ИЛИ 44 и 45/ элемент И 46, реле 47 времени/ элемент И 48, элемент 49 задержки/ элемент ИЛИ 50, элементы И 51,52, элементИЛИ 53, распределитель 54, элемент И 55, элемент ИЛИ 56, элементы И 57,58, элемент ИЛИ 59. элемент И 60/ элемент ИЛИ 61, распределитель 62/ элементы И 63-68, коммутатор 7 содержит распределитель 69 на регистре, элемент 10 ИЛИ. Коммутатор 12 содержит распределитель 71 на регистре/ элемент ИЛИ 72. Выводы блока 8 управления соединены соответственно с входом датчиков. 1 и 11, с управляющим входом коммутатора 7/ с управляющими входами накапливающих сумматоров с управляющими входами накапливающих сумматоров 26-1-26и / с входами блоков , ,/ с, управляющими входами блоков и накапливающих сумматоров , с управляющими входами регистров l8/,-l8g/ с управляющими входами сумматоров 30/1-30„/ с управляющими входами сумматоров 27/,-27„ Iреверсивных счетчиков 28xj-28f,, с управляющими входами коммутатора,12/ с входами блоков 13/1-13f/ с входами блоков / с входами блоков 14 -14g/ с входами блоков. 22 -20fl, с входами блоков ,, с управляющими входами блоков с управляющими входами блоков , с входами Исходное коммутаторов 7 и 12 с n+1-ым выходом коммутатора 7, с 2+1-м.выходом коммутатора 12, (22+п) с соответствующими входами блоков 4/,-4п/ счетчиков 19/, с входами счетчиков 21.-22., блоков ()(20;-20|). Устройство работает следуюнщм образом. Перед началом моделирования в блоках 3-1-Зп/ 4-1-4 набираются соотГJeтcтвyющиe законы рарпределения начальных значений и скоростей изменения параметров при номинальных нагрузках. В блоки 13 1-13{ вводятся значения детерминированных нагрузок или характеристики законов распределения случайных нагрузок с указанием признака закона. В блоки заносятся по m заданных коэффициентов, характеризуюощх корреляционную функцию флуктуационной составляющей нагрузки. В блоки. 201|-20, и 2l, вводятся характеристики законов распределения коэффициентов чувствитель ности к нагрузке. Устанавливается рабочая частота каждого из генераторов 29-1-29 п. На наборных полях устанавливаются упорядоченны ряды элементов. Командой из блока b устройство приводится в исходное положение. В начале цикла моделирования каждой реализации процесса изменения выходных параметров исследуемой схемы производятся две подготовительные операции: аерпая - формирование начальных значений и скоростей изменения параметров элементов при но- минальных нагрузках; вторая - формирование значений нагрузок, соответ ствующих моменту времени tg. Для этого по команде из блока 8 дается разрешение на прохождение сигналов в блоки Зл-ЗпИ в ечетчики 19 -19. Коммутатор 8 устанавливается в первое положение, а в датчике 1 формируется случайное число, которое через дешифратор 2 поступает на вход блока 3. Для получения заданного I значения случайной величины преоб- разованное число с выхода блока 3 поступает через элемент 5 на элемен 10 и дает разрешение на прохождение регулярных импульсов с генератора 9 на элемент 6 обратной связи и на счетчик 19. При совпадении в блоке 3 сигнала, соответствующего сформированной вероятности, и сигнала, поступающего с элемента б, снимается разрешение на прохождение импульсов через элемент 10 и прекращается поступление импульсов на счетчик 19-|. Таким образом в счетчик 19 заносит ся число, соответствующее начальном значению параметра первого элемента при номинальных нагрузках. Затем по команде из блока 8 коммутатор 7 переключается во второе положение и в датчике 1 формируется новое случайное число, которое через дешифратор 2 поступает на вход блока Зг1 и далее преобразуется описанным выше образом. А результате преобразования в счетчике 19 г фиксируется число, соответствующее начальному значению параметра второго элемента при номинальных нагрузках. После переключения коммутатора 7 в оставшиеся п-2 положения во все счет чики будут занесены числа, . соответствующие начальным значениям парс1метров соответствующих элементов при номинальных нагрузках. Для получения значений скоростей изменения параметров элементов при номинальных нагрузках по команде из блока 8 снимается разрииение на прохождение сигналов в блоки 3 -3 счетчики и дается разрешение на прохождение сигналов в блоки и счетчики . Аналогично описанному вьше, при переклк)чении коммутатора 7 в каждый из счетчиков заносится число в соответствии с вероятностью, сформированной в соответствующем блоке 4 -4 i Таким образом, после окончания работы коммутатора в счетчики оказываются занесенными числа, соответствующие начальным значениям, а в счетчики - числа, соответствующие скоростям изменения парамет- ров элементов при номинальных нагрузках., Для формирования значений нагрузок, соответствующих моменту времени tg, по команде из блока 8 снимается разрешение на прохождение сигналов в блоки 4 -4 j, счетчики 22,,-22, и дается разрииение на прохождение сигналов в блоки 13/J-13E ,15/,-15 еПо команде из блока 8 коммутатор 12 устанавливается в первое положение, а в датчиках 1 и 11 формируется по одному случайному числу, которые поступают на входь. блока 13-, , гДе одно из них преобразуется в значение неизменной во времени нагрузки. Затем в блок 15- заносится последовательно m чисел от датчика 11 для чего блок 8 выдает последовательно m команд на выработку этих чисел в датчике 11 и на сдвиг чисел в блоке . После этого по команде из блока 8 коммутатор 12 переключается во второе положение и в датчиках Г и 11 формируются новые случайные числа, которые аналогичным образом заносятся в блоки 13(2 и ISij. -Точно также при переключении коммутатора 12 в остальные 2-2 положений заносятся случайные числа в остальные блоки , . Затем из блока 3 выдаются команды на последовательное перемножение пар чисел одновременно во всех блоках с накоплением результатов в соответствующих накапливающих сумматорах , где образуются значения нагрузок, соответствующие моменту времени tg, После завершения подготовительных операций устройство работает в полуавтоматическом режиме. При этом для получения значений выходных параметров исследуемой схемы в момент времени tj() выполняются следующие операции: по команде оператора числа, соответствующие значениям нагрузок, в момент времени tj , вводятся в регистры 18 -18g; формируются значения параметров элементов в момент времени tj без учета изменен на отрезке времени utj и затем полу ченные значения суммируются с изменениями параметров за указанный отрезок времени; измеряются значения контролируемых выходных параметров исследуемой схемы; формируются значения скоростей изменения парс1мет- ров элементов в момент времени t: и моделируется их изменение на отрезке времени At j+i Формируются :я значения нагрузок, соответствующие моменту времени tj+. Для получения значейий параметров элементов в момент времени по команде оператора, выдаваемой через блок 8, числа, соответствующие значениям нагрузок в момент времени tg переносятся-из накапливающих Сумматоров в соответствующие регистры . Затем командой из блока 8 дается разрешение на прохождение сигналов в блоки , коммутаторы 7 и 12 устанавливаются в первое положение, а в датчике 11 формируется случайное число, которое поступафг на вхо блока где преобразуется в числ соответствующее коэффициенту чувствительности к нагрузке по параметру Это число по команде из блока 8 перемножается в блоке 23 с числом из регистра 18,, и полученное произведение по следующей команде из блока 8 поступает на вход накапливающего сумматора 25. Затем коммутатор 12 переключается во второе положение и в датчике 11 вырабатывается новое случайное число, которое поступает на вход блока 20, где преобразуетс аналогично предыдущему. По следующим командам из блока 8 число с выхода блока 20 перемножается в блоке 23 с числом из регистра и полученный результат прибавляется, к содержимому накапливающего сумматора 25, Точно также при переключении коммутатора 12 в остальные -2 положений к содержимому накапливающего сумматора 25 прибавляются оставшиеся В-2 произведений. Результат накопления суммируется с числом из счетчика 19. Затем по команде из блока 8 коммутатор 7 устанавливается во второе положение, а коммутатор 12 - в первое, в датчике 11 формируется новое случайное число,- которое преобразует я в блоке 20 Q. Полученный резульTaf йеремножается в блоке 23 с чис лом из регистра 18i и произведение поступает на вход.накапливающего сумматора 25г. При переключении коммутатора 12 в оставшиеся t-i положе ния к содержимому данного накапливающего сумматора прибавляются произведения, полученные в остальных 1-1 блоках , и число из счетчика 19 (. Аналогичным образом при переключении коммутатора 7 в оставшиеся п-2 положений во всех остальных п-2 накапливающих сумматорах 25,-25, образуются числа, соответствующие значениям параметров элементов в момент времени tg. По следующей команде из бЛока 8 одновременно во всех сумматорах 30-1-ЗОп происходит cy зv иpoвaниe чисел из соответствующих сумматоров 25-1-25 п и соответствующих счетчиков 28-,-28j,{B момент времени tg числа в этих счетчиках раны нулю), В соответствии с числами, полученными в сумматорах 30/|-ЗОп, в исследуемую схему подключаются по одному .элементу из совокупностей элементов, установленных на наборных полях п. Значения пара 1етров подключенных элементов соответствуют моменту времени t(j при нагрузках, соответствующих числам в регистрах . На исследуемую схему подается питание и измеряются значения ее контролируемых выходных параметров, соответствующие моменту времени tj. При этом могут быть зафиксированы значения параметров комплектующих элементов, соответствующие числам в сумматорах 30-(-ЗОл, и значения нагрузок, соответствующие числам в регистрах . В период измерения значений контролируемых выходных параметров исследуемой схемы работа устройства продолжается в автоматическом режиме. После суммирования чисел в сумматорах 30/(-30f| формируются значения скоростей изменения параметров элементов, соответствующие моменту времени tfl. По команде из блока 8 снимается разращение на прохождение сигналов в блоки 20;|-20 и даёт разрешение на прохождение сигналов в блоки , а коммутаторы 7 и 12,устанавливаются в первое положение. Затем в каждом из,положений коммутатора 7 коммутатор 12 переключается С раз. При этом по командам из блока 8 в датчике 11 формируются случайные чи лаг-Которые преобразуются в блоках в числа,соответствующие коэффициентам чувствительности элементов к нагрузкам по скорости.Полученные числа перемножаются в соответствующих блоках с числами из соответствующих регистров 18/|-18е и полученные произведения накапливается в соответствующих накапливающих сумматорах 26-1-2бн, куда также поступают числа из соответствующих счетчиков 22i-22f,.. После того, как коммутатор 7 проходит все положения, в накапливающих сумматорах хранятся числа, соответствующие скоростям изменения параметров элементов в момент времени tjj. Таким образом, формирование чисел в накапливающих сумматорах 26 1-26п происходит совершенно аналогично рассмотренному выше случаю образования чисел в накапливающих сумматорах 251-25 п. По следующей команде из блока 8 одновременно на все сумматоры начинают поступать импульсы от соответствующих генераторов 29ч-29т, Импульсы поступают в течение промежутк времени д4 . С приходом импульсов к содержимому сумматоров27-(-27 прибавляются числа из соответствующих накапливающих сумматоров 26-t-26n. Когда какой-либо из сумматоров 27)-2 переполняется, на его выходе появляется импульс, поступающий на соответствующий счетчик 28 -28fl. По истечении промежутка времени ,Д IB счетчиках 28-1-28п образуются числа, соответствующие изменениям параметров элементов за время fft и пропорциональные скоростям их изменения на указанном отрезке времени;Одновременно с началом отсчета интервала времени Д начинается формирование чисел ,соответствующих значениям нагрузок в.момент времени )Ц.По команде из блока 8 дается pfeis шение на прдхождение сигналов в бло , и коммутатор 12 ус танавливается в первое положение. При переключении коммутатора 12 на входы блоков 13-)-13g подается по одному случайному числу с выходов датчиков 1 и 11, которые преобразуются в числа, соответствующие неизменной во времени нагрузке. В кажды из блоков 15/|-15g заносится по одному случайному числу от датчика 11 Это число заносится по первому адресу, для чего числа, занесенные ранее, предварительно сдвигаются на один адрес, причем число, записанное по последнему адресу, теряется. Так как это описано выше для момента времени tg, при помсяди блоков 14 14J, 16i-16g, 17i-17g в последних формируются числа, соответствующие значениям нагрузок в момент времени t. После этого прекращаетсявы- дача всех команд из блока 8 и работа устройства приостанавливается. По окончании измерения значений контролируе№1х выходных параметров исследуемой схемы, соответствующих моменту времени t, оператором через блок 8 выдается команда на продолжение работы устройства. По этой коман де числа, соответствующие значениям нагрузок в момент времени t, переносится из накапливаняцих сумматоров 17/|-17g в соответствующие регистры . Затем, так как это описано выше для момента времени tg, при пот мощи датчиков 1 и 11, блоков , счетчиков 19/i-19n, накаляй вающих сумматоров , в по.следних формируются числа, соответствующие значениям параметров элементов в момент времени t, без учета их изменения во времени на отрезке &i, По следующей команде из блока 8 одновременно во всех сумматорах 30-tЗОл суммируются числа из соответствующих накапливающих сутиматоров и соответствующих счетчиков . В соответствии с полученными суммами в исследуемую схему подключаются новые элементы из рдцов, установленных на наборных полях 31х)-31„. Значения параметров подключенных элементов соответствуют моменту времени t при нагрузках, соответствующих числам в регистрах . После этого на исследуемую электронную схему подается питание и измеряются значения ее контролируекых выходных параметров, соответствующие моменту времени t. Одновременно, так как это описано выше для моментавремени tg, при помощи блоков , ,, счетчиков 22-t-22n и накапливающих сумматоров 26 -26fl в последних происходит формирование скоростей изменения параметров элементов соответ:твующих моменту времени t-j. Затем при помощи сумматоров 27-,-2/п, сч:етчиков 28t-28f,, генераторов моделируется изменение параметров элементов на отрезке времени Mj.. Числа, соответствующие указанным изменениям параметров, хранятся в счетчиках 28-(-28 о. Кроме того, с началом отсчета интервала времени ut(j по командам из блока 8 происходит формирование в накапливающих сумматорах 17 i-17g чисел, соответствующих нагрузкам в момент времени t(j. Формирование этих чисел происходит также, как это описано выше для момента времени t, при помощи блоков , J, 15-)15е , , накапливакнцих сумматоров . Затем прекращается выдача команд из блока 8 и работа устройства приостанавливается. После окончания измерений контролируемых выходных параметров для момента времени по команде оператора, выдаваемой через блок В,числа из накапливающих сумматоров переносятся в соответствующие регистрл 18-1-18J и работа устройства продолжается. ФоЕ шрованйе значений нагрузок и соответствующих значений параметров элементов для других моментов времени ,M) производится аналогично. После окончания измерений контролируемых выходных параметров исследуемой схемы для момента времени tf по команде оператора, вьвдаваемой через блок 8, устройство приводится в исходное положение и описанный цикл .моделирования повторяется для получения следующей реализации. Таким о разом, измеряя контролируемые выход ные параметры исследуемой схемы через заранее заданные интервалы времени и соединяя полученные значения отрезками прямых, можно получить ку сочно-линейные реализации процессов и изменения выходных параметров исследуемой схемы во времени при за данных нагрузках. По этим данным ОП ределяются вероятностные характерис тики выходных параметров и показатели надежности исследуемой схемы. При необходимости получения указанных данных при других нагрузках характеристики последних вводятся в блоки 13,-13g, и процедура моделирования повторяется. Предлагаемое устройство благодаря наличию новых блоков и связей между ними позволяет повысить точность моделирования процессов изменения параметров электронных схем. Формула изобретения 1. Устройство для моделирования процессов изменения параметров элек тронных схем, содержащее датчик рав номерно распределенных случайных чи сел, выход которого соединен с входом дешифратора, выход которого под ключен к первым входам блоков задания начальных значений параметров и к первым входам блоков задания скорости изменения параметров, выходы блоков задания начальных значений п раметров и блоков задания скорости изменения параметров через элемент ИЛИ подключены к информационному входу элемента И, управляющий вход которого соединен с выходом генератора импульсов, выход элемента И подключен к первым входам соо,тветствующих счетчиков памяти первой группы и через преобразователь последовательного кода в параллельный к вторым входам блоков задания начальных значений параметров и блоко задания скорости изменения параметров, управляющие входы которих подключены соответственно к первому и второму выходам блока управления третьи входы блоков задания начальных значений параметров и блоков за дания скорости изменения параметров соединены с информационными выходами первого коммутатора, управляющий вход которого подключен к третьему выходу блока управления, управляющие входы датчика нормально распределенных случайных чисел и датчика равномерно распределенных чисел сое динены с выходом блока уп равления, выу(од датчика нормально р пределенных случайных чисел соедине с первыми входами блоков памяти чисел, управляющие входы которых подключены к пятому выходу блока управления, управляющие ВХОДЕЛ блоков памяти коэффициентов соединены с шестым выходом блока управления, выходы блоков памяти коэффициентов и блоков памяти чисел подключены к информационным входам соответствующих блоков умножения первой группы, выходы которых подключены к первым входам соответствующих сумматоров первой группы, выходы сумматоров первой группы соединены с информационными входами соответствующих регистров, управляющие входы которых соединены с седьмым выходом блока управления, управляющие входы сумматоров первой группы соединены с управляющими входами блоков умножения первой группы и подключены к восьмому выходу блока управления, генератоЕм тактовых импульсов переменной частоты, выходы которых соединены с первыми информационными входами соответствующих сумматоров второй группы, выходы KOTOjMx подключены к информационным входам соответствующих реверсивных счетчиков, управляющие входы котоЕжлх соединены с управляющими входами сумматоров второй группы и подключены к девятому выходу блока управления, вторые входы счетчиков памяти первой группы подключены к информационным выходам первого коммутатора, управляющий выход которого соединен с первым входом блока управления., управляющие входы счетчиков памяти первой группы подключены к второму выходу блока управления, отличающее с я тем, что, с целью повышения точности моделирования, в устройство дополнительно введены второй коммутатор, блоки задания неизменных нагрузок, блоки задания коэффициентов чувствительности к нагрузке по параметру, блоки задания коэффициентов чувствительности к нагрузке по скорости, вторая и третья группы блоков умножения, третья, четвертая,и пятая группы сумматоров, вторая группа счетчиков памяти, выходы которих подключены к первым входам соответствующих сумматоров третьей группы, выходы которых соединены с первыми входами соответствующих сумматоров четвертой группы, вторые входы которых подключены к выходам соответствующих реверсивных счетчиков, управляющие входы сумматоров третьей группы соединены с десятым выходом блока управления, управляющие входы сумматоров четвертой группы соединены с одиннадцатым выходом блока управления , управляющие входы второй группы счетчиков памяти соединены с первым выходом блока управления, первые входы счетчиков памяти второй группы соединены первыми вxoдa вc блоков задания коэффициентов чувствительности к нагрузке по параметру блоков задания коэффициентов чувствительности к нагрузке по скорости подключены к информационным выходам первого коммутатора, вторые входы блоков задания коэффициентов чувствительности к нагрузке по скорости соединены с вторыми входами блоков задания коэффициентов чувствительности к нагрузке по параметру и под ключены к первым информационным выходам второго коммутатора, вторые и формационные выходы которого соединены с соответствующими входами бло ков памяти чисел, шестые входы блоков задания коэффициентов чувствительности к нагрузке по параметру соединены с третьими входами блоков задания коэффициентов чувствительности к нагрузке по скорости и подключены к выходу датчика нормально распределенных случайных чисел, выход блоков задания коэффициентов чувствительности к нагрузке по пара метру подключены к первым входам соответствующих блоков умножения второй группы, выходы блоков задани коэффициентов чувствительности к нагрузке по скорости соединены с пе выми входами соответствующих блоков умножения третьей группы, вторые входы блоков умножения второй и тре ей групп подключены к выходам соответствующих регистров, выходу второй группы блоков умножения соединень/ с вторыми входами соответствую щих сумматоров третьей группы, выходы счетчиков памяти первой группы подключены к первым информационным входам соответствующих сумматоров пятой группы, остальные информацион ные входы которвлх соединены с выходами соотве- ствующих блоков умножения третьей группы, выходы сумматоров пятой группы подключены к вторым информационнь 1 входам сумматоров второй группы, первые входа бло ков задания неизменных нагрузок под ключены к информационным выходам второго коммутатора, управляющий вы ход которого соединен с вторым вхо1ДОМ блока управления, вторые входы блоков задания неизменных нагрузок соединены с выходом датчика нормаль но распределенных случайных чиСел, третьи входы блоков задания неизменных нагрузок подключены к выходу датчика равномерно распределенных случайных чисел, выходы блоков зада ния неизменных нагрузок подключены к вторым входам соответствующих сум маторов первой группы, управлякяцие . входы блоков задания неизменных наг рузок соединены с двенадцатым выходом блока управления, управлякядий вход второго коммутатора подключен к тринадцатому выходу блока управления, управляющие входы пятой группы сумматоров соединены с четырнадцатым выходом блока управления, управляющие входы второй группы бло ков умножения подключены к пятнадцатому выходу блока управления, управлякяцие входы третьей группы блоков умножения соединены с шестнадцатым выходом блока управления, управляющие входы блоков задания коэффициентов чувствительности к нагрузке по параметру подключены к семнадцатому выходу блока управления, управляющие входы блоков задания коэффициентов чувствительности к нагрузке по скорости соединены с восемнадцатым выходом блока управления, первые входы счетчиков памяти второй группы соединены с информационными выходами первого колв утатора, вторые входы счетчиков памяти второй группы подключены к выходу элемента И. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит первый, второй и третий распределители импульсов, генератор.импульсов, реле времени, линию задержки, первый, второй и третий переключатели, элементы И, элементы ИЛИ, причем первый и второй выхЬдЫ первого распределителя импульсов через первый элемент ИЛИ подключены к первому входу первого элемента И, второй вход которого соединен с выходом генератора импульсов, выход первого элемента И подключен к первому входу второго элемента ИЛИ, второй и третий входы-которого соединены соответственно с выходами второго и третьего элементов И, информационный вход второго элемента И соединен с первыми входами четвертого элемента И и третьего элемента ИЛИ и подключен к третьему выходу первого распределителя,, четвертый и пятый выходы которого через четвертый элемент ИЛИ соединены с первыми, входами пятого и шестого элементов И и пятого элемента ИЛИ, выход которого подключен к первому входу седьмого элемента И, вторюй вход которого подключен к выходу генератора импульсов, выход седьмого элемента И соединен с первым входом второго распределителя импульсов и черюз линию задержки подключен к второму входу шестого элемента И, третий вход которого соединен с первым выт ходом второго распределителя импульсов и через шестой элемент ИЛИ подключен к первому входу восьмого элемента И, второй вход которого соединен с выходом генератора импульсов, шестой и седьмой выходы первого распределителя импульсов через седьмой элемент ИЛИ подключены к третьему входу восьмого элемента И, второму входу пятого элемента ИЛИ и к первому входу девятого элемента И, второй вход которого с помощью перемычки может быть подключен к любому, кроме первого, выходу второго распределителя импульсов, пятый выход первого распределителя импульсов и второй выход второго распределителя импульсов подключены соответственно к первому и второму входам десятого элемента И, выход которого соединен с первым входом восьмого элемента ИЛИ, второй вход которого соединен первЕлм входом одиннадцатого элемента И и подключен к выходу девятого элемента И, третий вход восьмого эл мента ИЛИ,соединен с вторым входом девятого элемента И, восьмой выход первого распределителя импульсов соединен с вторым входом третьего элемента ИЛИ, с информационным входом третьего элемента И и с первыми входами двенадцатогоJ тринадцатого и четырнадцатого элементов И, вторые входы которых подключены соответственно к первому и третьему выходам третьего распределителя импульсов, второй и третий выходы третьего распределителя импульсов соединены соответственно с первыми входами пятнадцатого и шестнадцатого элементов И, вторые входы которых объединены с первым входом четвертого элемента И, второй вход которого подключен к первому выходу третьего распр делителя импульсов, четвертый вьссод третьего распределителя импульсов и выход шестого элемента И подключены соответственно к первому и второму входам девятого элемента ИЛИ, выход четырнадцатого и шестнадцатого элементов И соединены соответственно с первыми входа1ми десятого и одиннадцатого элементов ИЛИ, вторые входы которых подключены соответственно к вЕлходам третьего и второго элементов И, пятый выход третьего распределителя импульсов соединен с первым входом двенадцатого элемента ИЛИ, выход которого соединен с первым входом третьего распределителя импульсов, второй вход которого подключен к выходу семнадцатого элемента }J, первый вход которого подключён к выходу третьего элемента ИЛИ, а йторой вход соединен с выходом генератора импульсов, девятый, десяты и Одиннадцатый выходы первого распре через тринадцатый элемент HJiH подключены к первому входу четырнадцатого элемента ИЛИ, второй и третий входы которого соединены соответственно с выходами пятого и одиннадцатого элементов И, второй вход которого подключен .к седьмому выходу первого распределителя импульсов, первый вход которого подключен к выходу четырнадцатого элемента ИЛИ, двенадцатый выход первого распределителя импульсов соединен с его вторым входом, одиннадцатый выход первого распределителя подключен к входу реле времени, первый вывод первого переключателя соединен с четвер- : тым входом четырнадцатого элемента ИЛИ, второй вывод первого переключателя, первый вывод второго переключателя и первый вывод третьего переключателя подключены к источнику питания, второй вывод второго переключателя подключен к третьему входу первого распределителя импульсов, второму входу двенадцатого элемента ИЛИ и к третьему входу восьмого элемента ИЛИ, четвертый вход которого соединен с вторым входом девятого элемента И, выход восьмого элемента ИЛИ подключен к второму входу второго распределителя импульсов, управляющие входы второго, третьего и пятого элементов И соединены с третьим входом двенадцатого элемента ИЛИ и являются вторым входом блока управления, первый вход которого соединен с пятым входом четырнадцатого элемента ИЛИ, первый и второй выходы первого распределителя импульсов, выход второго элемента ИЛИ, выход генератора импульсов, выход шестого элемента ИЛИ, второй вывод третьего ключа, девятый выход первого распределителя импульсов, выход восьмого элемента И, выход реле времени, выход одиннадцатого элемента ИЛИ, десятый выход первого распределителя импульсов, первый вуход второго распределителя .импульсов, выходы девятого и десятого элементов ИЛИ, выходы пятнадцатого, тринадцатого, четвертого и двенадцатого элементов И, второй вывод второго переключателя являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым, девятым, десятым, одиннадцатым, двенадцатым, тринадцатым, четырнадцатым, пятнадцатым, шестнадцатым, семнадцатым, восемнадцатым и девятнадцатым выходами блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 518775, кл. G Об F 15/20, 1976. 2.Авторское свидетельство СССР 5 634283, кл. G 06 F Д5/20, (прототип).

A. / 1 f П

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования канала передачи дискретной информации | 1983 |

|

SU1088006A1 |

| Система полунатурного моделирования динамических систем | 1986 |

|

SU1427377A1 |

| Устройство формирования оптимальных управляющих воздействий для обеспечения устойчивой работы сложных технических систем | 2017 |

|

RU2674281C1 |

| Устройство для прогнозирования надежности по результатам ускоренных испытаний | 1987 |

|

SU1508238A1 |

| Устройство для контроля вычислительных программ | 1985 |

|

SU1278856A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ УПРАВЛЯЮЩИХ ВОЗДЕЙСТВИЙ ДЛЯ ОБЕСПЕЧЕНИЯ УСТОЙЧИВОЙ РАБОТЫ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2011 |

|

RU2475828C1 |

| Устройство для моделирования процессов изменения параметров электронных схем | 1976 |

|

SU634283A1 |

| Устройство для определения законов распределения вероятностей | 1984 |

|

SU1188753A2 |

| Устройство для решения задач планирования экспериментов | 1984 |

|

SU1317450A1 |

Авторы

Даты

1982-04-30—Публикация

1980-02-12—Подача