(54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1981 |

|

SU966750A1 |

| Аналоговое запоминающее устройство | 1984 |

|

SU1156142A1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU691928A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU769633A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU849306A1 |

| Интегрирующее устройство | 1985 |

|

SU1251125A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU847376A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU928420A1 |

| АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1990 |

|

RU2018980C1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1084897A1 |

I

Изобретение -относится к области вычлолительной техники и предназначено для выборки и запоминания мгновенных значений напряжений и может быть использовано в аналогч -цифровых преобразователях.g

Известно аналоговое запоминающее уст- ройство ij, охваченное отрицательными обратными СВЯЗЯМИ. Высокой точностью и быстродействием отличаются аналоговые запоминающие устройства, охваченные двумя iо контурами обратной связи ИДз.Недостатком известных устройств являете ся ограниченное быстродействие, что обусловлено тем, что обеспечение большого коэф фициента передачи усилителей устройства 15 на низкой частоте, требуемое для получений малой статической погрешности - стройотва, сопровождается уменьшением полосы частот усилителя.

Из известных аналоговых запоминающих io устройств, охваченных отрицательными обратными связями, наиболее близким к предлагаемому изобретению по технической cymHoJти является устройство , содержащее усилитель, выход которого через первый ключ}

подключен к одному из его входов, накоп1|-тельный элемент, например конденсатор, одна из обкладок которого соединена с шиной нулевого поте щиала, ключи, нагрузочный элемент и щину входного сигнала.

Недостатком устройства является ограниченное быстродействие, которое проявляет ся в увеличении погрешности устройства (динамической погрешности) с ростом частоты. Повышение быстродействия устройства может быть достигнуто путем расширения полосы частот усилителя. Расширение полосы, однако, сорровождается уменьшением)стп (коэффициента передачи усилителя в р). кнутом состоянии), т. е. ростом погрешности устройства на низкой частоте. Найдем связь между KciTj усилителя и статической погрец ностью устройства. Пусти на шине входного сигнала присутствует напряжение U . Условие равновесия устройства в режиме выборки

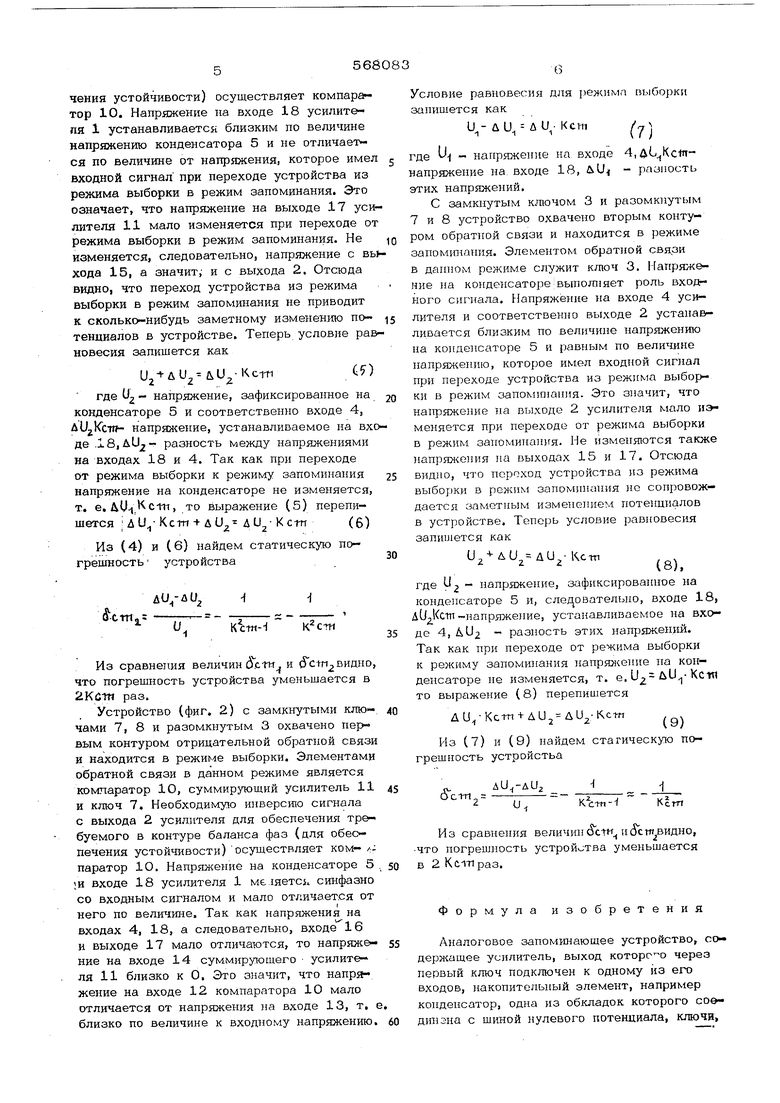

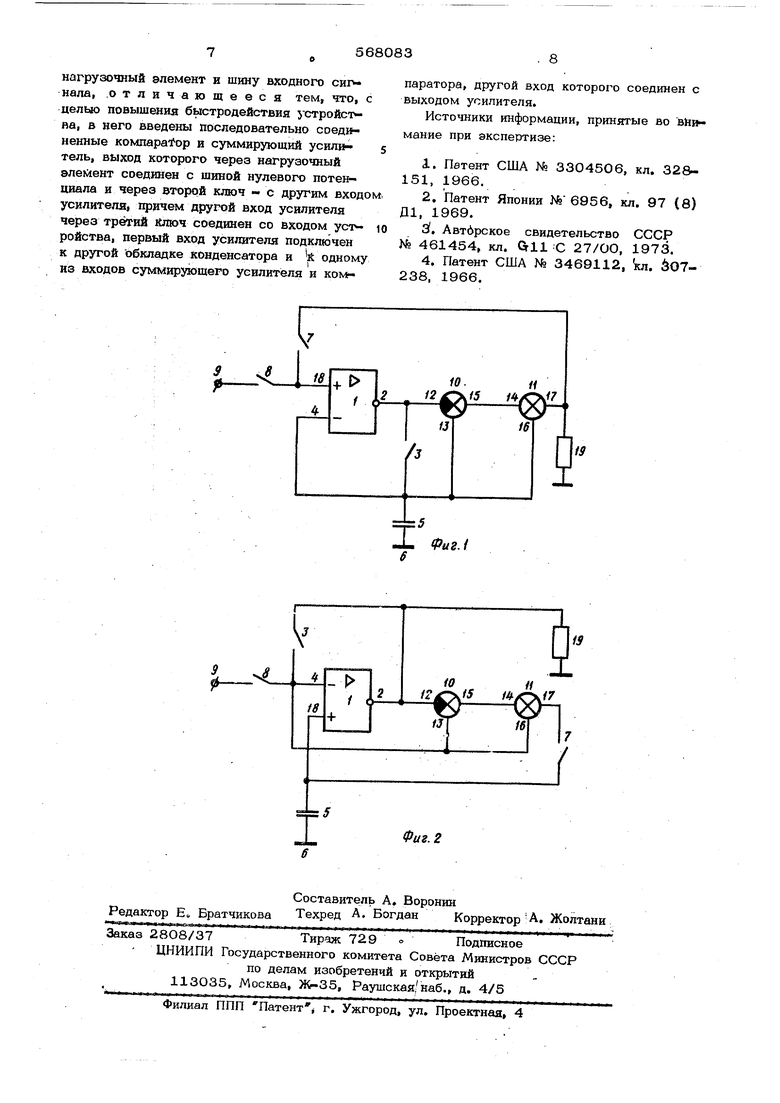

запишется как

ги,-ли -ди -Кстп (У)

где ДU разность между напряжением, присутствующим на одном из входЬв ( А и Kciti. ) и напряжением на другом входе (U,). Условие равновесия в режиме запоминания представится как (Jj,-Д 0 д U -Kern (3) разность между напряжением на одном из входов ( :(J) и на другом входе (). Так как при переходе от режима выборки к режиму запоминания напряжение на одном из входов не изменяется, т. е. Kctn,TO выражение (2) можно переписать ди Кет-ди ди Кс-тОТ. Из (1) и (З) найдем статическую погрешность запоминания устройства ., 2Кс-т-И 2 (Kc-m-v-l) Kctfl Из формулы видно, что применение в устройстве широкополосного усилителя с малым Kent не решает задачу повышения быстро-действия устройства, так как при этом резк возрастает статическая погрешность уст-. ройства. Целую изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в предлагаемое аналоговое запоминающее устройство введены последовательно соеди™ ненные компаратор и суммируюший усили тель, выход которого через нагрузочный элемент соединен с шиной нулевого потенциала и через второй ключ - с другим входом усилителя/ причем другой вход усилителя через третий ключ соединен со устройства, первый вход усилителя под ключен к другой обкладке конденсатора и к одному из входов суммирующего усилителя и компаратора, другой вход которого соедимен с выходом усилителя. На фигс 1 изображен первый вариант функциональной схемы предложенного уст. ройства; на фиг. 2 - второй вариант. Аналоговое запоминающее устройство (фиг« 1) содержит усилитель 1, выход 2 которого через первый ключ 3 подключен к одному из входов 4 усилителя 1, конденс тор 5, одна обкладка которого соединена с шиной нулевого потенциала 6, второй и третий ключи 7 и 8, шину входного сигнала 9, компаратор 10 и суммируюший усил тель 11, компаратор 1О подключен вычитаю шим входом 12 и суммируюшим входом 13 соогветственно к выходу 2 и ко входу 4 усилителя 1, а суммирующий усилитель 11 соединен одним из входов 14 с выходом 15 компаратора, другим входом 16 со вхоч дом усилителя 1, а выходом 17 через второй ключ 7 с другим входом 18 усилителя 1, причем выход 17 суммируюшего усилителя 11 подключен к нагрузочному элеме ту 19, вход 18 усилителя 1 через третий ключ 8 - к шине входного сигнала 9, а вход 4 усилителя - к другой обкладке конденсатора 5. Аналоговое запоминающее устройство (фиг. 2) содержит усилитель 1, выход 2 которого через первый ключ 3 подключен к одному из входов 4 усилителя, конденсатор. 5, одна обкладка которого соединена с шиной нулевого потенциала 6, второй и третий ключи 7 и 8, шину входного сигнала 9, компаратор 1О и суммирующий усилитель 11, компаратор 10 подключен вычитаю- шим входом 12 и суммирующим 13 соответственно к выходу 2 и ко входу 4 усилителя 1, а суммирующий усилитель 11 соединен одним из входов 14 с выходом 15 KON паратора 10, другим входом 16- со входом 4усилителя 1, а выходом 17 через второй ключ 7 с другим входом 18 усилителя 1, причем выход 2 усилителя 1 подключен к нагрузочному элементу 19, вход 18 усилителя 1 - к другой обкладке конденсатора 5, вход 4 усилителя 1 через третий ключ 8 подключен к шине входного сигнала 9, Устройство (фиг, 1) с замкнутыми клюнами 3 и 8 и разомкнутым 7 охвачено первым контуром отрицательной обратной cBseзи и находится в режиме выборки. Элементом обратной связи в данном режиме служит ключ 3. Напряжение на конденсаторе 5и выходе 2 усилителя меняется синфазно со входным сигналом и мало отличается от него по величине. Условие равновесия для режима выборки запишется как ди Ксш 1) где 1/ - напряжение, присутствующее на входе 18,uU jKciirh напряжение, присутствующее на входе 4, дО - разность между напряжением на входах 18 и 4. Так как с замкнутым ключом 3 напряжение на выходе 2 и входе 4 равны, равны и напр51жения на входах 12 и 13 компаратора 10, Поэтому напрю;сение на выходе 15 компаратора 10 равно О о Это напряжение, а также напряжение с конденсатора 5 поступают на суммирую ший усилитель 11, Сумма напряжений, присутствующая на выходе 17 суммирующего усилителя 11, не отличается, естественно, по величине от напряжения, присутствующего на входе 4 и .входе 2 усилителя 1. С замкнутым ключом 7 и разомкнутыми 3, 8 устройство охвачено вторым контуром отрицательной обратной связи и находится в режиме запоминания, Нап ряжение на конденсаторе выполняет роль входного сигнала. Элементами обратной связи в данном реж ме являются компаратор 1.0, усилитель 11 и ключ 7, Необходимую инверсию с выхода 2 усилителя 1 сигнала для обеспечения требуэмого в контуре баланса фаз (для обеспечения устойчивости) осуществляет компаратор 10. Напряжение на входе 18 усилит&пя 1 устанавливаетсй близким по величине напряжению конденсатора 5 и не отличается по величине от напряжения, которое име входной сигнал при переходе устройства из режима выборки в режим запоминания. Это означает, что напряжение на выходе 17 уси лителя 11 мало изменяется при переходе о режима выборки в режим запоминания. Не изменяется, следовательно, напряжение с в хода 15, а значит, и с выхода 2. Отсюда видно, что переход устройства из режима выборки в режим запоминания не приводит к сколько-нибудь заметному изменению потенциалов в устройстве. Теперь условие ра новесия запишется как и напряжение, зафиксированное на конденсаторе 5 и соответственно входе 4, AUjKc7№- напряжение, устанавливаемое на вх де .18, разность между напряжениями на входах 18 и 4. Так как при переходе от режима выборки к режиму запоминания напряжение на конденсаторе не изменяется, т. е, ди l c-iii, то выражение (5) перепишется ; Д Ц-КсттИ-д U д U.-К cm(6) Из (4) и (6) найдем статическую погрешность устройства tTtljL Из сравнения величин dent. и dcin 2 видно, что погрешность устройства уменьшается в 2КС-т раз. Устройство (фиг, 2) с замкнутыми ключами 7, 8 и разомкнутым 3 охвачено вым контуром отрицательной обратной связи и находится в режиме выборки. Элементами обратной связи в данном режиме является компаратор 10, суммирующий усилитель 11 и ключ 7. Необходимую инверсию сигнала с выхода 2 усилителя для обеспечения требуемого в контуре баланса фаз (для обеспечения устойчивости) осуществляет ком- лпаратор 10. Напряжение на конденсаторе 5 ;и входе 18 усилителя 1 ме raeTCi синфазно со входным сигналом и мало отличается от него по величине. Так как напряжения на входах 4, 18, а следовательно, входе 16 и выходе 17 мало отличаются, то напрянс&ние на входе 14 суммирующего усилителя 11 близко к О. Это значит, что nanpstжение на входе 12 компаратора 10 мало отличается от напряжения входе 13, т. е близко по величине к входному напряжению. Условие равновесия для 1,ежима выборки запишется как Ц- ли, ДЦ- Ксм1 где Ц - напряжение на входе 4,дЦКслнапряжение на, входе 18, U,U.| - разность этих напряжений. С замкнутым ключом 3 и разомкнутым 7 и 8 устройство охвачено вторым контуром обратной связи и находится в режиме запомгоиания. Элементом обратной связи в данном режиме служит ключ 3. Напряжение на конденсаторе выполняет роль входного сигнала. Напряжение па входе 4 усилителя и соответственно выходе 2 устана&ливается близким по величине напряжению на конденсаторе 5 и равным по величине напряжению, которое имел входной сигнал при переходе устройства из режима выборзки в режим запоминапня- Это значит, что напряжение па выходе 2 усилителя мало изменяется при переходе от режима выборки в режим запоминания. Не измептотся также папря се)ия на выходах 15 и 17. Отсюда видно, что переход устройства из режима выборки в реисим запомипапия не сопровождается заметным изменением потеппиалов в устройстве. Теперь условие равновесия запииются как и,-ли -ди -Ксп1 g где У папряжепие, зафиксироваппое на конденсаторе 5 и, слег овательпо, входе 18, -напряжение, устанавливаемое на входе 4, AU2 - разность этих нащзяжепий. Так как при переходе от режима выборки к режиму запомипания папря кепие па конденсаторе не изменяется, т. е. U - U -Kcrti то выражение (8) перепишется ди -Ксгп1-ди2 Ди Из (7) и (9) найдем статическую погрешность устройства (Scrn Из сравнения величин cttt и(Scrnвидно, что погрешность устройства уменьщается в 2 К tin раз. Формула изобретения Аналоговое запом1шающее устройство, содержащее усилитель, выход которого через первый ключ подключен к одному из его входов, накопительный элемент, например копдепсатор, одна из обкладок которого со&ипэна с шиной нулевого потенциала, ключи,

нагрузочный элемент и шину входного си1 нала, .отличающееся тем, что, с целью повышения быстродействия устройств ва, в него введены последовательно соединенные компаратор и суммирующий усил тель, выход которого через нагрузочный элемент соединен с шиной нулевого потенциала и через второй ключ - с другим входо усилителя, причем другой вход усилителя через третий йлюч соединен со входом уст ройства, первый вход усилителя подклкзчен к другой обкладке конденсатора и s одному из входов суммирующего усилителя и ко-ме -

паратора, другой вход которого соединен с выходом усилителя.

Источники информации, принятые во внимание при экспертизе:

3f. Автбрское свидетельство СССР № 461454, кл. ОН С 27/00, 1973.

Авторы

Даты

1977-08-05—Публикация

1975-07-29—Подача