Изобретение относится к вычислительной и информационногизмеритель- нон технике, в частности, предназначено для иснользования в интегрирующих преобразователях срорма-код.

Цель изобретения - повьшение точности интегрирования.

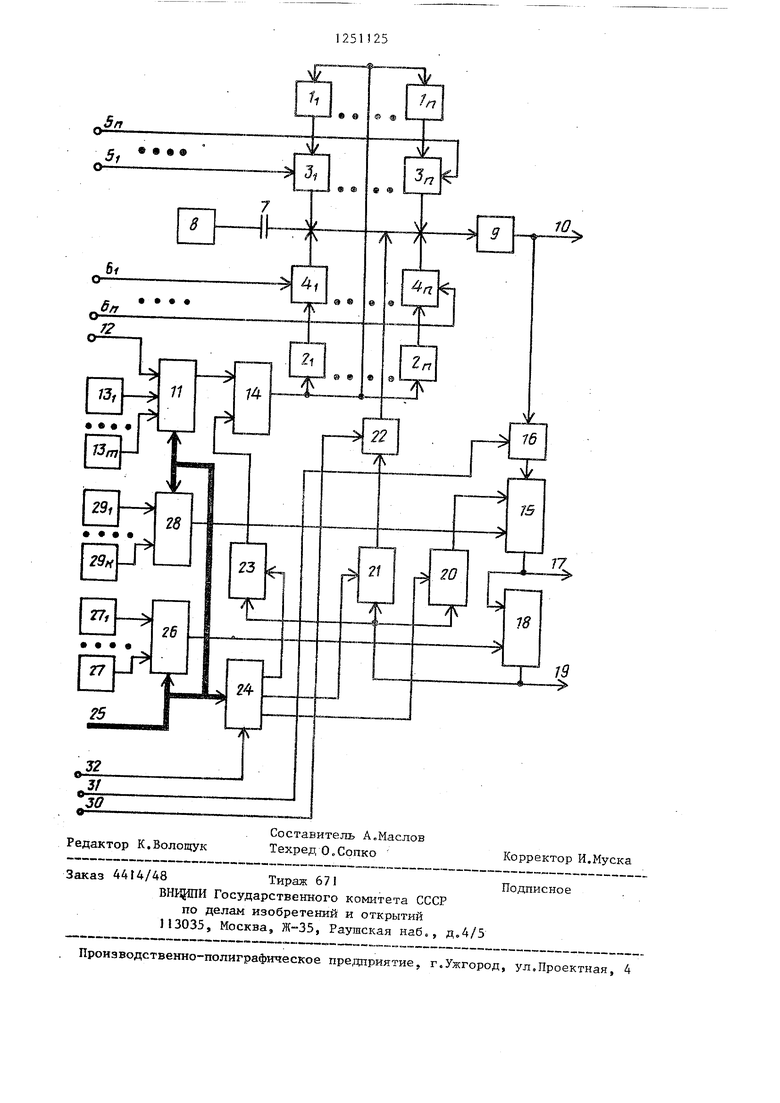

На чертеже приведена схема интегрирующего устройства.

Интегрирующее устройство содержит генераторы тока положительной 1 - 1„ и отрицательной

2, - 2 полярности, переключатели 3. - 3f. и 4, А.тока, управляющие входы которых являются входами разрешения интегрирования устройства 5, - 5 и

6 , - 6

р интегрирующий конденсатор

7, одна обкладка которого соединена с источником 8 постоянного напряжения, буферный усилитель 9, выход которого является аналоговым информационным выходом устройства 10, а вход соединен с другой обкладкой интегрирующего конденсатора 7 и через соответствующие переключатели 3 - 3, и 4, - 4„ тока с выходами генераторов тока положительной

Ь

и отрицательной 2 , - 2 f, полярности, первый коммутатор 11, информационные входы которого соединены соответственно с аналоговым информационным входом устройства 12 и выходами группы источников 13, - 13 эталонных сигналов, суммирующий усилитель 14, первый вход которого соединен с выходом первого коммутатора 11, а выход - с управляющими входами генераторов 1( - 1 и 2( 2 h тока, усилитель с регулируемым коэффициентом передачи 15, аналоговый блок 16 памяти, вход которого соединен с аналоговым информационным выходом устройства 10, а выход - с входом усилителя с регулируемым коэффициентом передачи 15, выход которого является аналоговым информационным выходом считывания устройства 17, элемент 18 сравнения, первый вход которого соединен с выходом устройства 17, а выход является дискретньш информационным выходом устройства 19, первый интегратор 20 обратной связи, выход которого соединен с первым управляющим входом плавной регулировки коэффициента усиления усилителя с регулируемым коэффициентом передачи 15, второй интегратор 21 обратной связи, ключ 22, через который выход второго интеграто-.

10

.

15

20

25

30

35

40

45

50

55

252

ра 21 обратной связи соединен с вхо- дом буферного усилителя 9, третий интегратор 23 обратной связи, выход которого соединен с вторым входом суммирующего усилителя 14, входы всех интеграторов 20, 21 и 23 обратной связи соединены с дискретным информационным выходом устройства 19, четвертый коммутатор 24, управляющие входы которого являются входами задания работы устройства 25, а соответствующие выходы соединены с входами разрешения интегрирования интеграторов 20,21 и 23 обратных связей, второй коммутатор 26, выход которого соединен с вторым входом элемента 18 ,сравнения, а входы - с источниками 27, - 27 опорных сигналов, третий коммутатор 28, выход которого соединен управляющим входом дискретной регулировки коэффициента усиления усилителя с регулируемьм коэффициентом передачи 15, а входы - с выходами группы источников 29 - 29 к сигналов программирования коэффициента усиления, управляющие входы всех коммутаторов 11,24, 26 и 28 соединены с входами задания режима работы устройства 25, управляющий вход ключа 22, адресный вход аналогового блока 16 памяти, информационный вход четвертого коммутатора 24 являются соответственно входом начальной установки устройства 30, входом выборки и запоминания результата интегрирования 31 и стробирующим входом устройства 32.

Устройство работает следуюищм образом.

При подаче на входы 25 задания режима работы устройства соответствующей комбинации управляющих сигналов реализуется один из режимов работы устройства. Интегрирование входного сигнала производится при подключении через первый коммутатор I1 к первому входу суммирующего усилителя 14 информационного входа устройства 12, через -третий коммутатор 28 одного из источников 29, - 29 ц. сигнала регулирования выбранного коэффициента усиления, через второй коммутатор 26 одного из источников 27 - 27 опорного сигнала, соответствующего нулевому значению входного сигнала. При из-, менВНИИ сигнала на выходе суммирую- щего усилителя 14 прямо пропорционально изменяется разность токов ге

312

нераторов тока положительной 1, - 1, и отрицательной 2, 2 полярности. При снятии сигнала на входе 30 начальной установки устройства и подаче на управляющие входы 5, - 5, и 6( - 6„ переключателей 3, - 3 и 4| у тока, сигналов разрешения интегрирования разность токов генераторов тока положительной и отрицательной полярности заряжает интегрирующий конденсатор 7, разность напряжений на котором до и после интегрирования соответствует интегральному значению сигнала на интервале интегрирования. Е момент окончания сигнала разрешения интегрирования ток генераторов тока посредством переключа телей тока от интегрирующего конденсатора переключается на общую шину устройства, при этом заряд на конден саторе 7 запоминается. Так как выход устройства 10 используется для последовательного соединения интеграторов при преобразовании форма - код методом последовательного интег- рирования, то буферный усилитель 9 должен не только обладать высоким входным сопротивлением, но и обеспечивать неискаженную передачу формы изменения напряжения на интегрирующем

конденсаторе 7. I

По окончании сигнала разрешения

интегрирования Подается сигнал выборки на вход выборки и запоминания результата интегрирования 31. Напряже- ние на выходе буферного усилителя 9 запоминается аналоговым блоком 16 памяти по окончании сигнала выборки. После этого может быть подан сигнал начальной установки устройства по входу 30, по которому через ключ 22 переходивший в открытое состояние, интегрирующий конденсатор 7 разряжается до уровня, соответствующего напряжению на выходе интегратора 21 обратной связи. По окончании сигнала начальной установки устройства процесс интегрирования может быть повторен. На выходе устройства 17 напряжение соответствует интегральному значению сигнала с определённым масштабирующим коэффициентом, что позволяет- нормировать выходной сигнал.

В элементе 18 сравнения производится дискретизация разности выходно- го и опорного сигналов. Если в качестве элемента 18 сравнения используется не отдельный компаратор, а анало

54

го-цифровой преобразователь, то с выхода 19 устройства может сниматься код, соответствующий интегральному значению сигнала.

При интегрировании сигнала реальным устройством интегрирующий конденсатор 7 также заряжается начальной разностью токов генераторов I - 11, и 2, 2 тока и входным током буферного усилителя 9,

В момент действия сигнала выборки интегрируюпшй конденсатор 7 также продолжает заряжаться входным током буферного усилителя 9. При этом нестабильность коэффициента преобразования определяется в первую очередь нестабильностью генераторов тока 1 -1, и 2 - 2(, тока емкостью интегрирующего конденсатора 7. Для компенсации погрешностей преобразователя используются интеграторы 20,21 и 23 обратных связей, осуществляющие отрицательную обратную связь изменением соответственно коэффициента усиления с регулируемым коэффициентом пе- редачи 15, уровня начального значения напряжения интегрирующего кон- денсатора 7, смещения уровня входного сигнала.

При выборе режима установки начального значения на интегрирующем конденсаторе 7 через второй коммутатор 26 к второму входу блока 18 сравнения подключается опорньш сигнал, соответствующий нулевому значению входного сигнала.

При отсутствии сигнала разрешения интегрирования на соответствующих входах 5 ,-6„ снимается сигнал начальной установки на входе 30 устройства и подается сигнал выборки по входу 31, по окончании которого в аналоговом блоке 16 памяти запоминается значение напряжения, соответствующее начальному уровню напряжения на интегрирующем конденсаторе 7 с учетом входного тока и смещения .буферного усилителя 9, которое далее сравнивается в элементе 18 сравнения с опорным сигналом, соответствующим нулевому значению входного сигнала. При этом результат сравнения учитывает также смещение аналогового блока 16 памяти и усилителя с регулируемь М коэффициентом передачи 15.

По окончании сигнала выборки с учетом задержки, необходимой для установлеиия результата сравнения на выходе элемента 18 сравненияj на стробирующий вход устройства 32 подается сигнал, который через коммутатор 24 поступает на вход разрешения интегрирования только второго интегратора 21 обратной связи в соответствии с комбинацией управляющих сигналов на входе 25 задания режима работы устройства. За определенное количество циклов данного режима на выходе второго интегратора 21. обратной связи устанавливается напряжение, обеспечивающее разряд интегрирующего конденсатора 7 до уровня начального значение при котором на выходе элемента 18 сравнения устанавливается нулевой результат сравнения.

При выборе режима кo meнcaции начальной разности токов генераторов 1, - 11 и 2 ( - 2 ц тока и тока буферного усилителя 2 через первый коммутатор 1I подключается источник эталонного сигнала, через второй коммутатор 26 источник опорного сигнала, соответствующие нулевому значению нходного сигнала, снимается сигнал начальной установки устройст- па по входу 30, подается сигнал разрешения .интегрирования на входы 5( - .5 и 6., - 6„9 по окончании которого подаётся сигнал выборки на вход 31 устройства. В момент окончания сигнала выборки в аналоговом блоке 16 памяти запоминается значение напркже1 ия на интегрирующем конденсаторе 7, отличающееся от начального значения на величину иитегрального значения разности токов генераторов 5 - 1 и 2 , 2 тока и входного тока буферно.го усилителя 9, которое сравнивается в элементе 18 сравнения с опорньм сигналом, соответствующим нулевому значению входного сигнала. По окончании сигнала выборки также с задержкой подается на вход 32 устройства сиг- нал, который Б данном случае поступает через дешифратор на вход разрешения интегрирования только третьего интегратора 23 обратной связи.

За определенное количество цик лов данного режим на выходе третьего интегратора 23 обратной связи устанавливается напряжение5 компенсирующее разность токов генераторов

Ц - 1 и 2| - 2jj тока и входного тока буферного усилителя 9.

При выборе режимй коррекции обще- го коэффициента преобразования через первьш коммутатор 1I подключается источник 13 эталонного сигнала, отличного от нулевого значения,через третий коммутатор 28 - источник сигнала регулирования выбранного коэффициента усиления, через второй коммутатор 26 - источник 27 опорного сигнала,, соответствующего эталонному сигналу с заданным коэффициентом усиления. Далее производится также последовательность действий, как при интегрировании нулевого значения эталонного сигнала, но при этом сигнал, подаваемый на вход 32 устройства,

проходит на вход разрешения интегрирования уже только первого интегратора 20 обратной связи. Сигнал на выходе элемента сравнения учитывает отличие общего коэффициента преобразования от ожидаемого. За определенное количество циклов на выходе первого интегратора 20 обратной связи устанавливается сигнал, изменяющий коэффициент усиления усилителя с регулируемым коэффициентом усиления 15 и компенсируюпщй нестабильность общего коэффициента преобразования.

Описанные режимы работы устройства в зависимости от применяемых эле

ментов и требуемой точности могут чередоваться с режимом интегрирования входного сигнала с различной частотой повторения.

Формула изобретения

Интегрирующее устройство, содержащее две группы генераторов тока соответственно положительной и отрицательной полярностей, выходы которых через соответствующие переключатели тока подключены к одной из обкладок интегрирующего конденсатора и к входу буферного усилителя, выход которого является аналоговым информационным выходом устройства, и источник постоянного напряжения, выход которого подсоединен к другой обкладке интегрирующего конденсатора, управляющие входы переключателей тока являются соответствующими, входами разрешения интегрирования устройства, отличающееся тем.

что, с целью повьш1ения точности интегрирования, оно содержит первый, второй и третий интеграторы обратной связи, первый, второй, третий и четвертый коммутаторы, элемент срав нения, группу источников эталонных сигналов, группу источников сигналов программирования коэффициента усиления, группу источников опорных сигналов, усилитель с регулируемым коэффициентом передачи, аналоговый блок памяти, ключ и суммирующий усилитель, выход которого соединен с управляющими входами всех генераторов тока, а первый и второй входы подключены соответственно к выходам первого коммутатора и третьего интегратора обратной связи, один из информационных входов первого коммутатора является аналоговым информа- ционным входом устройства, а другие информационные входы первого коммутатора подсоединены к выходам соответствующих источников эталонных сигналов группы, выход второго ком мутатора соединен с первым входом элемента сравнения, а его информационные входы подсоединены к выхода соответствующих источников опорных сигналов группы, управляющие входы плавной и дискретной регулировки коэффициента усиления усилителя с регулируемым коэффициентом передачи подключены соответственно к выходу первого интегратора обратной связи

и к выходу третьего коммутатора, информационные входы которого подсоединены к выходам соответствующих источников сигналов програмирования коэффициента усиления группы, информа- ционньй вход четвертого коммутатора является стробирующим входом устройства, а его три выхода подключены к входам разрешения интегрирования соответственно первого, второго и третьего интеграторов обратной связи, выход второго интегратора подключен через ключ, подсоединенный управляющим входом к входу начальной установки устройства, к входу буферного усилителя, выход которого соединен с информационным входом аналогового блока памяти, адресньш вход аналогового блока памяти является управляющим входом выборки и запоминания результата интегрирования устройства, а его выход подключен к информационному входу усилителя с регулируемым коэффициентом передачи, выход которого является ансшоговым информационным выходом считывания устройства и подключен к второму входу элемента сравнения, выход элемента сравнения соединен с информационными входами первого, второго и третьего интеграторов обратной связи и является дискретным информационным выходом устройства, управляющие входы всех коммутаторов объединены и являются цифровым входом задания режима работы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования напряжения переменного тока в код | 1990 |

|

SU1795543A1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2006886C1 |

| Компаратор формы сигналов | 1985 |

|

SU1257604A1 |

| Аналоговый интегратор | 1987 |

|

SU1425724A1 |

| СПОСОБ ОЦИФРОВКИ АНАЛОГОВОЙ ВЕЛИЧИНЫ, ОЦИФРОВЫВАЮЩЕЕ УСТРОЙСТВО, ОСУЩЕСТВЛЯЮЩЕЕ УКАЗАННЫЙ СПОСОБ, И ДЕТЕКТОР ЭЛЕКТРОМАГНИТНОГО ИЗЛУЧЕНИЯ, СОДЕРЖАЩИЙ ТАКОЕ УСТРОЙСТВО | 2008 |

|

RU2430465C2 |

| Масштабный преобразователь напряжения и его варианты | 1980 |

|

SU922780A1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО СБОРА ДАННЫХ С АКСЕЛЕРОМЕТРОВ | 2016 |

|

RU2644620C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ СБОРА ДАННЫХ С АКСЕЛЕРОМЕТРОВ | 2016 |

|

RU2658569C2 |

| Интегратор | 1988 |

|

SU1728871A1 |

Изобретение относится к вычислительной и к информационно-измерительной технике. Цель изобретения - повышение точности интегрирования. Интегрирование входных и эталонных сигналов в отличие от нрототипа осуществляется при управлении генераторают тока через первый коммутатор и первый вход суммирующего усилителя, на второй вход которого подается сигнал с третьего интегратора обратной связи, учитьшаищий погрешность интегрирования от разности токов генераторов тока и входного тока буферного усилителя. Начальное значение напряжения на интегрирующем конденсаторе устанавливается через ключ соответствующим выходному сигналу второго интегратора обратной связи. Погрешность от напрялсения смещения и входного тока буферного усилителя учитывается в момент выборки результата интегрирования аналоговым блоком памяти, сигнал на выходе которого усиливается при подаче на вход плавной регулировки коэффициента усиления усилителя с регулируемым коэффициентом усиления выходного сигнала первого интегратора обратной связи с учетом погрешности общего коэффициента преобразования. Выбор наиболее выгодного диапазона интегрирования осуществляется подключением соответствующих генераторов тока, а выбор масштаба выходного сигнала также и регулированием коэффициента усиления. Изобретение может быть использовано в радиоэлектронных системах обработки и анализа сигналов, в частности в интегрирующих преобразователях форма - код. 1 Ш1. (Л ю сд го СП

| Устройство для измерения параметров одиночных и редко повторяющихся импульсов малой длительности | 1977 |

|

SU693269A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Бахтиаров Г.Д, и др, Аналого-циф- ровые преобразователи, М.: Советское радио, 1980,, с | |||

| Раздвижной паровозный золотник с подвижными по его скалке поршнями между упорными шайбами | 1922 |

|

SU148A1 |

Авторы

Даты

1986-08-15—Публикация

1985-01-24—Подача