(54) геНЕРАТОР ИМПУЛЬСОВ с ЛИНЕЙНОИЗМЕНЯЮЩЕЙСЯ ЧАСТОТОЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой кодирующий преобразователь частоты следования импульсов | 1980 |

|

SU919080A1 |

| Генератор импульсов с линейно-изменяющейся частотой | 1982 |

|

SU1094139A1 |

| Генератор импульсов с линейно изменяющейся частотой | 1985 |

|

SU1256158A2 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1978 |

|

SU742967A1 |

| Устройство для измерения частоты повторения импульсов | 1976 |

|

SU573766A1 |

| Генератор случайного процесса | 1982 |

|

SU1037249A1 |

| Многоканальный преобразователь частоты в код | 1984 |

|

SU1243095A1 |

| Устройство для вычисления обратных функций | 1980 |

|

SU942007A1 |

| Генератор случайного процесса | 1983 |

|

SU1113800A1 |

| Измерительный узкополосный усилитель | 1982 |

|

SU1072250A1 |

Изобретвйие относится к импульсной технике.

Известен генератор импульс ж с линей- во изменяющейся,частотой, содержащий восьмиразрядный счетчик импульс1Ж, имеюпшй аналоговый выход, схему генерация пилообразного напряжения, выпопнанную на четырех транзисторах, двух усилителях и двух логических элементах И-НЕ, и генератс опорной частоты Ш . Однако такой генератх сложен по конструкции.

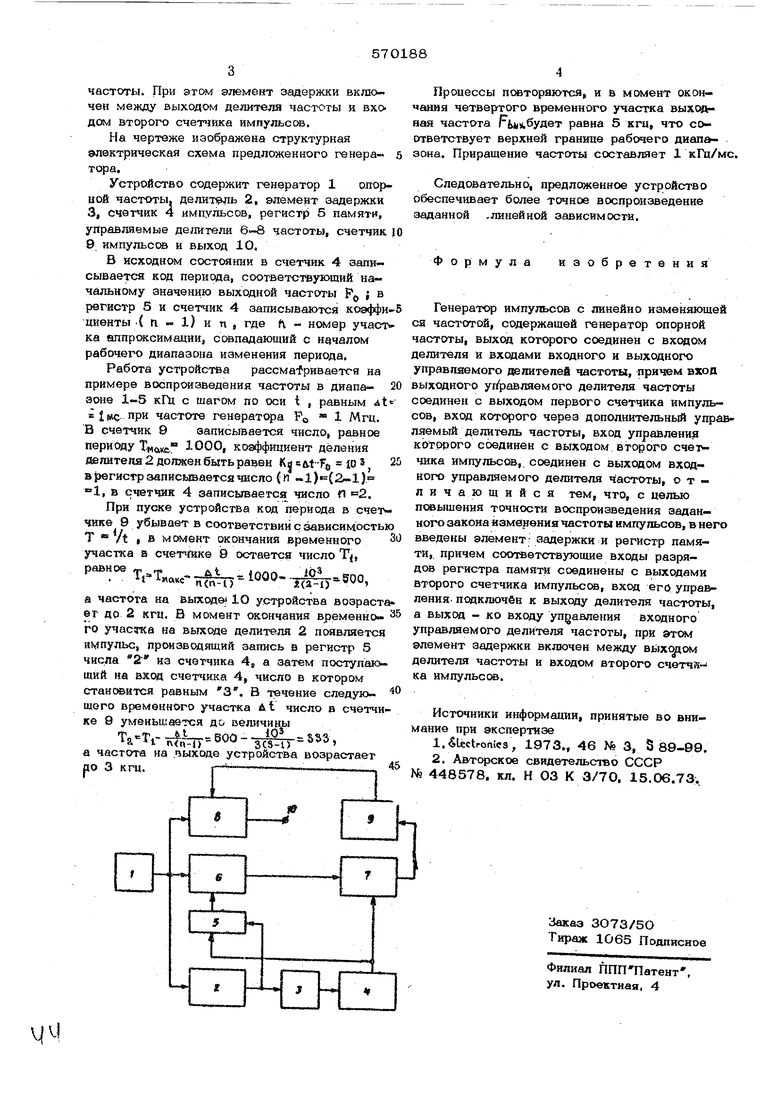

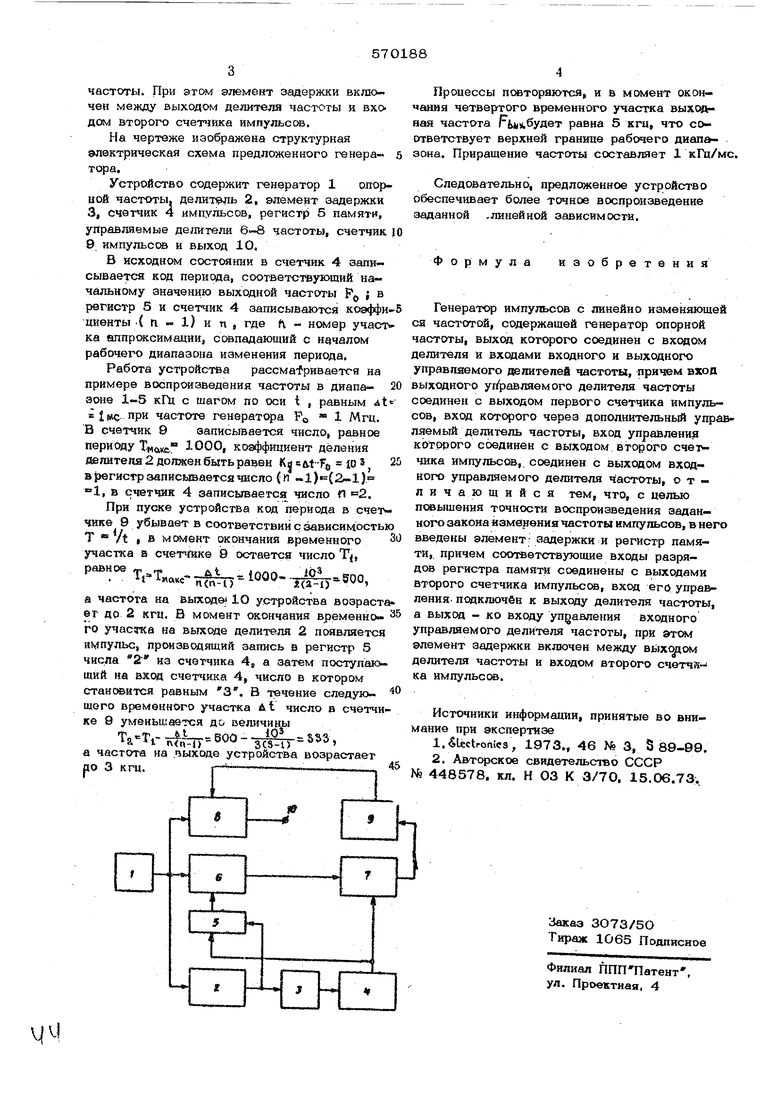

Наиболее близким по технической: сущности к предложенному устройству является генератор содержащий генератор опорясй частоты, выход которого соединен со входом делителя частоты и входами входноьго и выходного управляемых делителей частоты, причем вход выходного управляемого делителя частоты соединен с выходом первого счетчика импульсов, вход которого через дополнительный управляемый делитель частоты, вход управления которого соединен с выходом второго счетчика импульсов, соединён с выходом входного управляемого делтеля частоты 2. Однако такой генератор

зйе обеспечивает необходимой точности воспр изведения зад1анно1чэ закона изменения частоты.

Цель изобретения - повышение точности воспроизведения заданного закона изменения ;Частоты импульсов.

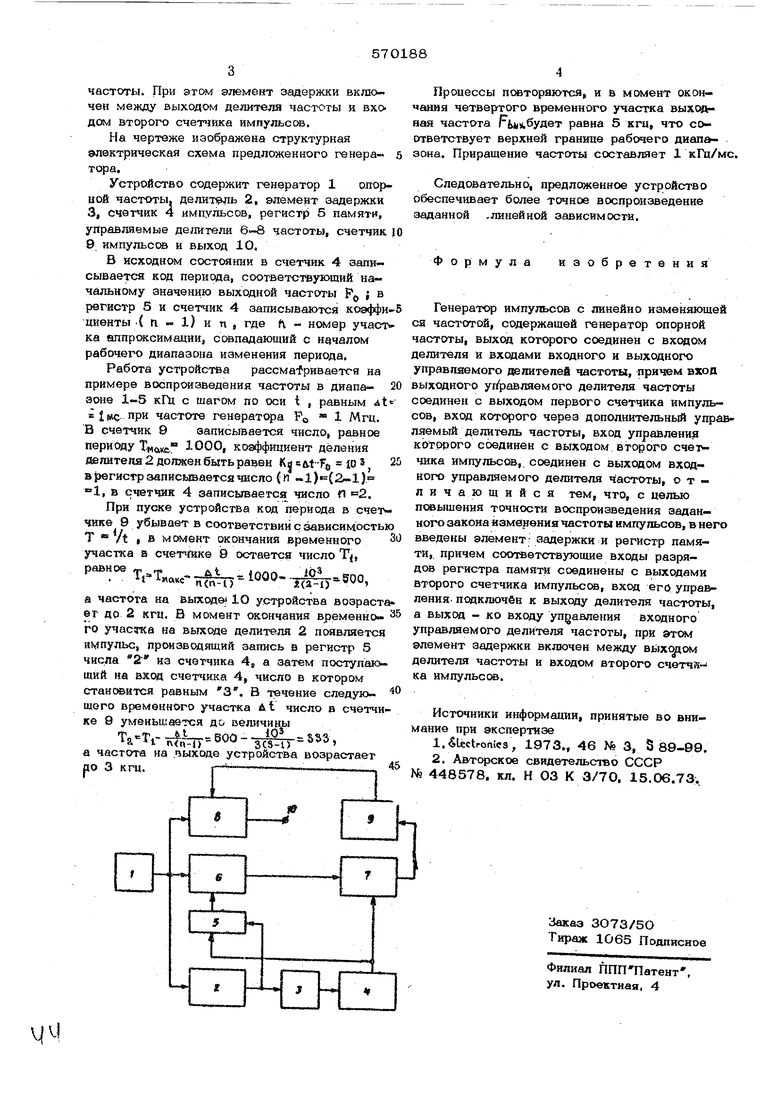

Это достигается тем, что в генератор импульсов, содержащий генератор tmypeou частоты, выход которого соединен со вхс дом делителя частоты и входами входного и выходного управляемых делите;юй дастоты причем вход выходного управляемого делите пя частоты соединен с .выходом первого счетчика импульсов, вход которого через дополнительный управляемый делитель час10 ты, вход-управления которого соединен с выходом второго счетчика импульсов, соединен с выходом входного управляемого де:Ли-теля частоты, введены элемент задержки И;регистр памяти, причем соответствующие входы разрядов регистра памяти соединены с выходами второго счетчика импульсов, вход его управления подключен к выходу делителя частоты, а выход - ко входу управления входного управ.шемого делителя

Авторы

Даты

1977-08-25—Публикация

1976-04-12—Подача