Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для однократного дифференцирования по времени частотно-импульсных сигналов.

Известно устройство для дифференцирования частотно-импульсных сигналов, содержащее блок управления, счетчик, делитель частот 1, генератор опорной частоты, три регистра памяти, три управляемыхделителя частоты, переключательный блок и блок вычитания импульсов 1.

Известно также частотно-импульсное дифференцирующее устройство, содержащее блок управления, генератор опорной частоты, счетчики, регистры памяти, распределитель импульсов, блок вычитания, группы элементов И и ИЛИ и блоки сложения-вычитания 2.

Недостатком известных устройств является понийсенная динамическая точность дифференцирования.

Наиболее близкое к предлагаемому устройство для дифференцирования частотно-импульсных сигналов содержит три регистра памяти, информационный вход первого из соединен с

выходом счетчика, подключенного счетным входом через делитель частоты к выходу генератора опорной частоты и к счетным входам первого и второго управляемых делителей частоты, а выход первого регистра памяти соединен с управляющим входом первого .управляемого делителя частоты и информационным входом второго регистра

10 памяти, выход которого подключен к управляющему входу второго управляемого делителя частоты, соединенного выходом с первым входом первого блока вычитания импульсов, выход кото15рого подключен к счетному входу третьего управляемого делителя частоты, а второй вход соединен с выходом первого управляемого делите;ля частоты, причем входы управления

20 записью регистров памяти и обнуляющие входы счетчика и делителя частоты подключены к соответствующим выходам блока управления, соединенного входом с входной шиной устрой25ства, а выход счетчика подключен к информационному входу третьего регистра памяти, соединенного выходе с управляющим входом третьего управляемого делителя частоты, выход

которого подкгаочен к выходной ине устройства 3.

Как и указанные выще известные стройства, данное устройство не вносит динамических ошибок дифференцирования только при формировании производных для линейно-изменяющихся во времени входных сигналов. При дифференцировании нелинейно-изменяющихся во времени входных сигналов выходной сигнал устройства имеет динамическую ошибку преобразования, увеличивающуюся от нуля до максимума внутри каждого очередного следова- НИИ входных импульсов и пропорционаЛьную второй производной входного сигнала.

Цель изобретения - уменьшение динамической ошибки.

Для достижения указанной цели в устройство для дифференцирования часTOtHO-импульсных сигналов, содержащее три регистра памяти, информационный вход первого из которых соединен с выходом счетчика, подключенного счетным входом.через делитель частоты к выходу генератора опорной частоты и к счетным входам первого и второго управляемых делителей частоты, а выход первого регистра памяти соединен с управляющим входом первого управляемого делителя частоты и с информационным входом второго регистра памяти, выход которого подключен к управляющему входу второго управляемого делителя частоты, соединенного вы|ходом с первым входом первого блока вычитания импульсов, первый выход которого подключен к счетному входу третьего управляемого делителя частоты, а второй вход соединен с выходом первого управляемого дели геля частоты, причем входы управления записью регистров памяти и. обнулящие входы счетчика и делителя частоты подключены к соответствующим выходам блока управления, соединенного входом с входной шиной устройства, дополнительно введены четверть|й, пятый и шестой управляемые делители, частоты, .второй и третий блоки вычитания импульсов, двоичный умножитель, триггер и блок суммирования частот, соединенный выходом с выходной шиной устройства ,и подключенный входами соответственно к выходу двоичного умножителя, второму выходу первого блока вычитания импульсов, входу третьего управляемого делителя частоты и выходу триггера, соединенного счетным вхо-дом с входом четвертого управляемого делителя частоты и выходом второго блока вычитания импульсов, входы которого подключены к выходам третьего и пятого управляё1«ых делителей частоты, причем счетный вход пятого управляемого делителя частоты, соединенного управляющим входом с выходом

Iвторого регистра памяти и информационным входом третьего регистра памяти, подключен к выходу третьего .блка вычитания импульсов, входы которого соединены с выходами второго и шестого управляемых делителей частоты, а счетный вход шестого управляемого делителя частоты, подключенного управляющим входом к выходу третьего регистра памяти, соединен с выходом генератора опорной частоты и первым информационным входом двоичного умножителя, подключенного входом обнуления к соответствующему выходу блока управления и соединенного вторым информационным входом с выходом четвертого управляемого делителя частоты, управляющий вход которого подключен к выходу первого регистра памяти к управляющему входу третьего управляемого делителя частоты.

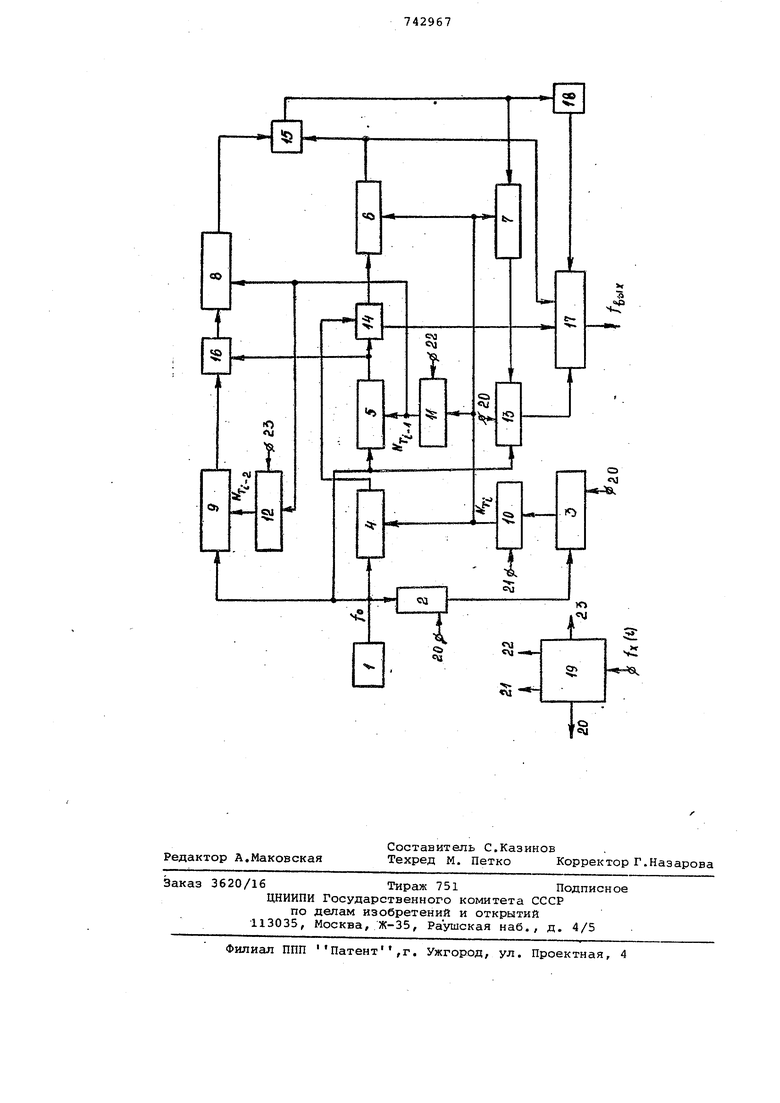

На чертеже изображена блок-схема устройства для дифференцирования частотно-импульсных сигналов.

Устройство содержит генератор 1 опорной частоты, делитель 2 частоты, счетчик 3, первый, второй, третий, четвертый, пятый и шестой управляемые делители 4-9 частоты, первый, второй и третий регистры 10-12 памяти, двоичный умножитель 13, первый второй и третий блоки 14-16 вычитания импульсов, блок 17 суммирования частот, триггер 18 и блок 19 управления. Вход блока 19 управления соединен с входной шиной устрой.ства. Выходы 20-23 блока 19 управления соединены соответственно с обнуляющими входами делителя 2 частоты, счетчика ,3, двоичного умножителя

13и входами управления записью регистров 10-12 памяти.

Выход генератора 1 соединен со счетными входами управляемых делителей 4, 5 и 9, первым информационным входом умнож1 теля 13 и подключен через делитель 2 к счетному входу счетчика 3. Выход счетчика 3 соединен с информационным входом регистра 10, подключенного выходом к управляющим входам делителей 4,6,7 и к информационному входу регистра

11.Выход регистра 11 соединен с управляющими входами делителей 5

,и 9 с информационным входом регистра

12,соединенного выходом с управляющим входом делителя 9. Выходы делителей 4 и 5 подключены к входам блока

14вычитания, соединенного первым выходом со счетным входом делителя 6 Выход блока 16 вычитания, подключенного входами к выходам делителей 5 и 9,соединен со счетным входом делителя 8.Выходы делителей 6 и 8 подключеНВ..к входам блока 15 .вычитания,соединенного выходом со счетными входами триггера 18 и делителя 7, выход которого подключен к второму информационному входу умножителя 13. Входы блока 17 суммирования частот, соеди ненного выходом с выходной шиной устройства, подключены соответствен но к выходу умножителя 13, второму выходу блока 14 вычитания, выходу делителя б и выходу триггера 18, Устройство работает следующим образом, В блоке 19 управления из каждого импульса входной последовательности дифференцируемого сигнала ) формируются управляклцие сигналы на выходах 20-23, определяющие последо вательность работы блоков устройства , С выхода генератора 1 импульсы высокой опорной частоты пост ьпают на вход делителя 2, счетные входы управляемых делителей 4, 5 и 9 и пе вый информационный вход двоичного умножителя 13, В делителе 2 опорная частота делится на постоянный коэф;фициент К пересчета. В делителях 4, 5 и 9 опорная частота делится на переменные коэффициенты, записанные в виде параллельного кода в соответствующие регистры 10-12 памяти и обновляемые после окончания каждого периода входной частоты Импульсы с выхода делителя 2 поступают на счетйый вход счетчика 3, где суммируются в промежутке времени, равном текущему периоду Т вход ного сигисша и формируемом путем по дачи на обнуляющий вход счетчика 3 сигналов с выхода 20 блока 19 управ ления после прихода каждого очере,цного импульса входной частоты. На выходе счетчика 3 в момент опроса о разуется код, пропорциональный закон чившемуся i-му периоду входной частотыЭтот код перед обнулением счетчика 3 по сигналу с выхода 21 блока 19 управления записывается в регистр 1 памяти. Перед записью, этого кода в регистр 10 памяти содержащийся в регистре 10 код М. ..пропорциональный предыдущему периоду , переписыв ется по сигналу с выхода 22 блока управления в регистр 11 памяти. Соответственно, перед записью этого кода содержащийся в регистре 11 код т-.у, пропорциональный периоду Ту,, по сигналу с выхода 23 блока управления, перезаписывается в1регистр 1 памяти. Таким образом, после окончания i-ro периода входной частоты в регис ре 10 памяти:, записан код N., в регистре 11 памяти - код РЦ-. , а в регистре 12 - код . На выходах управл1э мых делителей 4, 5 и 9 частоты формируются соотве ственно частоты(, пропорциональные. мгновенным значениям частот f( t( и fx t-{-2) ВХОДНОГО сигна :( t. и f Ct } ла в серединах периодов Т.( , Т,-, Т,. На первом выходе блока 14 вычитания образуется разность частот с выхода делителя 4 и выхода делителя 5, которая в делителе б делится на код N-J.. , записанный в регистре 10 памяти, На выходе делителя б образуется частота К fx(t) - fx(tv-) ,. f Т;; к ( - f И- ) fa пропорциональная среднему значению первой производной по времени входного сигнала в i-рм периоде. Знак этой производной определяется знаком разности частот, формируемым на втором выходе блока 14, В блоке 16 вычитания формируется разность частот с выходов делителей 5 и 9 частоты. Выходная скорость блока 16 делится в делителе 8 на код регистра 11 памяти. На выходе делителя 8 образуется частота тг KatfK t-t--) - fx(t,--2)b и W пропорциональная среднему значению первой производной по времени входного сигнала в (i-l)-oM периоде. Частоты с выходов делителей б и 8 поступают на входы блока 15 вычитания, на выходе которого образуется последовательность импульсов с частотой, пропорционсьльной приращению среднего значения первой производной входной частоты за время i-ro периода, С выхода блока 16 сигнал поступает на счетный вход триггера 18, осуществляющего деление выходной .частоты блока 16 на два, а также |На счетный вход делителя 7, в котором выходная частота блока 16 делится на код-N,.. резгистра 10 памяти, Частота на выходе делителя 7 к Uy(t ) - f (tn..«) -f(t.) пропорциональна- среднему значению второй производной по времени входного сигнала в i-ом периоде. На информационные (счетные входы счетчиков) входы двоичного умножителя 13 поступают выходы частоты делителя 7 и генератора 1, Емкость счетчиков двоичного умножителя 13 выбирается равной К - коэффициенту деления делителя 2. На выходе двоичного умножителя образуется последовательность импульсов со средней частотойf()- t пропорциональной текущему приращению (первой производной, зависящему от скорости ее изменения, т.е. от второ производной входной частоты по време ни. С помощью блока 17 суммирования частот осуществляется алгебраическое (в зависимости от знака на втором вы ходе блока 14) суммирование частот с выхода делителя б, триггера 18 и умножителя 13. Выходной сигнал с блока 17 поступает на выходную шину устройства. Таким образом, выходной сигнал устройства корректируется величиной половины приращения с выхода триггер 1 8 среднего значения первой производной по времени входного сигнала за время i-ro периода и ее текущим приращением с выхода умножителя 13, пропорциональным второй производной по времени входного сигнала. Благода этому компенсируется методическая , схЯибка, связанная с тем, что значение, первой производной, найденное ка отношение приращения входной частоты за время текущего периода, характери зует не мгновенное значение производ ной, а среднее значение за текущий период и должно быть отнесено к сере дине этого периода, а не к концу его Введением текущего приращения пер в(Ьй производной по времени, компенсир ется динамическая ошибка, связанная изменением значения первой производн за время следующего периода пропорци нрльно второй производной входного сигнала по времени. Это позволяет уменьшить динамическую погрешность формирования сигнала, пропорционального первой производной входной частоты по времени. Таким образом, по Оравнению с известным устройством, где выходной сигнал соответствует среднему значению первой производной по времени входной частоты за время закончившегося периода, в прегщагаемом выходной сигнал соотЭетствует мгновенному значению перНОй производной входной частоты по . . времени. Формула изобретения Устройство для дифференцирования частотно-импульсных сигналов, содерйсащее три регистра памяти, информационный вход первого из которых соединен с выходом счетчика, подклю ченного счетным входом через делител частоты к выходу генератора опорной частоты и к счетным входам первого и второго управляемых делителей Частоты, а выход первого регистра памяти соединен с управляющим входо первого управляемого делителя часто И с информационным входом второго регистра памяти, выход которого под ключен к управляющему входу второго правляемого делителя частоты, соединенного выходом с первым входом первого блока вычитания импульсов, первый выход которого подключен к счетному входу третьего управляемого делителя частоты, а второй вход соединен с выходом первого управляемого делителя частоты, причем входы управления записью регистров памяти и. обнулящие входы счетчика и делителя частоты подключены к соответствующим выходам блока управления, соединенного входом с входной шиной устройства, отличающееся тем, что, с целью уменьшения динамической ошибки, в устройство дополнительно введены четвертый, пятый и шестой управляемые делители частоты, второй и третий блоки вычитания импульсов, двоичный умножитель, триггер и блок суммирования частот, соединенный выходом с выходной шиной устройства и подключенный входами соответственно к выходу двоичного умножителя, второму выходу первого блока вычитания импульсов, входу третьего управляемого делителя частоты и выходу триггера, соединенного счетным входом с входом четвертого управляемого делителя частоты и выходом второго блока вычитания импульсов, входы .которого подключены к выходам .третьего и пятого управляемых делителей частоты, причем счетный вход пятого управляемого де:г1ителя частоты, соединенного управляющим входом с выходом второго регистра памяти и информационным входом третьего регистра памяти, подключен к выходу третьего блока вычитания импульсов, входы которого соединены с выходами второго и шестого управляемых делителей частоты, а счетный вход шестого управляемого делителя частоты, подключенного управляющим входом к выходу третьего регистра памяти, соединен с выходом генератора опорной частоты и первым информационным входом двоичного умножителя, подключенного входом обнуления к соответствующему выходу блока управления и соединенного вторым информационным входом с выходом четвертого управляемого делителя частоты, управляющий вход которого подключен к выходу первого регистра памяти и управляющему входу третьего управляемого делителя частоты. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство ССС №495675, кл. G Об G 7/18, 1974. 2.Авторское свидетельство СССР по заявке № 2506713/24, кл. G Об G 7/18, 1977. 3.Авторское свидетельство СССР №604008, кл. С 06 G 7/18, 1976 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дифференцирования частотно-импульсных сигналов | 1980 |

|

SU894729A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1978 |

|

SU723599A1 |

| Устройство для дифферинцирования частотно-импульсных сигналов | 1975 |

|

SU526916A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1977 |

|

SU732904A1 |

| Умножитель частоты импульсов | 1978 |

|

SU780175A1 |

| Устройство для дифференцированиячАСТОТНО-иМпульСНыХ СигНАлОВ | 1979 |

|

SU811281A1 |

| Цифровой частотомер | 1975 |

|

SU783701A1 |

| Устройство для дифференцирова-Ния чАСТОТы СлЕдОВАНия иМпульСОВ | 1978 |

|

SU798881A1 |

| Устройство для преобразования частоты в код | 1977 |

|

SU696604A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

Авторы

Даты

1980-06-25—Публикация

1978-03-01—Подача