(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ОБНАРУЖЕНИЯ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2003 |

|

RU2256937C1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU938396A1 |

| Устройство для измерения параметров четырехполюсника | 1989 |

|

SU1800395A1 |

| Измеритель амплитудно- и фазочастотной характеристики СВЧ-тракта | 1990 |

|

SU1721546A1 |

| Устройство для измерения фазового сдвига | 1984 |

|

SU1190294A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2527187C1 |

| ПРИЕМНИК АППАРАТУРЫ ПОТРЕБИТЕЛЕЙ СИГНАЛОВ ГЛОБАЛЬНЫХ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2001 |

|

RU2195685C1 |

| Цифровой формирователь частотно-модулированных сигналов с низким уровнем искажений | 2021 |

|

RU2765273C1 |

| Устройство для контроля амплитудно-частотных характеристик четырехполюсников | 1985 |

|

SU1259499A2 |

| СЧЕТЧИК АКТИВНОЙ ЭНЕРГИИ С ЧАСТОТНЫМ ВЫХОДОМ | 1992 |

|

RU2037830C1 |

/ ;. Л . , ,.; , : ,

Изобретение относится к области иаи ерительной и вычислительной техники и может быть использовано в линейных и нелинеА;ных преобразованиях .напряжения в двоиЧ ный позиционный код с наносекундными

временами преобразования, а также в радио пакации дпя цифрового детектирований видеосигналов из радист- или промежуточной частоты без преобразования в аналоговый видеосигнал.

Известен быстродействующий аналог «шф ровой преобразователь (АЦП) с параллель ной структурной схемоЙ так называемый АЦП считывания, содержащий компараторы схемы совпадений и антисовпадений, блоки памяти и управления С11. Его недостаток заключается в сложности.

Известен также АЦП, содержащий набор делителей напряжения, набор компараторов;, схемы антисовпадений, постоянную память, схему управления, выходной регистр.

Быстродействие известного АЦП определяется лишь задержкой сигнала в компараторе, схеме аптисовпадений, в постоянной памяти 2 . Недостатком такого АЦП я&ляется сравнительно низкие быстродействие и надежность.

Целью изобретения является упрощение конструкции и повышение надежности работы АЦП.

Поставленная цель достигается тем, что в АЦП, содержащий блок выработки эталонных сигналов, соединенный с блоком компа раторов, блок элементов антисовпадений, соединенный с первой группой входов постоянного запоминающего устройства, исто« ник опорного напряжения, блок управления и преобразователь напряжение-фаза, подклю ченный к входному зажиму аналого-пи ового преобразователя, введены два делителя мощности, блок модуляторов и два клоча, при этом первый делитель мощности между выходом феобразователя и другим входом блока компараторов, второй делитель мощности включен между одним из выходов источника опорного напрЯкения и второй группой входов постоянного запоминающего устройства, входы блока модуля торов подключены к блоку компараторов и первому ключу, а выходы - к блоку элеме TDB антисовпадений, входы первого и второ го ключей соединены соответственно с выходами источника опорного напряжения и блока управления, а выход второго ключа сое. оинен с входом блока выработки эталонных сигналов и BTOpbJM входом преобразователя напряжение-фаза.

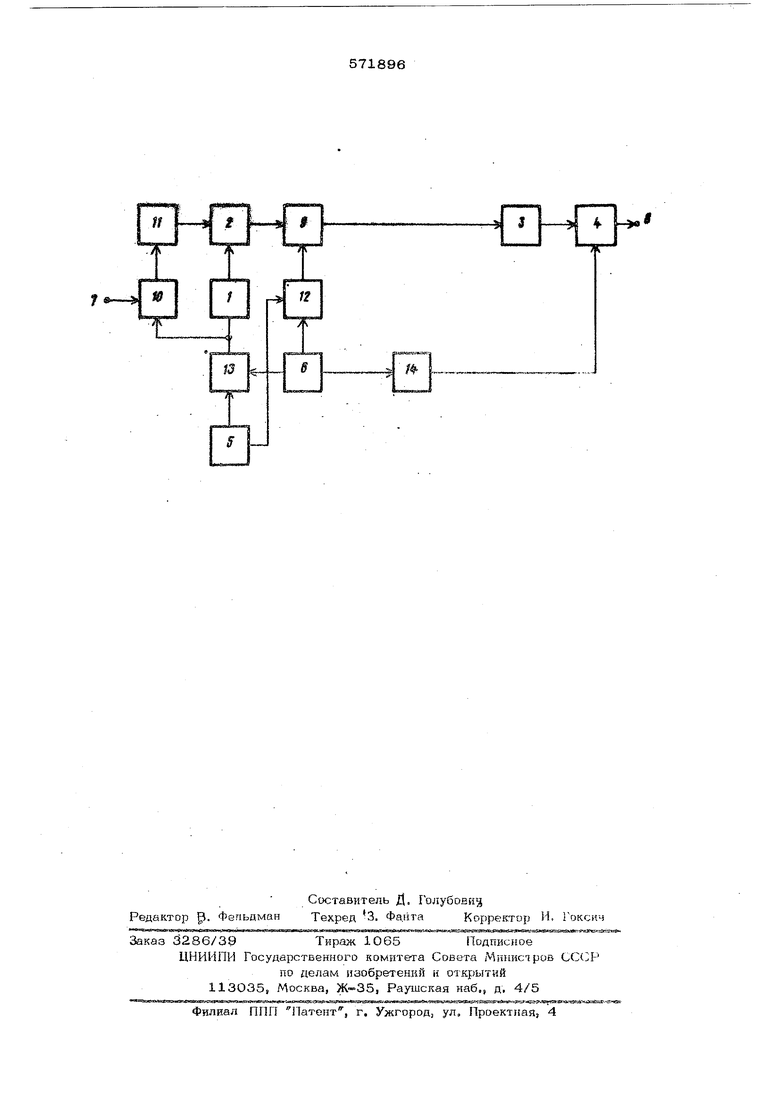

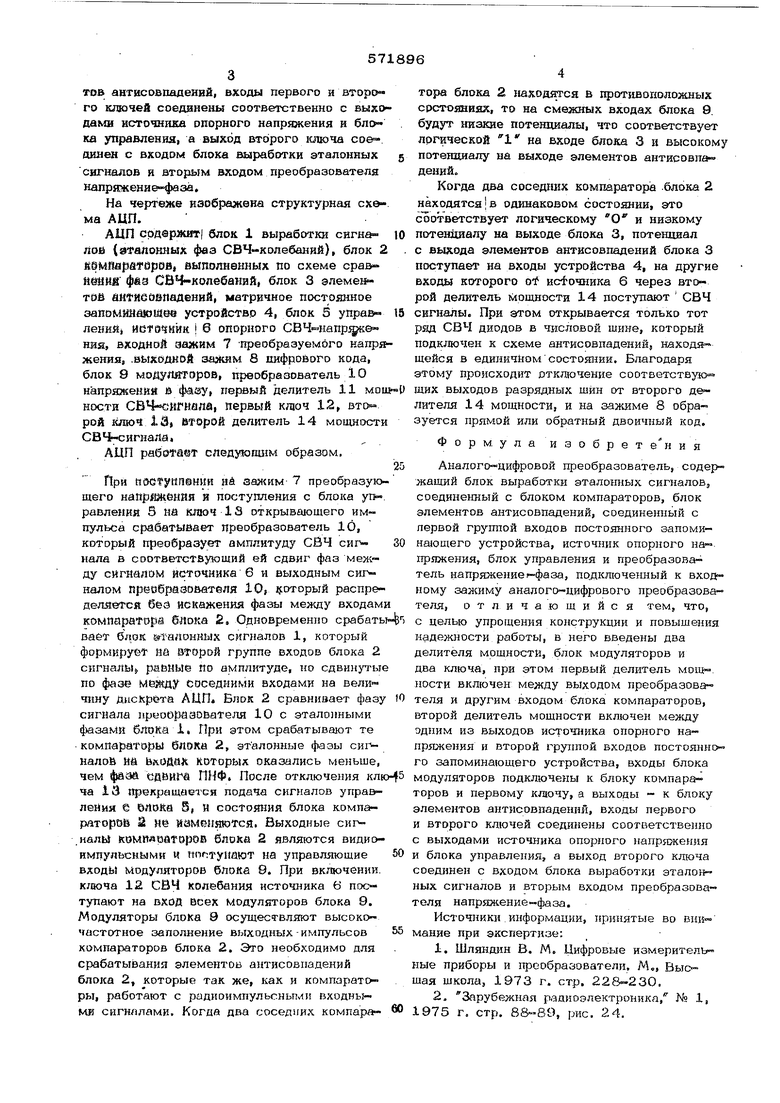

На чертеже изображена структурная схе-. ма АЦП. АЦП содержит блок 1 выработки сигнаЛое (iSTanoHHfalx фаз СВЧ-колебаний), блок 2 SSMBapSTOpOB, выполненных по схеме сравйеиий фйз СВЧ-кодебаний, блок 3 элемеатов адаяеоепадений, матричное постоянное запоминаюшее устройство 4, блок 5 управ лений ИОТОЧЯШ 8 опорного СВЧ« иапрфк© ния, входной зажим 7 -преобразуемого напря жения, .выходной эажим 8 цифрового кода, блок 9 модулйторов, преобразователь 10 напряжения в фаеу, первый делитель 11 мои ности СВЧ- сигиала, первый ключ 12 рой ключ, 13, второй делитель 14 мощности СВЧ-сигнала. АЦП рабетает следующим образом, При НОСУунпении ий 7 преобразующего напряжения и поступления с блока . равления 5 на ключ 13 открывающего им пульса срабатывает преобразователь 10, который преобразует амплитуду СВЧ сигнала в соответствующий ей сдвиг фаз между Сигналом источника6 и выходным сиг налом преобразо&ателя Ю, 1 оторый распределяется без искажения фазы мелсду входами компараторй блока 2, Одновременно срабатывает блок э-талонных сигналов 1, который формирует на второй группе входов блока 2 сигналы равные по амплитуде, но сдвинутые по фазе между соседними входами на величину Дискрета АЦП. Блок 2 сравнивает фазу сигнала приоорааователя 10 с эталонными фазами блока i. При этом срабатывают те . компараторы блока 2, эталонные фазы сипналоб Ий ЬлОДах которых оказались меньше, чем фйэа еавига ПНФ. После отключения клю Ча 13 1грекращае7 ся поДача сигналов управлейия е блока 5, и состоямия блока компаратороб 2 не изменяются. Выходные налы компараторов блока 2 являются видноимпульсными и нпптукают на управляющие входы модуляторов блока 9. При включении, ключа 12 СВЧ колебания источника 6 пос тупают на вход всех модуляторов блока 9. Модуляторы блока 9 осуществляют высокочастотное заполнение выходных-импульсов компараторов блока 2. Это необходимо для срабатывания элементов а} тисовпадений блока 2, которые так же, как и компаратсиры, работают с радиоимпульсными входнь - ми сигналами. Когда два соседних компаратора блока 2 находется в противоположных срсто5шиях, то на смежных входах блока 9. будут низкие потенциалы, что соответствует логической 1 на входе бпока 3 и высокому потенциалу на выходе элементов антисовла дений.

Когда два соседних компаратора .блока 2 находятсяjв одинаковом состоянии, это соответствует логическому О и низкому потенциалу на выходе блока 3, потенциал с выхода элементов антисовпадений блока 3 поступает на входы устройства 4, на другие входы которого of источника 6 через второй делитель мощности 14 поступают СВЧ сигналы. При этом открывается только тот ряд СВЧ диодов в числовой шине, который подключен к схеме антисовпадений, находя- щейся в единичном состоянии. Благодаря этому происходит отключение соответствующих выходов разрядных шин от второго де лителя 14 мощности, и на зажиме 8 образуется прямой или обратный двоичный код. Формула изобретения Аналого-цифровой преобразователь, содержащий блок выработки эталонных сигналоВэ соединенный с блоком компараторов, блок элементов антисовпадений, соединенный с первой группой входов постоянного запоминшощего устройства, источник опорного на- пряжения, блок управления и преобразователь напряжение1 фаза, подключенный к входному зажиму аналого-цифрового преобразователя, отличающийся тем, что, с целью упрощения конструкции и повышения надежности работы, в него введены два делителя мощности, блок модуляторов и два ключа, при этом первый делитель мощ-, ности включен между выходом преобразователя и другим входом блока компараторов, второй делитель мощности включен одним из выходов источника опорного напр51жения и второй груттой входов постоянного запоминающего устройства, входы блока модуляторов подключены к блоку компараторов и первому ключу, а выходы - к блоку элементов антисовпадений, входы первого и второго ключей соединены соответствешш с выходами источника опорного напряжения и блока управления, а выход второго ключа соединен с входом блока выработки этало}- ных сигналов и вторым входом преобразова теля напряэкение-фаза. Источники. информации, принятые во гзни-° мание при экспертизе; 1.Шлянш н В. М. Цифровые измерительные приборы и 1реобразователи, М,, Выещая щкола, 1973 г. стр. . 2, Зарубежная радиоэлектроника, 1 1, 1975 г. стр. , рис. 24.

Авторы

Даты

1977-09-05—Публикация

1976-05-24—Подача