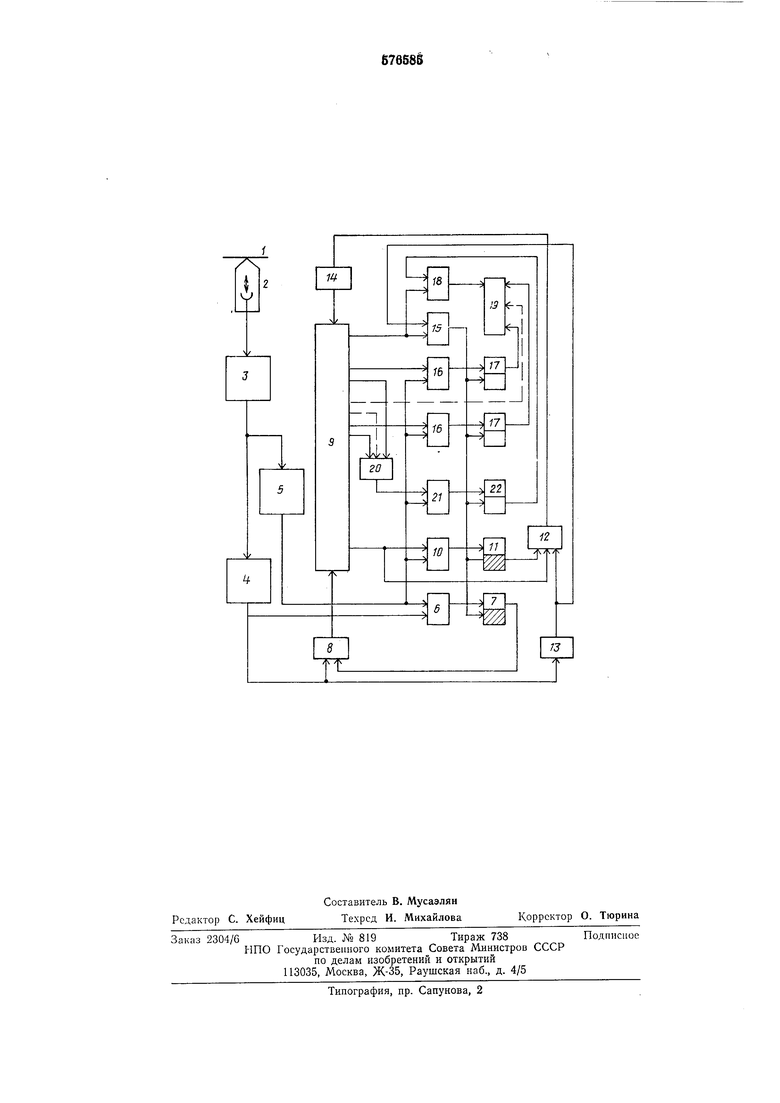

разрядов кодовой группы следуют после определителя 3 четных тактах, т. с. через один тактовый импульс. При поступлепии на схему совпадения 6 одновременно тактового и кодового импульса Tppirrep управления 7 переходит в состояние «1 и разрешает прохоладение тактовых импульсов через схему совпадения 8 на счетный вход распределителя 9. Если второй выделенный раснределителем 9 тактовый импульс совпадает с кодовым, то схема совпадения 10 переводит триггер блокировки 11 в состояние, которое запрещает прохождение через схему совпадения 12 инвертированных тактовых им 1ульсов с inieepTOpa 13 и вторых импульсов с распределителя 9. Если указанные импульсы не совпадают, тогда на ключ 14 сброса раснределителя 9 в пололсение «О проходит второй импульс распределителя, задерлсаппый иа полтакта, и переводит распределитель 9 в исходное состояние, переведя триггер уиравления 7 также в исходное состояние последним импульсом раснределителя 9, поступающим со сдвигом на полтакта со схемы совпадения 15.

Таким образом происходит поиск определителя начала кодовой группы в последовательности воспроизводимых тактовых и кодовых импульсов. При поступлении определителя сброс распределителя 9 в положение «О не произойдет и на его вход будут продолл :ать поступать тактовые пмпульсы. Поочередпо на входы схем совпадения 16 будут поступать четные импульсы с выходов распределителя 9 и кодовые импульсы, поступающие с селектора 5. Совпадающие импульсы переводят триггеры памяти 17 в состояние «1. В исходное состояние триггеры памяти 17 переводятся последним импульсом распределителя 9 через схему совпадения 15. Последний импульс с распределителя поступает на схему совпадения 18, которая выдает импульс «воспроизведение на регистратор кода 19 при условии, что все поступивщие четные импульсы с распределителя 9 через смеситель 20 на схему совпадения 21 не совпадут по времени с кодовыми импульсами, поступающими с селектора 5, и не нереведут триггер 22 в положение, запрещающее проход последнего импульса через схему совпадения 18. Если такое совпадение произойдет, что будет означать сбой в расположении кодовых импульсов группы, то регистратор 9 не считает воспроизведенный ложный код, т. е. произойдет запрещение регистрации ложной Информации,; Триггер 22 переводится в исходное состояние чмпульсом со схемы совпадения 15.

Устройство производит преобразование поступающего па его вход последовательного кода в параллельный.

Синхронная выборка кода обеспечивает повышенную помехозащищенность устройства, так как помехи могут пройти только в определенном порядке и в такте с кодовым импульсом. Синхронная выборка ложной информации обеспечивает запрет ее регистрации.

Вид примененной модуляции тактовых импульсов при записи определяет тип селектора: амплитудный, широтный, фазовый и т. д.

Формула изобретения

Устройство для воспроизведения служебной информации аналогового многоканального магнитографа, содержащее магнитную головку воспроизведения, подключенную через усилитель воспроизведепия к селектору и формирователю, выходы которых подключены к входам схемы совпадения, соединенные через триггер управления и вторую схему совпадения с выходом распределителя, вход сброса которого связан через ключ, третью схему совпадения и инвертор с входами первых двух схем совпадения и выходам формирователя, причем два других входа третьей схемы совпадения связаны собой через другую схему совпадения, подключенную к первому выходу раснределителя, и триггер памяти; выходы остальных триггеров памяти подключены к входам регистратора, а их входы установки единицы связаны через схемы совпадения с четными выходами распределителя, а входы установки нуля - с выходом схемы совнадения, один вход которой связан с последним выходом распределителя и с выходом инвертора, вторые входы всех схем совпадения триггеров памяти подключены к выходу селектора, отличающееся тем, что, с целью запрещения регистрации ложной информации, оно снабжено дополнительной схемой совпадения, соединенной одним входом с выходом селектора, вторым входом - через смеситель с нечетными выходами распределителя, а выходом-с входом «воспроизведение регистратора через дополнительный триггер памяти и схему совпадения, второй вход которой связан с последним выходом распределителя.

Авторы

Даты

1977-10-15—Публикация

1974-12-27—Подача