Изобретение относится к телеграфной связи, может быть исиользовано для синхронизации но никлам а пнаратуры лередачи двончной информапии, применяющей блочные корректирующие коды или маркерные разделительные сигналы.

Иззестно устройство синхронна ащгн по циклям, содержащее на1конитель с дещифраторол, выход которого подключен через последовательно соединенные,первую схему «И, счетчнк числа Ошибок, триггер и вторую схему «И ко входу распределителя, унравляемого генератором тактовых импульсов.

Цель изобретения - ускорение вхождения в синхронизм при сохранении высокой номеХОуСТОЙЧИВОСТИ.

(Предлагаемое устройство отличается тем, что между Быходом дещифратора и одним из входов второй схемы «И введены последовательно соединенные дополнительная схема «И, счетчак числа совпадений и блок памяти синхронного положення, .например, подключенный ко второму входу дополнительной схемы «И делитель частоты, унравляелтый генератором тактовых имнульсов, причем выход распределителя подключеи ко второму входу первой схемы «И.

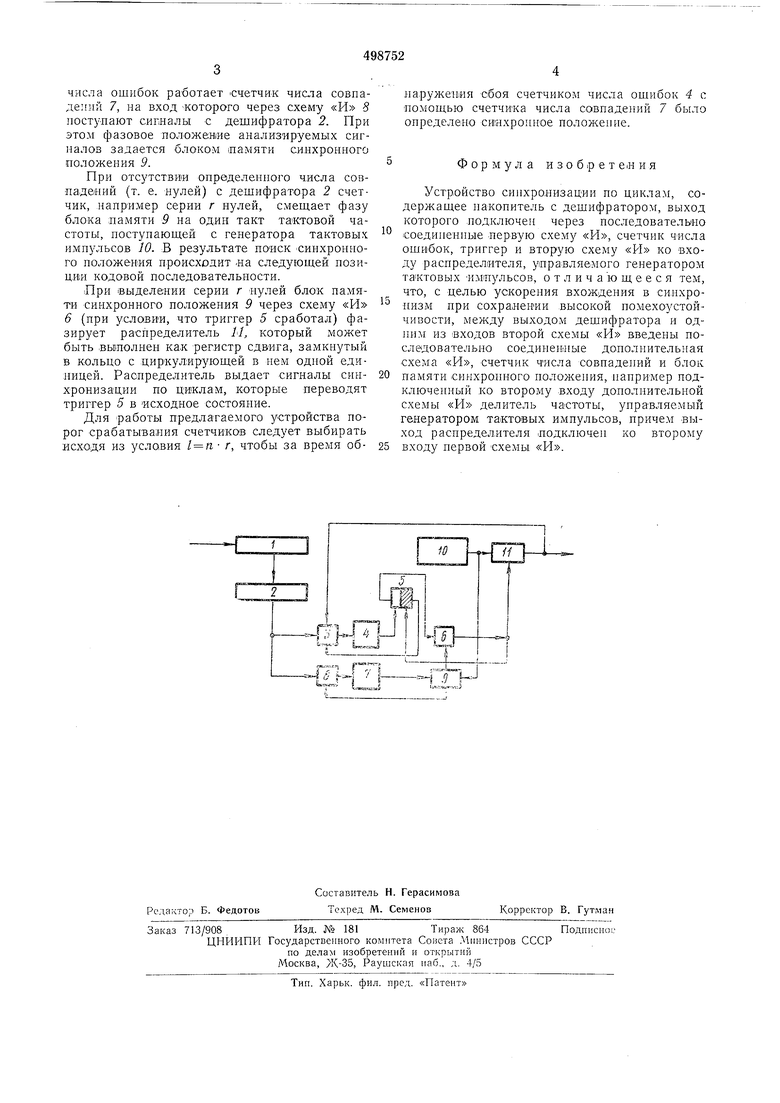

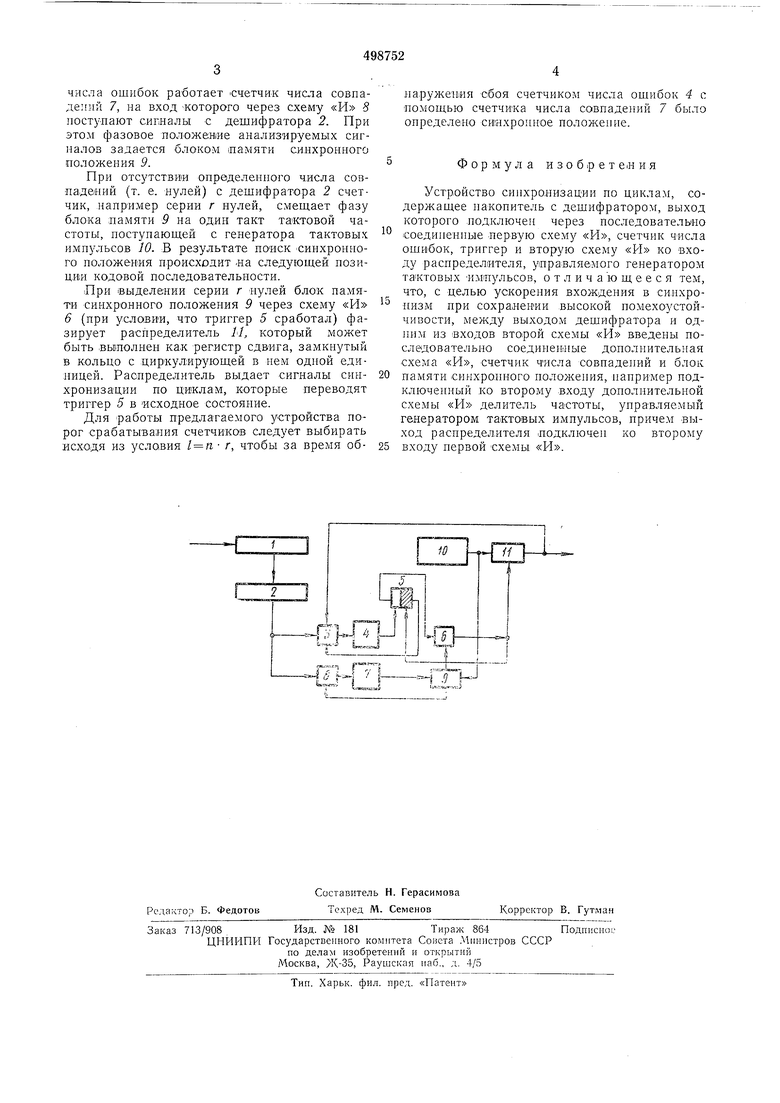

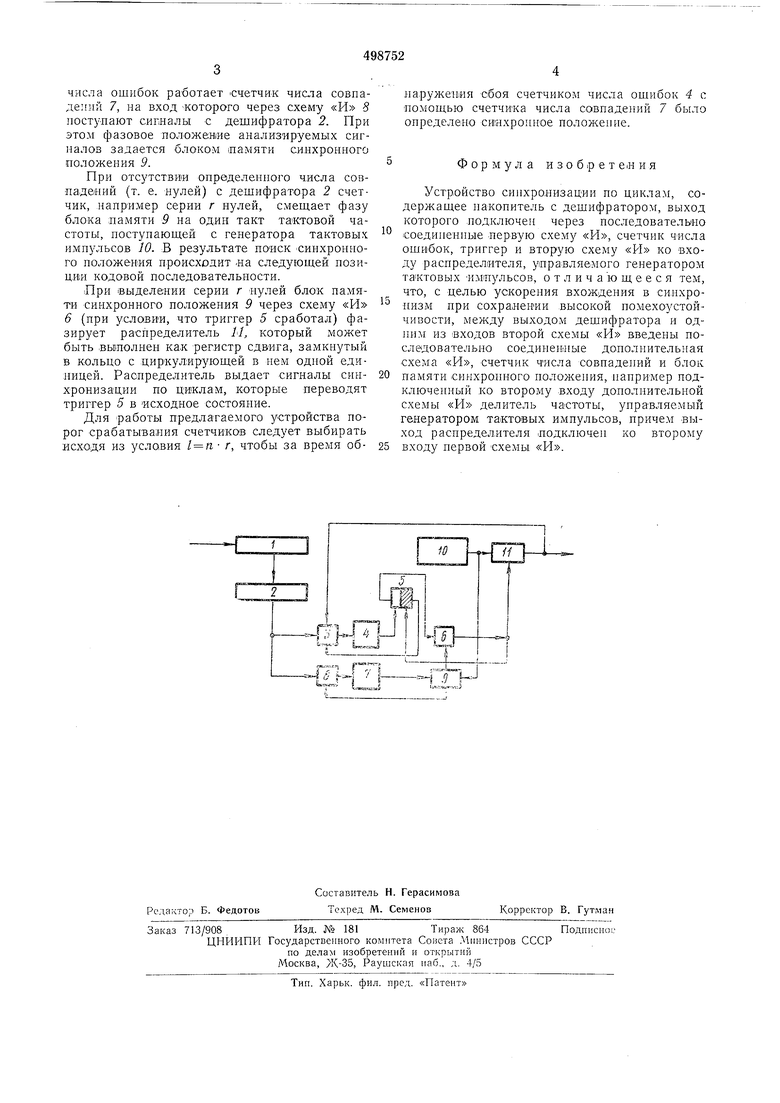

На чертеже ириведена блок-схема устройства.

Устройство содержит накопитель принятых

знаков 1 с денгифратором 2, первую схему «И , счетчнк числа ощибок 4, триггер 5 с разД.:лынз1мн пепями праБлеи я, вторую схему «И 6, счетчик числа совнадений 7, схему «И (S, блок намяти синхронного положения 9, генератор тактовых импульсов 10 и распределитель п.

Устройство работает следующим образом.

Нл приеме двоичная информация, за1;одирова;1ная блочными n,k кодами (:или с маркэриыми сигиалами, представляющими собой некоторую фиксированную комбинацию), поступает на накопитель 7 с дещ ифратором 2, на выходе которого появляются сигналы «1 при неудовлетворении закону построения кода (или маркеров) в принятой «пформацин на соответствующем сдаиге / (1 /-;:.«) накопи теля.

Через схему «И 3 эти сигналы, соответствуюпдие /-той фазе раснределителя в режиме захвата (удержаиия), подсчитываются счетчиком числа ошибок 4 и при достижении определенного порога срабатывания, например появлении Серии / сигналов ошибок, ио ценя управления переключают триггер 5 в состояние, когда левое плечо триггера имеет высокий потенциал «1. iB результате разрешается прохождение импульсов через схему «И 6 и закрывается вход на счетчик числа ошибок через схему «И 3. Одповременно со счетчико

чр1сла ошибок работает счетчик числа совпадений 7, на вход Которого через схему «И S поступают сигаалы с дешифратора 2. При этом фазовое положение анализируемых сигналов задается блоком памяти сиБхронного положения 9.

При отсутствии определенного числа совпадений (т. е. нулей) с дешифратора 2 счетчик, например серии г нулей, смещает фазу блока памяти 9 на один такт тактовой частоты, поступающей с генератора тактовых импульсов 10. :В результате поиск Синхронного положения происходит -на следующей позиции кодовой последовательности.

При iвыдeлeнии серии г нулей блок памяти синхронного положения 9 через схему «П 6 (при услави-и, что триггер 5 сработал) фазирует распределитель //, который может быть выполнен как регистр сдвига, замкнутый в кольцо с циркулирующей в нем одной единицей. Распределитель выдает сигналы синхронизации по циклам, которые переводят триггер 5 в -исходное состояние.

Для работы предлагаемого устройства порог срабатывания счетчиков следует выбирать исходя из условия 1 п- г, чтобы за время обнаруженйя сбоя счетчиком числа ощибок 4 с помощью счетчика числа совпадений 7 было определено синхронное положение.

Формула изобрет ea-i и я

Устройство синхронизации но циклам, содержащее накопитель с дешифратором, выход которого подключен через последовательно соединенные первую схему «И, счетчик числа ощибок, триггер и вторую схему «И ко входу распределителя, управляемого генератором тактовых ИМпульсов, отличающееся тем, что, с целью ускорения вхождения в си.нхронизм нри сохранении высокой помехоустойчивости, между выходом дещифратора и одним из входов второй схемы «П введены последовательно соедине1Ы1ые дополнительная схема «И, счетчик числа совпадений и блок памяти синхро.нного положения, нанример подключенный ко второму входу дополнительной схемы «И делитель частоты, унравляемый генератором тактовых импульсов, причем выход распределителя подключен ко второму входу первой схемы «И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации по циклам | 1977 |

|

SU641670A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| УСТРОЙСТВО для ТЕЛЕИЗМЕРЕНИЯ | 1970 |

|

SU277587A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для измерения коэффициента ошибок в цифровых системах передачи | 1984 |

|

SU1177920A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство декодирования циклических сдвигов м-последовательности | 1979 |

|

SU777867A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Телеграфное устройство для исключения обнаруженных ошибок | 1973 |

|

SU490268A1 |

Авторы

Даты

1976-01-05—Публикация

1973-04-02—Подача