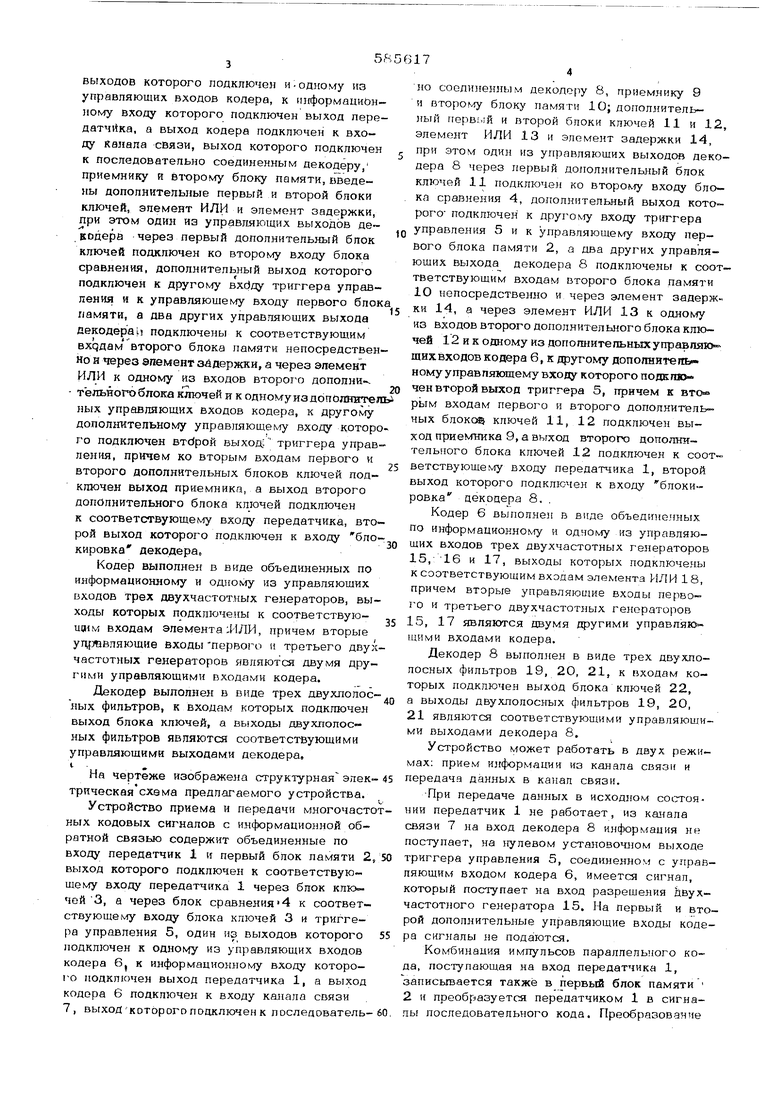

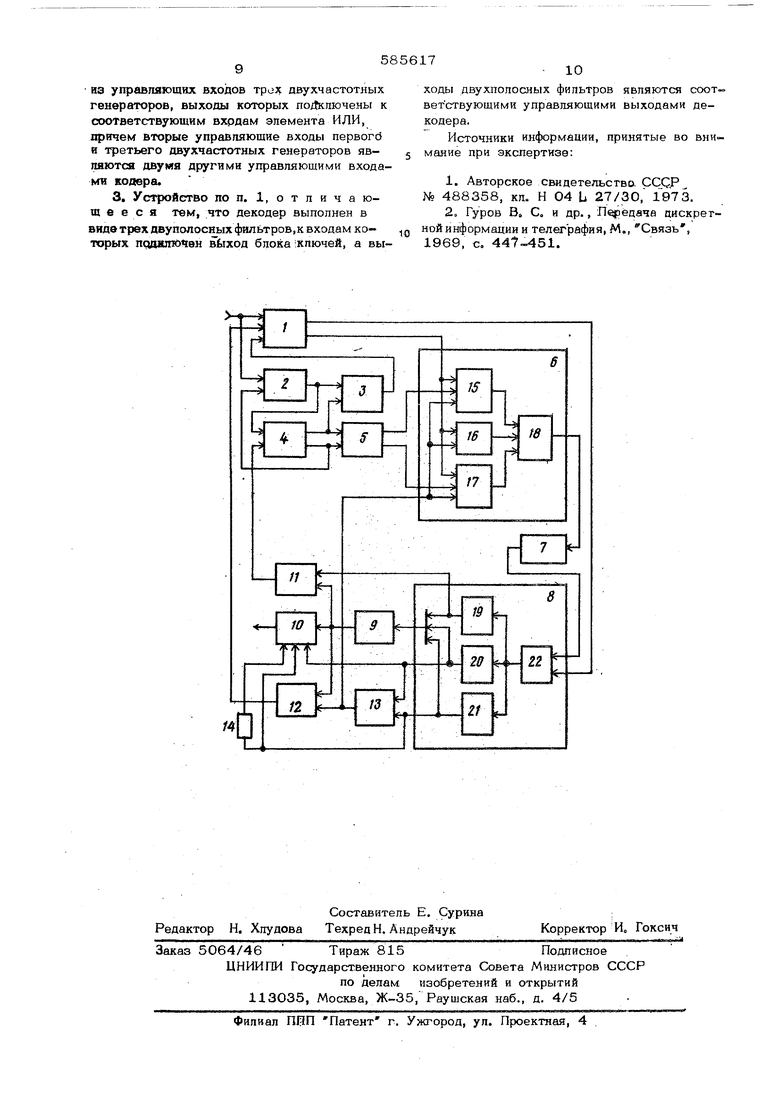

ВЫХОДОВ которого 1юдключе}г и одному из управляющих входов кодера, к шгформационлому входу которого подключен выход передатчика, а выход кодера подключен к вхоау калала связи, выход которого подключен к последовательно соединенным декодеру, приемнику я В1х)рому блоку памяти, вЪедены дополнительные первый и второй блоки ключей, эпемент ИЛИ и элемент задержки, при этом один из управляющих выходов декодера -через первый дополнительный блок ключей подключен ко второму входу блока сравнения, дополнительный выход которого подключен к другому вхбду триггера управления и к управляющему входу первого блок памяти, а два других управляющих выхода Декодера.) подключены к соответствующим вхддам второго блока памяти непосредствен но и через эпемент зйдернски, а через элемент ИЛИ к одному из входов второго дополни-. - тепьногобпока ключей и к oднo vfyиздoпoлнитel ных управляющих входов кодера, к другому дополнительному yпpaвпяющe y входу которо го подключен BTdpoft выход: триггера управ ления, причем ко вторым входам первого и второго дополнительных блоков ключей подключен выход приемника, а выход второго дополнительного блока ключей подключен к соответствующеKjy входу передатчика, вто рой выход которого подключен к входу бло кировка декодера. Кодер выполнен в виде объединенных по информационному и одному из управляющих входов трех двухчастотных генераторов, выходы которых подключены к соответствуюищм входам элемента JlЛИ, причем вторые ущлзвляющие входы nepeoi o и третьего двух частотных генераторов являются двумя другими управляющими входами кодера. Декодер выполнен в виде трех двухпопос ных фильтров, к входам которых подключен выход блока ключей, а выходы двухпопос- ных фильтров являются соответствующими управляющими выходами декодера. ч ., На чертеже изображена структурная элек трическаясхема предлагаемого устройства. Устройство приема и передачи многочасто ных кодовых сигналов с информационной обратной связью содержит объединенные по входу передатчик 1 и первый блок памяти 2 выход которого подключен к соответствующему входу передатчика 1 через блок клЮ чой3, а через блок сравнения4 к соответствующему входу блока ключей 3 и триггера управления 5, один из выходов которого подключен к одному из управляющих входов кодера 6, к информационному входу которо- I-O подключен выход передатчика 1, а выход кодера 6 подключен к входу канала связи 7, выход которого подключен к последовательно соединенным декодеру 8, приемнику 9 и Бтороглу блоку памяти 10; дополнительный перв.мй и второй блоки ключей 11 и 12, элемент ИЛИ 13 и элемент задержки 14, при этом один из управляющих выходов декодера 8 через первый дополнительный блок ключей 11 подключен ко BTopONfy входу блока сравнения 4, дополнительный выход которого- подключен к другому входу триггера управления 5 и к управляющему входу первого блока памяти 2, а два других управляющих выхода декодера 8 подключены к соот- тветствующим входам второго блока памяти 10 непосредственно и через элемент задержки 14, а через элемент ИЛИ 13 к одному из входов второго дополнительного блока ключей 12 и к одному из допопнитепьныхуправгшю- ших входов кодера 6, к другому дополните яьному управляющему входу которого подключен второй выход триггера 5, причем к вто рым входам первого и второго дополнительных блоков ключей 11, 12 подключен выход приемника 9, а выход второго дополнительного блока ключей 12 подключен к соот ветствующему входу передатчика 1, второй выход которого подключен к входу блокировка декоцера 8. . Кодер 6 выполнез в виде объединенных по информационному и одному из управляющих входов трех двухчастотных генераторов 15, 16 и 1 выходы которых подключены к соответствующим входам элемента ИЛИ 18, причем вторые управляющие входы первого и третьего двухчастотных генераторов 15, 17 являются двумя другими управляющими входами кодера. Декодер 8 выполнен в виде трех двухполосных фильтров 19, 20, 21, к входам которых подключен выход блока ключей 22, а выходы двухлолосных фильтров 19, 2О, 21 являются соответствующими управляющими выходами декодера 8, Устройство может работать в двух режимах; прием информации из канала связ1 и передача данных в канал связи. При передаче данных в исходном со(ттояНИИ передатчик 1 не работает, из кштала связи 7 на вход декодера 8 информация не поступает, на нулевом установочном выходе триггера управления 5, соединенном с управляющим входом кодера 6, имеется сигнал, который поступает на вход разрещения Ьвухчастотного генератора 15. На первый и второй дополнительные управляющие входы кодера сигналы не подаются. Ko rбинaция импульсов параллельного кода, поступающая на вход передатчика 1, записывается также в первый блок памяти 2 и преобразуется передатчиком 1 в сигналы последовательного кода. Преобразование сигналов(11осыпок)последователь юго кода в частотно-модулированные сигналы осущест вляется кодером 6, который формирует пакеты двух частот, соответствующие посыпкам последовательного кода. Частоты в пакетах зависят от наличия управляющих. сигналов на управляющем и дополнительных управляющих, входах кодера 6: при наличии сиг нала на управляющем входе кодера б на входе ра рещения двухчастотного генератора 15 также имеется сигнал, -который разрещает модуляцию приходяших на информационный вход кодера 6 с передатчика 1 сигналов поспедо f, (TOKOватепьного кода частотами 4/ и вая посыпка модутшруется частотой , а бестоковая посылка - частотой f, . При пере даче знака с передатчика 1 на вход блокировка декодера 8 поступает сигнал, ,закрываюший блок ключей 22 декодера 8 поего входу управления, тем самым запрещая прохождение сигналов из канала связи 7 на вход декодера 8. Таким образом, модулированные частотами i и tj, сигналы поспе- ; довательного кода поступают в канап связи 7, По окончании передачи комбинации последовательного кода в канал связи 7 сигнал с входа блокировка декодера 8 снимается блок ключей 22 открывается, декодер 8 разблокируется и становится возможным прием информации из канала связи 7 на декодер 8 . Сигналы автоответа с приемной стороны на передающую поступают через канал 7 в виде комбинаций пакетов двух час тот f J и i , соответствующих посылкам последовательного кода, и проходят на вход декодера 8. При этом кo fбинaции пакетов двух частот f и f проход5гг через открытый блок ключей 22 декодера 8 на входы двухполосных фильтров 19, 2О, 21, но так как только двухполосный фильтр 19 настрое на пропускание частот fj и{ то только I на его выходе появляются сигналы, проходящие на первый управляющий выход декодера 8 и далее - на вход управления первого дополнительного блока ключей 11,; открывая его. Импульсы последовательного кода с информационного выхода декодера 8 поступают на приемник 9, преобразуются в параллель51ый код на его выходе, который затем через открытый первый дополнительный блок ключей 11 поступает на второй вход блока сравнения 4. В блоке сравнения 4 происходит поразрядный анализ коктбинаций параллельного кода, поступающих на оба его входа. В случае равенства комбинаций на входах блока сравнения 4 на его дополнительном выходе появляется сигнал, который подается на управляющий вход первого блока .памяти 2, производя стирание записанной в нем первой комбинации импульсов параллельного кода, поступивщей ранее также нп вход передатчика 1 и переданной в кпнпл связи 7. Упомянутый сигнал с дополнительного , выхода блока сравнения 4 поступает также на единичный установочный вход тригт-ер а управления 5, который переключается и подает сигнал со своего второго выхода на второй дополнительный управляющий вход кодера 6, подготавливает его к работе, раэре- щая модуляцию посыпок последовательного кода, которые поступают на v нфopмaциoнныa вход кодера 6, частотами и f, .При этом сигнал с управляющего входа кодера 6 (формируемый другим ллечом триггера 5) снимается. Следующая комбинация последовательного кода с передатчика 1 теперь же передается в канал связи 7 на частотах f и . (токовая посыпка модулируется частотой f, , бесто ковая - частотой Ig). В случае неравенства комбинаций на входах блока сравнения 4 на его выходе появляется сигнал, который подается fJs управляющий вход блока ключей 3 и на нулевой установочный вход триггера управления 5, подтверждая его состояние. Сигнал , поступающий на управляющий вход блока ключей 3 разрещает прохождение комбинации сигналов параллельного кода неверно принятого знака с первого блока памяти 2 на передатчик 1, который повторяет ее передачу в канал связи 7 на частотах j Таким образом, передача в канал связи 7 первой комбинации кода и повторение неправильно принятых комбинаций осу1иествлявтся путем использования частотij иIj, а при правильном приеме автоответа передача следующей комбинации кода в канал связи 7 осуществляется с использова}1И9М частот -и. При приеме данных в исходном состоянии приемник 9 не работает, а на входе бло- . кировка декодера 8 сигнал отсутствует, т,е, опок ключей 22 оказывается oткpыты, При приходе из канала связи 7 сигналов с частотами i и fj соответствующих посылкам поспедоветепыюго кода, начинает работать двухлолосный фильтр 20 декодера 8. На информационном выходе декодера в появляются посылки последовательного кода, поступающие на приемник 9 и преобразуемые им в сигналы параллельного кода. Сигнал с второго управляющего выхода декодера 8 (выход двухполосногофипьтра 20) производит стирание информации из второго блока памяти 10 без выдачи ее на выход устройства через элемент ИЛП 13, открывает второй дополнительный блок клрчой 12. При этом счгнапы параппельного кода г: пыхопа приемника 9 через дополнительны бпок клю чей 12 поступают на вход передатчика 1, который фop fиpyeт посылки последовательного кода на информацио51ном входе кодера повторяющие Посылки, принимаемые из кана па связи 7. На выходе декодера 8 формируются пакеты частот f и т соответствуюшие посыпкам последовательного кода на информационном входе кодера 6. Наличие Частот jf и f.,при этом определяется напичием сигнала, снимаемого с выхода элеме та ИЛИ 13 на первый дополнятельный управляющий вход кодера 6. Этот сигнал, посту пая на входы запрета двухчастотных генера торов 15 и 17, запрещает их работу, а пос тупая на вход разрешения двухчастотного генератора 16, настроенного на частоты I и А разрешает модуляцию посылок по. ледовательного кода именно этими частота- ми. При появлении на входе декодера 8 пос- педоватепьности сигналов с частотами fg и f J начинает работать двухполосный фильтр 21, настроенный на эти частоты, сигнал с выхода которого поступает на третий управляющий выход декодера 8. Этот сигна списывает ранее принятую информацию в па раллельном коде со второго блока памяти Ю на выход устройства я через время, определяемое элементом 14, стирает информацию в блоке памяти 1О, подго тавливая его к приему очередной комбинаци сигналов принятого кода с выхода приемник 19. Работа остальных устройств в режиме приема осуществляется также, как при поступлении из канала свззи 7 сигналов с частотами i, Hfj. К Таким образом, при приеме из канала связи 7 комбинации сигналов кода в виде пакетюв частот и fj свидетельствукицих об ошибочном приеме предыдущей кодовой комбинации, осуществляется стирание ранее при)1ятой кодовой комбинации во втором бло ке памяти 10 (без считывания ее на выход устройства) и последующее запоминание в нем комбинашга кода, поступающей с выхода п|И1емняка 9. При приеме иа канатш связи 7 комбинаПИИ кода в виде пакетов частот 1 и 1., свидетепьствуюших о правильности ранее принятой комбинации кода, осуществляется счить1 вание предыдущей комбинации Koqa из второго блока памяти 10 на выход устройства, затем обнуления блока и запись в него очередной принятой приемником 9 комбинации кода. Ё обоих случаях кок1бицация кода с выхо да приемника 9 передается снова в канал. связи 7 на частотах j и f, являясь сигналом автоответа на передакмций пункт, где производится анализ правильности прини« маемой на приемном пункте комбинации кода. По сравнению с известным устройством предлагаемое изобретение позволяет увеличить скорость передачи информации, испол аовать симплексные каналы и повысить надежность восприятия автоответа. Формула изобретения 1. Устройство приема и передачи многочастотных кодовых сигналов с информационной обратной связью, содержащее объединенные fo входу передатчик и первый блок памяти выход которого подключен к соответствующему входу передатчика через блок ключей, а через блок сравнения - к соответствующему входу блока ключей и триггера управления один из выходов которого подключен к одному из управляющих входов кодера, к информационному входу которого подключен выход передатчика, а выход кодера подключен к входу канала связи, выход которого подключен к последовательно соединенным декодеру приемнику и второму блоку памяти, о т п и-i чающееся тем, что, с целью повышения скорости передачи информации и увеличения помехоустойчивости приема информации, в него введены дополнительные первый и второй блоки ключей, элемент ИЛИ и элемент задержки, при этом один из управляющих выходов декодера через первый дополнительный блок ключей подключен ко второму входу блока сравнения, дополнительный выход которого подключен к другому входу триггера управления и к управляющему входу первого блока памяти, а два других управляющих выхода декодера подключены к соответствующим входам второго блока памяти непосредственно и через элемент задержки, а через элемент ИЛИ-к одному из входов второго дополнительного блока ключей и к одному из лопрлнительныхуправляющих входов кодера, к другому дополнительному управляющему входу которого подключен второй выход триггера управленпЯ|.причем ко вторым входам первого и второго дополнительных блоков ключей подКпючен выход приемника, а выход второго дополнительного блока ключей подключен к соответствующему входу передатчика, второй выход которого, подключен к входу блокировка декодера. 2. Устройство по п. 1, о т л и ч а ю - щ е е с я тем, что кодер выполнен в виде объединенных по инфopмaциoш o fy и одно(у

нз управляющих входов трох двухчастотяых генераторов, выходы которых подключены к соответствующим вхрдам элемента ИЛИ, причем вторые управляющие входы первогб и третьего двухчастотных генераторов являются двумя другими управляющими входами кодера.

3, Устройство по п. 1, о т л и ч а юш е е с я тем, что декодер выполнен в вида трех двуполосных фильтров,к входам которых подключен блока ключей, а выходы двухполосных фильтров являются соот ветствующими управляющими выходами декодера.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство. СССР № 488358, кл, Н 04 Ь 27/30, 1973,

2.Гуров В С, и др., Передача дискретной информации и телеграфия, М., Связь , 1969, с, 447-451.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приема и передачи многочастотных кодовых сигналов с информационной обратной связью | 1977 |

|

SU745010A2 |

| Система передачи дискретной информации | 1981 |

|

SU978374A1 |

| СПОСОБ РАДИОСИГНАЛИЗАЦИИ И ОБНАРУЖЕНИЯ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2099791C1 |

| СИСТЕМА ТЕЛЕСИГНАЛИЗАЦИИ СО СКВАЖИН | 1997 |

|

RU2126994C1 |

| Система телемеханики | 1990 |

|

SU1711216A1 |

| Способ формирования цифрового дельта-потока импульсов в групповом передатчике сигналов управления и взаимодействия | 1990 |

|

SU1815806A1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2008 |

|

RU2384012C1 |

| Ретранслятор системы связи | 1982 |

|

SU1081808A1 |

| Телеизмерительная система | 1983 |

|

SU1179411A1 |

| УСТРОЙСТВО ДИСТАНЦИОННОЙ СИГНАЛИЗАЦИИ | 1992 |

|

RU2032229C1 |

Авторы

Даты

1977-12-25—Публикация

1974-09-06—Подача