(54) ПЕРЕДАТЧИК ТЕЛЕГРАФНОГО АППАРАТА

| название | год | авторы | номер документа |

|---|---|---|---|

| Передатчик телеграфного аппарата | 1974 |

|

SU504310A1 |

| Передатчик телеграфного аппарата с автоконтролем | 1978 |

|

SU739749A2 |

| Передатчик телеграфного аппарата | 1976 |

|

SU649155A1 |

| Передатчик телеграфного аппарата с автоконтролем | 1976 |

|

SU568199A1 |

| Передатчик телеграфного аппарата с автоконтролем | 1979 |

|

SU886297A2 |

| ПЕРЕДАЮЩАЯ ЧАСТЬ ТЕЛЕГРАФНОГО АППАРАТА | 1971 |

|

SU310410A1 |

| ПЕРЕДАТЧИК ТЕЛЕГРАФНОГО АППАРАТА | 1973 |

|

SU379986A1 |

| Передатчик телеграфного аппарата | 1986 |

|

SU1401632A1 |

| Передатчик телеграфного аппарата | 1977 |

|

SU658768A1 |

| Передатчик телеграфного аппарата | 1987 |

|

SU1494241A2 |

1

Изобретение относится к технике передачи дискретной информации и может использоваться 1в качестве электронного передатчика телеграфного аппарата.

По основному авт. св. № 50431О из- вестен передатчик телеграфного аппарата,, содержащий клавиатуртый комбинатор и трансмиттерную приставку, выходы которых подключены к дешифратору и через многоступенчатый буферный накопитель - с соответствуюшими входами передающего распределителя, подключенного к выходному блоку, дополнительный выход которого через последовательно соединенные блок для сопряжения в элемент сравнения подкточен к первому входу выходного элемента И, причем выходы дешифратора подключены к входам элемента ИЛИ, выход последнего через дополнительную ячейку многоступенчатого буферного накопителя подключен к входу первого трнггера второй вход которого соединен со вторым выходом передающего распределителя, а выход - с первым вхоаом элемента И, второй вход которого соединен с третьим выходом передающего распределителя, а выхоа элемента И подключен к второму входу выходного элемента И и счетному входу второго триггера, установочные входы которого соединены с выходами Дешифратора, а выход - со вторым входом элемента сравнения.

Однако известный передатчик телеграфного аппарата не обеспечивает высокую точ ность контроля передачи информации.

Цель изобретения - повышение точности контроля передачи информации.

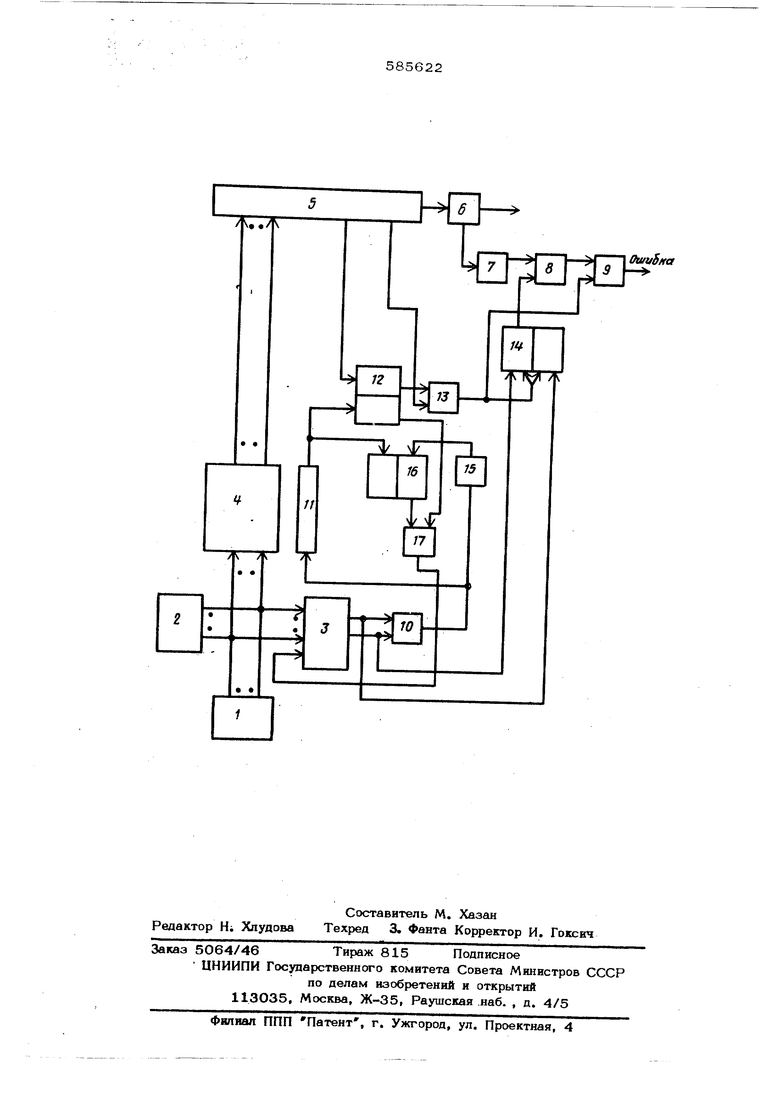

Для этого в передатчик телеграфного аппарата, содержащий клавиатурный комбинатор и трансмиттерную приставку, выходы которых подключены к дешифратору и через многоступенчатый буферный . накопитель - с соответствующими входами передающего распределителя, подключенного к выходному блоку, дополнительный выход которсяго через последовательно соединенные блок для сопряжения и, элемент сравнении подключейк первому входу выходного элемента И, причем выходы дешифратора подключены к входам элемента ИЛИ, выход последнего через до полнительную ячейку многоступенчатого буферного накопителя подключай к входу первого триггера, второй вход которого соединен .со вторым выходом передающего распределителя, а выход - с первым входом элемента И, второй вход которого соединен с третьим выходом передающего распределителя, а выход элементами подключен к второму входу выходного элемента И и счетному входу второго триггера, установочные входы которого соединены с выходами дешифратора, а выходсо вторым входом элемента сравнения, введены последовательно соединенные элемент задержки, дополнительны/ триггер и дополнительный элемент И, причем выход элемента tiTIH подключен к входу элемента задержки, выход дополнительной ячейки многоступенчатого буферного накопителя подключе к другому входу.J дополнительногр триггера, а дополнительный выход первого триггера по ключен к другому входу дополнительного элемента И, выход которого подключен к дополнительному входу дешифратора. На чертеже представлена структурная эле трическая схема передатчика телеграфного аппарата. Передатчик телеграфного аппарата содержит клавиатурный комбинатор 1, трансмиттерную приставку 2, выходы которых подклю чены к дешифратору 3 и через многоступенчатый буферный накопитель 4 (с п ступенями) - с соответствующими входами пе(редаюшего распределителя 5, подключенного к выходному блоку 6, дополнительный быход Которого через последовательно соединенные блок 7 для сопряжения и элемент 8 сравнения подключен к первому входу выходного элемента И 9, причем выходы дешифратора 3 подключены к входам элемента ИЛИ 10, выход последнего через дополнительную ячей ку 11 многоступенчатого буферного, накопителя 4 подключен к входу первого триггера 12, второй вход которого соединен с вторым выходом передающего распределителя 5, а выход - с первым входом элемента И 13, второй вход которого соединен с третьим выходом передающего распределителя 5,. а вы ход элемента И 13 подключен к второму вхо ду выходного элемента И 9, и счетному входу второго триггера 14, Установочные входы которого соединены с выходами дешифратора 3 а выход - с вторым входом элемента 8 сгйвнения-последовательно соединенные эл мент 15 задержки, дополнительный триггер 16 и дополнительный элемент И 17, причем выход элемента RfJH 1О подключен к входу элемента 15 задержки, выход дополнительной ячейки 11 многоступенчатого буферного накопителя 4,подключен к другому входу дополнительного триггера 16, а дополнительны выход первого триггера 12 подключен к другому входу дополнительного элемента И 17, выход которого подключен к дополнительному входу дешифратора 3. Передатчик телеграфного аппарата работает следующим образом. При передаче информации с клавиатурного комбинаторна 1 или с трансмиттерной приставки 2 кодовые комбинации вводятся в многоступенчатый буферный накопитель 4, в котором осуществляется продвижение комбинаций с первой ступени в п -ую-ступень. При наличии кодовой комбинации в п-ой ступени многоступенчатого буферного накопителя 4 происходит запуск передающего распределителя 5. При этом кодовая комбинация многоступенчатого буферного накопителя 4 поступает в передающий распределитель 5, в котором осуществляется формирование стартстопной последовательной комбинации и передача ее через выходной блок 6 в линию. При записи в многоступенчатый буферный накопитель 4. кодовой комбинации 1О10 или 01О1.... срабатывает дешифратор 3, выходной сигнал которого через элемент ИЛИ 10 поступает на вход дополнительной ячейки 11 многоступенчатого буферного накопите пя 4 и записывает в нее 1. Выходной сигнал дешифратора 3 подается также на один из входов триггера 14. Если в многоступенчатый буферный накопитель 4 записывается комбинация 1О10. то сигналом с выхода дешифратора 3, соответствующим этой комбинации, триггер 14 устанавливается в положение, при котором на его выходе появляется сигнал О. Одновременно выходной сигнал дешифрзаторза 3 через элемент 15 задержки поступает на вход триггерза 16 и изменяет его состояние так, что выходной сигнал элемента И 17 запрющает по дополнительному входу дешифратор 3 дешифрзадию последующих комбинаций 101О.... или 0101,,.. (после записи в дополнительную ячейку 11 буферного накопителя 4 и предварительной установки триггера 14). С продвижением комбинации 1010.... от первой ступени многоступенчатого буферного накопителя 4 в п-ую продвигается сигнал 1 от первой ступени дополнительной ячейки 11 в п -ую ступень дополнительной ячейки 11. При считывании с последней ( а-и) ступени многоступенчатого буферного накопителя 4 кодовой комбинации 101О .... считывается сигнал I с fi -И ступени дополнительной ячейки 11 многоступенчатого буферного накопителя 4. Этим сигналом триггер 12 и триггер 16 переводятся в положение, когда на вход элемента И 13 вьшается сигнал разрешения, а на входы элемента И 17 подаются сигнал разрешения (с выхода триггера 16) и сигнал запрета (с выхода триггера 12). Благодаря этому на дополнительный вход дешифратора 3 продолжает воздействовать запрещаюший сигнал (с выхода элемента И 17). При формировании передающим распределителем 5 элементов кодовой комбинации с его выхода через элемент И 13 на счетный вход триггера 14 поступают сигналы, с приходом каждого из которых триггер 14 изменяет свое состояние и на его выходе формируется комбинация 101О...,, В момент передачи стопового элемента комбинации сигналом с выхода передаюш.его распределителя 5 триггер 12 устанавливается в исходное состояние, когда с его выходов на вход элемента И 13 выдается сигнал запрета, а на вход элемента И 17 сигнал разрешения. На выходе элемента И 17 появляется сигнал, разрешающий дещифрацию очередной комбинации 1010... (0101,.J В случае поступления комбинации 0101.., триггер 14 выходным сигналом дешифратора 3 предварительно устанавливается в положение , что обеспечивает формирование на его выходе комбинации 01О1... (с поступ лением сигналов от передающего распределителя 5). При правильной работе блоков передатчика телеграфного аппарата комбинации 1010... (0101...), формируемые триггерюм 14, идентичны комбинациям, передаваемым в линию с выходного блока 6, и поэтому элемент 8 сравнения не выдает разрешающего сигнала на вход выходного элемента И 9, а на его выходе сигнал Ошибка отсутствует. При неправильной работе одного из блоков, передатчика телеграфного аппарата, приводящей к искажению передаваемых комбинаций, элемент 8 сравнения при формировании триггером 14 комбинаций 1010... (01О1....) выдает сигнгш несравнения. Этот сигнал для выходного элемента И 9 ЯЕ ляется разрешающим и поэтому стробирующие сигналы с выхода элемента И 13 проходят на выход выходного элемента И 9 как сигналы Ошибка. Периодичность контроля передатчика телеграфного аппарата определяется частотой появления комбинаций 1010... и 0101.,.. При непрерывной вьщаче с клавиатурного комбинатора 1 или с трансмиттериой приставки 2 комбинаций 101О.... 010...{. осуществляется непрерывный контроль работы передатчика телеграфного аппарата. формула изобретения Передатчик телеграфного аппарата по авт.св. № 504310, отличающийс я тем, что, с целью повышения точности контроля передачи информации, в него введены последовательно соединенные элемент задержки, дополнительный триггер и дополнительный элемент И, причем выход элемента «ИЛИ подключен к входу элемента задержки, выход дополнительной ячейки многоступенчатого буферного накопителя подключен к другому входу дополнительного триггера, а дополнительный выход первого триггера подключен к другому входу дополнительного элемента И, выход которого подключен к дополнительному входу дешифратора.

ОшыЬна

Авторы

Даты

1977-12-25—Публикация

1976-03-22—Подача