1

Изобретение относится к автоматике и вычислительной технике и может применяться в устройствах цифровой и зна1;твой индикации.

Известны устройства для индикации, содержащие блок ци(}ровых индикаторов, сое/шненный с выходами блоков ключей выбора разрядов, цифровых символов и запятой, блок управления, соединенный,со входом блок динаХПГЧбеКЬ0памяти и блока отсчета циклов, выход которого соединен с блоком ключей выбора разрядов и блоком буферной пама ти, выход соединен с шифратором цифровых симвопрв. Информация, наход щаяся в блоке памяти, выводится на цифровы и.ндикаторы, причем на индикацик выводятся как целые, так и десятичные дробные числа,- Для этого в блоке памяти для каляого цифрового символа (десятичного раэ ряда) отводится пять двоичных мест, из коTopboi четыре двоичных места отводятся для хранения кода цифрового символа и одно двоичное место для указания запятой . Наличие логической в пятом двоичном

месте любого десятичного говорит о том, что перёд этим десятичным разрядом должна быть запятая. Однако при этом способе индикации уменьшается полезная информационная емкость динамической памяти За счет искусственного увеличения раэрядности хранимых чисел (вместо четырех. двоичных разрядов используется пять двоичных разрядов).

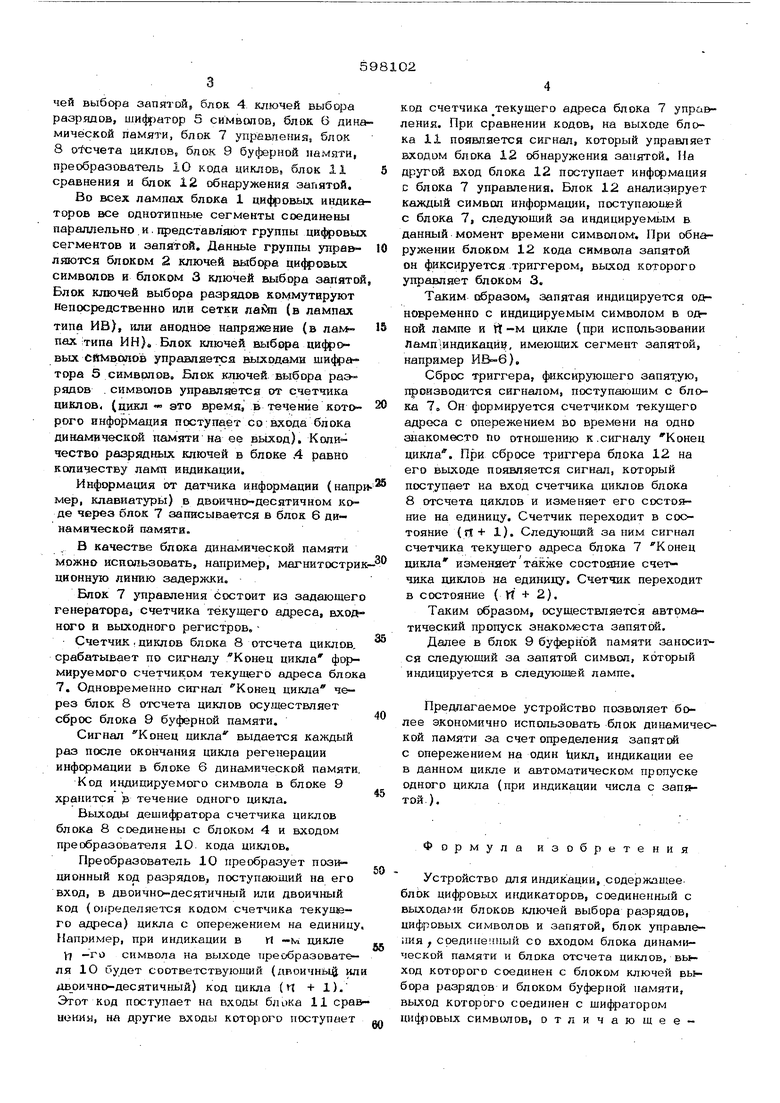

Целью изобретения являетЬя увеличение нопеэнрй информационной емкости динамической памяти, т.е. увеличение надежности. В предлагаемом устройстве это достигается тем, что в него введены последовательно соединенные преобразователь кода циклов, блок сравнения и блок обнаружения запятой, выход соединен со входом блока ключей выбора запятой и блока отсчета цикглов, выход которого соединен со входом преобразователя кода циклов.

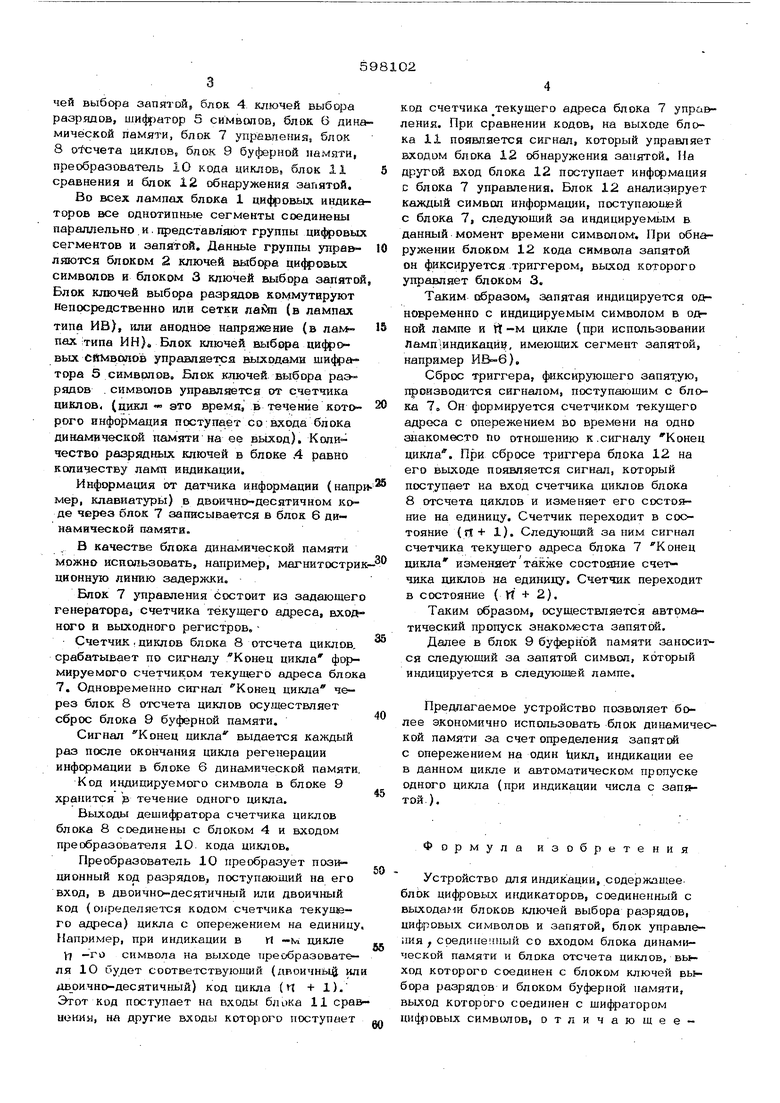

На чертеже показана блок-схема предлагаемого устройства.

Оно содержит блок 1 цифровых индикаторов, блок 2 ключей выбора символа , блок 3 KJiKf чей выбора запятой, блок 4 ключей выбора разрядов, ujHcj arop 5 символов, блок 6 дина мической памяти, блок 7 упраБпения8 блок 8 обсчета циклов, блок 9 буферной памяти, преобразователь 10 кода циклов, блок 11 сравнения и блок 12 обнаружения запятой. Во всех лампал блока 1 цифровых индика торов все однотипные сегменты соединены параллельно и. представляют группы цифровых сегментов и запятой. Данные группы управляются блоком 2 ключей выбфа ци(}ровых символов и блоком 3 ключей вьзбора запятой Блок ключей выбора разрядов коммутируют Непосредственно или сетки лайт (в лампах типа ИВ), или анодное напрян ние (в лампах типа ИН) Блок ключей выбора цифрt вых СйгМвслов управляется выходами шифра- тора 5 символов. Блок ключей выбора разрядов . символов управляется от счетчика циклов, (пшш « это время, в течение которого информация поступает со;входа блока динамической памяти на ее выход). Количество разрядных ключей в блоке ,4 равно количеству ламп индикации. Информация от датчика информации (напр мер, клавиатуры) а двоично-десятичном коде через блок 7 записывается в блок 6 динамической памяти. В качестве блока динамической памяти можно использовать, например, магнитостри ционную линию задержки. Блок 7 управления Состоит из задающег генератора, счетчика текущего адреса, вход ного а выходного регистров, Счетчик .циклов блока 8 отсчета циклов, срабатывает по сигналу Конец цикла формируемого счетчиком текущего адреса блок 7. Одновременно сигнал Конец ци1и1а через блок 8 отсчета циклов осуществляет сброс блока 9 буферной памяти. Сигнал Конец цикла выдается каждый раз после окончания цикла регенерации информации в блоке 6 динамической памяти Код индицируемого символа в блоке 9 хранится э течение одного цикла. Выходы деши4 атора счетчика циклов блока 8 соединены с блоком 4 и входом преобразователя 10 кода циклов. Преобразователь 10 преобразует позиционный код разрядов, поступающий на его вход, в двоично-десятичный или двоичный код (олределяеа-ся кодом счетчика текуаего адреса) цикла с опережением на единицу Например, при индикации в П -м цикле Y} -го символа на выходе преобразователя 10 будет соответствующий (дроичнь ил дв оично-десятичный) код цикла П +1). Этот код поступает на входы блока 11 сра иении, на другие входы которого поступает од счетчика текущего адреса блока 7 управения. При сравнении кодов, на выходе блоа 11 появляется сигнал, который управляет ходом блока 12 обнаружения занятой. На ругой вход блока 12 псютупает информация блока 7 управления. Блок 12 анализирует аждый символ информации, поступающей блока 7, следующий за индицируемым в анный момент времени символом-. При обнаужении блоком 12 кода символа запятой он фиксируется триггером, выход которого управляет блоком 3. Таким образом, запятая индицируется одновременно с индицируемым символом в одной лампе и rt-м цикле (при использовании ламп;индикацй$, имеющих сегмент запятой, например ), Сброс триггера, фиксирующего запятую, производится сигналом, поступающим с бло ка 7, Он формируется счетчиком текущего адреса с опережением во времени на одно знакоместо по отношению к.сигналу Конец цикла . При сбросе триггера блока 12 на его выходе появляется сигнал, который поступает на вход счетчика циклов блока 8 отсчета цяклов и изменяет его состояние на единицу. Счетчик переходит в состояние (я + 1). Следующий за ним сигнал счетчика текущего адреса блока 7 Конец шиша изменяет также состояние счетчика циклов на единицу. Счетчик переходит в состояние (Ц + 2). Таким образом, осуществляется автоматический пропуск 3HaKoivKCTa запятой. Далее в блок 9 буферной памяти заносится следующий за запятой символ, который индицируется в следующей лампе. Предлагаемое устройство позволяет более экономично использовать блок динамической памяти за счет определения запятда с опережением на один Ьикл, индикации ее в данном цикле и автоматическом пропуске одного цикла (при индикации числа с запятой ). Формула изобретения Устройство для индикации, содержащееблок цифровых индикаторов, соединенный с выходами блоков ключей выбора разрядов, цифровых символов и запятой, блок управления f среди е ный со входом блока динамической памяти и блока отсчета циклов, выход которого соединен с блоком ключей выбора разрядов и блоком буферной памяти, выход которого соединен с щифратором цифровых символов, отличающеес я тем, что, с целью увеличения надежности устройства, в него введены последовательно соединен1гьге преобразователь кода циклов, блок сравнения и блок обнаружения запятой ((ВЫХОД кпторого ооеднно н со входом блока ключей выбора занятой и блока, отсчета циклов, выход которого со тинен со входом преобразователя кода циклов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1974 |

|

SU560247A1 |

| Система передачи и приема сигналов контроля | 1981 |

|

SU999081A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ГИДРОЛОКАТОРА БОКОВОГО ОБЗОРА | 1993 |

|

RU2060516C1 |

| Устройство для индикации | 1989 |

|

SU1667150A1 |

| Устройство для индикации | 1983 |

|

SU1149306A1 |

| Устройство для измерения глубинных параметров нефтяной скважины | 1986 |

|

SU1423730A2 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| Устройство для автоматизированного управления процессом налива емкостей | 1986 |

|

SU1406121A1 |

| Устройство для цифровой индикации | 1981 |

|

SU1045226A1 |

| ЭЛЕКТРОННАЯ КЛАВИШНАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1973 |

|

SU395837A1 |

От атчг/(«

VHtpffflMOtfUU

Авторы

Даты

1978-03-15—Публикация

1976-07-21—Подача