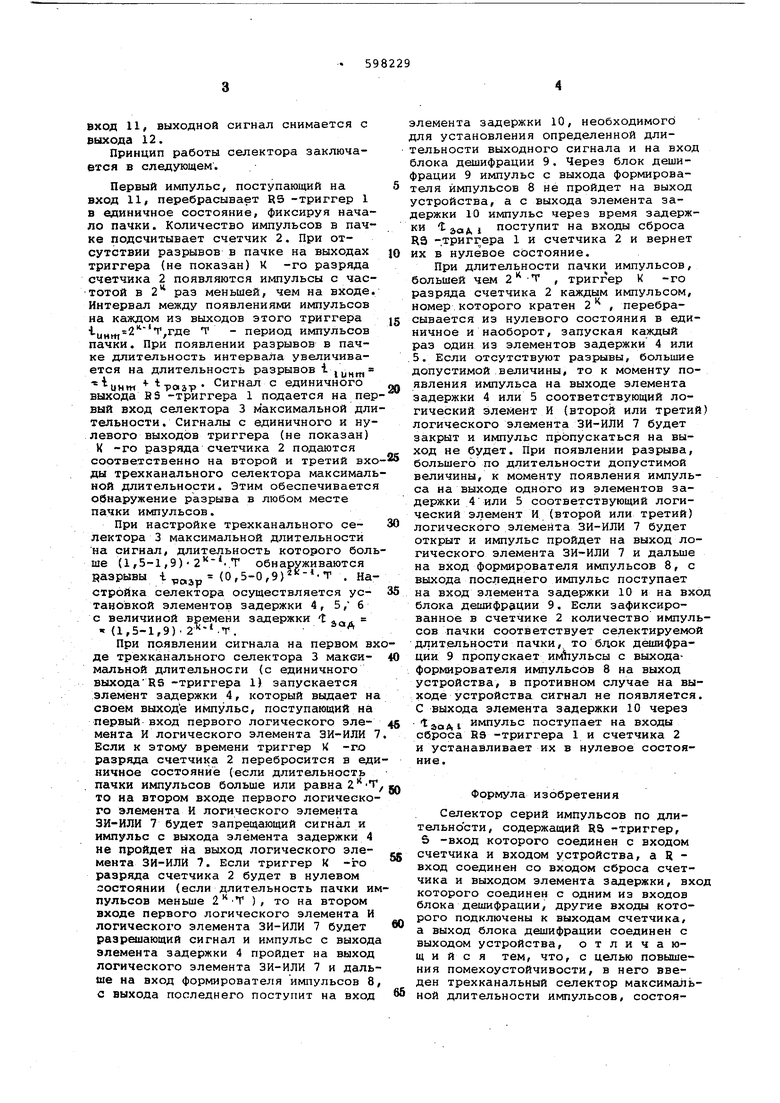

Изобретение относится к импульсной технике. Известен селектор импульсов, содержащий генератор эталонной частоты умножитель частоты, дополнительный модулятор частоты, диод с накоплением заряда, смеситель, фильтр, логические элемента И, реверсивный счетчик, счет чик, дополнительный делитель частоты триггер Шмитта ij. Недостатком такого устройства является его сложность Наиболее близким по технической сущности к данному изобретению являет ся селектор импульсов, содержащий КЗтриггер, & -вход которого соединен с входом счетчика и входом селектора а R-вход соединен со входом сброса счетчика и выходом элемента задержки вход которого соединен с одним из входов блока дешифрации, другие входы которого подключены к выходам счет чика, а выход блока дешифрации соединен с выходом селектора 2. Однако такой селектор не обладает достаточной помехоустойчивостью. Целью изобретения является повышение помехоустойчивости. Это достигается тем, что в предлагаемый селектор импульсов введен трекканальный селектор максимальной длительности импульсов, состоящий из трех элементов задержки, логического элемента ЗИ-ИЛИ и формирователя импульсов, выход которого соединен со входом элемента задержки, а вход формирователя импульсов подключен к выходу логического элемента ЗИ-ИЛИ, первый вход одного из логических элементов И, входящих в состав логического элемента ЗИ-ИЛИ, соединен через первый элемент задержки с выходом R3 -триггера, а второй вход указанного логического элемента И соединен с первым входом третьего логического элемента И, причем первые входы второго и третьего логических элементов И непосредственно, а вторые входы через элемент задержки соединены с выходами счетчика. На чертеже показана структурная электрическая схема предлагаемого селектора. Селектор импульсов содержит R5 триггер 1, счетчик 2, трехканальный селектор 3 максимальной длительности импульсов, состоящий из элементов задержки 4-6,- логического элемента ЗИИЛИ 7 и формирователя импульсов 8, блок дешифрации 9 и элемент задержки 10. Селектируемый сигнал подается на

ВХОД 11, выходной сигнал снимается с выхода 12.

Принцип работы селектора заключается в следующем.

Первый импульс, поступающий на вход 11, перебрасывает R5 -триггер 1 в единичное состояние, фиксируя начало пачки. Количество импульсов в пачке подсчитывает счетчик 2. При отсутствии разрывов в пачке на выходах триггера (не показан) К -го разряда счетчика 2 появляются импульсы с частотой в 2 раз меньшей, чем на входе. Интервал между появлениями импульсов на каждом из выходов этого триггера 1ц„ 2 т,где Т - период импульсов пачки 4 При появлении разрывов в пачке длительность интервала увеличивается на длительность разрывов 1 ,„..„

t.1 U П ГП

uwm pas-p- Сигнал с единичного выхода SS -триггера 1 подается на первый вход селектора 3 максимальной длительности. Сигналы с единичного и нулевого выходов триггера (не показан) К -го разряда счетчика 2 подаются соответственно на второй и третий вхо ды трехканального селектора максимальной длительности. Этим обеспечивается обнаружение разрыва в любом месте пачки импульсов.

При настройке трехканального селектора 3 максимальной длительности на сигнал, длительность которого больше (1,5-1,9) .Т обнаруживаются разрывы t дзр (0,5-0,9) . Настройка селектора осуществляется установкой элементов задержки 4, 5, 6 с величиной времени задержки t- -(1,5-1,9). .Т. . аад

При появлении сигнала на первом вхде трехканального селектора 3 максимальной длительности (с единичного выходаRS -триггера 1) запускается элемент задержки 4, который выдает на своем выходе импульс, поступающий на первый вход первого логического элемента И логического элемента ЭИ-ИЛИ 7 Если к этому времени триггер К -го разряда счетчика 2 перебросится в единичное состояние (если длительность пачки импульсов больше или равна то на втором входе первого логического элемента И логического элемента ЗИ-ИЛИ 7 будет запрещающий сигнал и импульс с выхода элемента задержки 4 не пройдет на выход логического элемента ЗИ-ИЛИ 7. Если триггер К -го разряда счетчика 2 будет в нулевом состоянии (если длительность пачки импульсов меньше 2 Т ) , то на втором входе первого логического элемента И логического элемента ЗИ-ИЛИ 7 будет разрешающий сигнал и импульс с выхода элемента задержки 4 пройдет на выход логического элемента ЗИ-ИЛИ 7 и дальше на вход формирователя импульсов 8, с выхода последнего поступит на вход

элемента задержки 10, необходимого для установления определенной длительности выходного сигнала и на вход блока дешифрации 9. Через блок дешифрации 9 импульс с выхода формирователя импульсов 8 не пройдет на выход устройства, а с выхода элемента задержки 10 импульс через время задержки аад, поступит на входы сброса R3 -триггера 1 и счетчика 2 и вернет их в нулевое состояние.

При длительности пачки импульсов, большей чем , триггер К -го разряда счетчика 2 каждым импульсом, номер которого кратен 2 , перебрасывается из нулевого состояния в единичное и наоборот, запуская каждый раз один из элементов задержки 4 или .5. Если отсутствуют разрывы, большие допустимой величины, то к моменту появления импульса на выходе элемента задержки 4 или 5 соответствующий логический элемент И (второй или трети логического элемента ЗИ-ИЛИ 7 будет закрыт и импульс пропускаться на выход не будет. При появлении разрыва, большего по длительности допустимой величины, к моменту появления импульса на выходе одного из элементов задержки 4или 5 соответствующий логический элемент И (второй или третий) логического элемента ЗИ-ИЛИ 7 будет открыт и импульс пройдет на выход логического элемента ЗИ-ИЛИ 7 и дальше на вход формирователя импульсов 8, с выхода последнего импульс поступает на вход элемента задержки 10 и на вх блока дешифрации 9. Если зафиксированное в счетчике 2 количество импулсов пачки соответствует селектируемо длительности пачки, то бдок дешифрации 9 пропускает импульсы с выходаформирователя импульсов 8 на выход устройства, в противном случае на выходе устройства сигнал не появляется С выхода элемента задержки 10 через t аоА I импульс поступает на входы сброса В9 -триггера 1 и счетчика 2 и устанавливает их в нулевое состояние.

Формула изобретения

Селектор серий импульсов по длительности, содержащий RS -триггер, 5 -вход которого соединен с входом счетчика и входом устройства, а R вход соединен со входом сброса счетчика и выходом элемента задержки, вх которого соединен с одним из входов блока дешифрации, другие входы которого подключены к выходам счетчика, а выход блока дешифрации соединен с выходом устройства, отличающийся тем, что, с целью повышения помехоустойчивости, в него введен трехканальный селектор максимальной длительности импульсов, состоямий из трех элементов задержки, ло-. гического элемента ЗИ-ИЛИ и формирователя, импульсов, выход которого соединен с входом элемента задержки, а вход формирователя импульсов подключен к выходу логического элемента ЗИ-ИЛИ, первый вход одного из логических элементов И, входящих в состав логического элемента ЗИ-ИЛИ, соединен через первый элемент задержки с выходом RS -триггера, а второй вход упо минутого логического элемента И соединен с первым входом третьего логического элемента И, причем первые входы ВТОРОГО и третьего логических элементов И непосредственно, а вторые входы через элемент задержки соединены с выходами счетчика. Источники информации, принятые во внимание при экспертизе: 1.патент США 3838338,кл.324-791), 2.Авторское свидетельство 451186, кл. Н 03 К 5/20, 1974,

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор серий импульсов по дли-ТЕльНОСТи | 1979 |

|

SU813768A1 |

| Устройство для измерения средней частоты импульсов нестационарного случайного потока | 1982 |

|

SU1049819A1 |

| Преобразователь пачки импульсов в прямоугольный импульс | 1975 |

|

SU577651A1 |

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

| Селектор импульсных сигналов | 1978 |

|

SU741446A1 |

| Селектор серий импульсов по длительности | 1983 |

|

SU1106008A1 |

| Микропрограммное устройство управ-лЕНия | 1979 |

|

SU842815A1 |

| Цифровой измеритель частоты заполнения радиоимпульсов | 1982 |

|

SU1161892A1 |

| Селектор импульсов по частоте следования | 1980 |

|

SU898604A1 |

| Устройство для измерения девиации частоты линейно-частотно-модулированного колебания | 1989 |

|

SU1711087A1 |

Авторы

Даты

1978-03-15—Публикация

1975-12-11—Подача