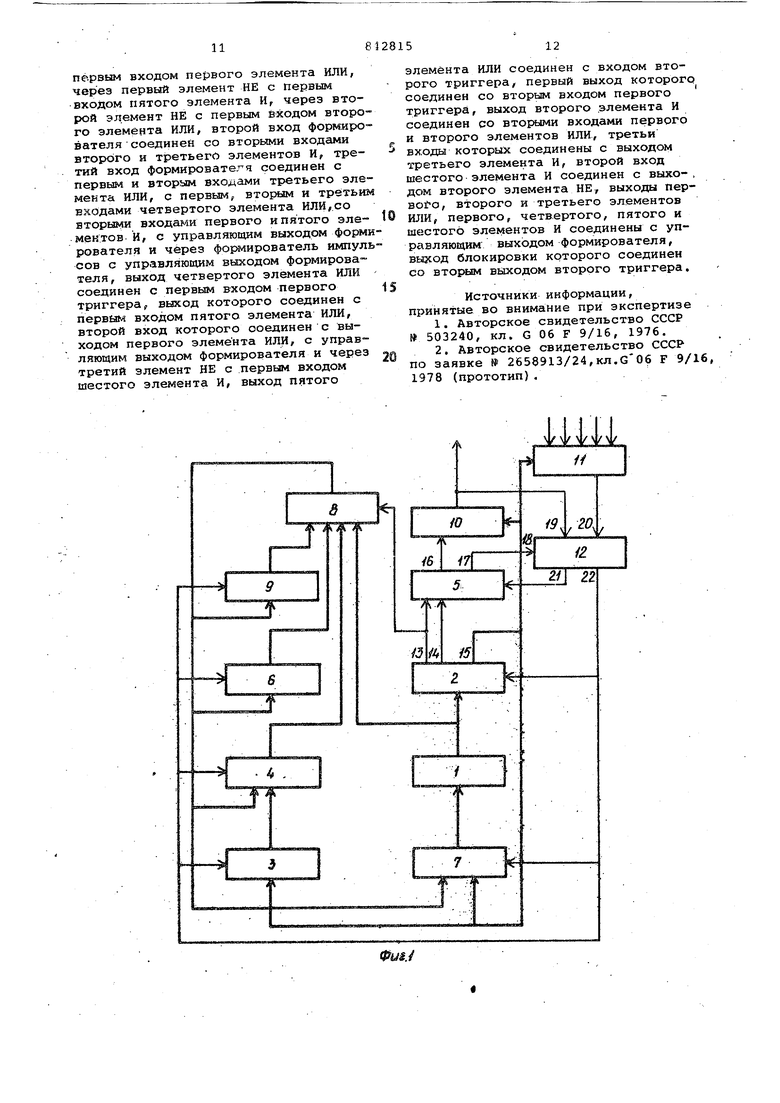

(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ равлянхцих сигналов, причем выходы-, сдвигового регистра и счетчика соеди нены соответственно с третьим и четвертым информационными входами коммутатора, управляющие входы сдвигового регистра, счетчика, блока опера тивной памяти, регистра, адреса опе{ративной Пс1мяти, регистра адреса мик рокоманд, регистра чкрокоманд соединены с управляющим вьаходом формирователя управляющих сигналов выход блокировки которого соединен с третьим входом дешифратора микрокоманд, первый и второй выходы которого соединены соответственно с информационным входом дешифратора функциональных сигналов и с первым входом формирователя управляющих сигналов, второй вход которого соединен с выходом селектора условий, группа информационных входов которого является группой входов условий устройства выход дешифратора функциональных сиг налов соединен с третьим входом формирователя управляющих сигналов и яв ляется выходом устройства, разрешающие входы селектора условий и дешиф.ратора функциональных сигналов соединены с выходом функциональной выборки регистра микрокоманд, информационные входы сдвигового регистра .и счётчика соединены с выходом коммутатора. Кроме того, селектор условий содержит коммутатор и триггер, причем группа информационных входов селекто ра соединена с группой входов коммутатора, выход и вход которого соединены соответственно с входом триггера и с разрешающим входом селектора, выход триггера соединен с выходом се лектора. Кроме того, формирователь управля ющих сигналов содержит элементы И, ИЛИ, НЕ и два триггера, причем пер- вый вход формирователя соединен с первыми входами первого, второго и третьего элементов И, с первым и лторым входгиян четвертого элемента И с первым входом первого элемента ИЛИ через первый элемент НЕ с первым вхо дом пятого элемента И, через второй элемент НЕ с первым входом второго элемента ИЛИ, второй вход формирователя соединен со входами вто рого и третьего элементов И, третий вход Формирователя соединен с первым и вторьм входами третьего элемен та ИЛИ, с первым, вторьт и третьим входами четвертого элемента ИЛИ, со вторыми входсми первого и йятогб эле ментов И, с управляющим выходом Формирователя и череэ фо{х а{рователь импульсов с управляющем выходом о&трователя, выход четвертого элемента ИЛИ соединен с первьм входом первого триггера, выход которого соединен с первым входом пятого элемента ИЛИ, второй Вход которого соедин еи с выхо дом первого элемента ИЛИ, с управляющим выходом формирователя и через третий элемент НЕ с первым входом шеС того элемента и, выход пятого элемента ИЛИ соединен с входом второго триггера, первый выход которого соединен со вторым входом первого триггера, выход второго элемента И соединен со вторыми входами первого и второго элементов ИЛИ, третьи входы которых соединены с выходом третьего элемента И, второй вхЬд шестого элемента И соединен с выходом второго элемента НЕ, выходы первого, второго и .третьего элементов ИЛи, первого, четвертого, пятого и шестого элементов И соединены с управляющим выходом формирователя, выход блокировки которого соединен со вторым выходом второготриггера. На фиг.1 представлена блок-схема устройства; на фиг.2 - схема селектора условий ; на фиг. 3 - схема формирователя управляющих сигналов. Устройство состоит из блока памяти микрокоманд, регистра 2 микрокоманд, регистра 3 адреса оперативной памяти, блока 4 оперативной памяти, дешифратора 5, микрокоманд, счетчика 6, регистра V адреса микрокоманд, коммутатора 8, сдвигового регистра 9, дешифратора 10 функциональных сигналов, селектора 11 условий формирователя 12 управляющих сигналов, а также содержит выходы 13-15 регистра микрокоманд, выходы 16 и 17 дешифратора микрокоманд, входы 18-20 и выходы 21 и 22 формирователя управляющих сигналов. Выход 13 является выходом поля управляющим коммутатором, выход 14 разряды поля кода .команды,выход 15- выход поля функциональной выборки, выход 21- сигнал блокировки дешифрации микрокоманды, выход 22 - яв ляется выходом сигналов, управляющих работой регистра микрокоманд, регистра адреса микрокоманд, регистра адреса оперативной памяти, оперативной памяти счетчика, сдвигового регистра. Схема селектора 11 условий (фиг.2) включает .в себя Коммутатор 23 и триггер 24. При выполнении микрокоманд УсОжиданиеловное ветвление четырехразрядный код анализируемого условия по вьгходу 15 регистра 2 микрокоманд позволяет получать на выходе коммутатора 23 истинное значение входного условия, которое запоминается иа триггере 24. Схема формирователя 12 управляюих сигналов (фиг.З) включает В себя элемент И 25, элемент ИЛИ 26 формирователь 27 импульсов, элементы ИЛИ 28 и 29, триггеры 30 и 31, элемекты И 32-34, элемент НЕ 35, элементы И 36 и 37, элементы ИЛИ 38 и 39, элемс;нты НЕ 40 и 41. и работает следующим образом.Сигнал Загрузка РАМ на выходе элемента ИЛИ 38. формируется при выполнении микрокоманд безусловного пе рехода (по входу 18),при выполнении микрокоманд Условное ветвление и Ожидание и обнаружении заданного условия и по входу 20 через элемент И 37 или заданного неусловия по входу 20 через элемент И 36. Сигнал Приращение РАМ на входе элемента И 25 вырабатывается при выполнении любой микрокоманды (на выводе элемента НЕ 40 единичное значение) , кроме микрокоманды Ожидаи при отсутствии условий для. формирования сигнала загрузка РАМ на выходе элемента ИЛИ 38. Сигнал Загрузка РАМ на выходе элемента ИЛИ 39 формируется после выполнения любой микрокоманды, кроме микрокоманды Ожидание (при этом на выходе .элемента НЕ 40 .значение логического нуля) и если не обнаружены заданные микрокомандной Ожидание условия (на выходе эле ментов И36 и И 37 значения логичес ких нулей).. . . Сигнал Выбор РОИ , на выходе элемента И 34 формируется при совпа дений сигналов с дешифратора 5 по входу 18. Сигналы Загрузка счетчика на выходе элемента И 32 и Приращение счетчика на выходе элемента И 33 вырабатывается соответственио при наличии и отсутствии сигнала на входе 18 и при появлении сигнала Синхронизация счетчика на входе 19 из дешифратора 10. Сигнал Синхронизация СР на выходе элемента ИЛИ 26 совместно с единичным сигналом Загрузка СР п входу 19 осуществляет параллельную загрузку информации в сдвиговый регистр 9, ас нулевым сигналом Загрузка .СР - сдвиг информации. Сигнал Загрузка на выходе формирователя 27 импульсов запускается по входу 19 из дешифратора 10 Сигнал Блокировка дешифрации на выходе триггера 31 устанавливается через элемент ИЛИ 29 или единичны сигналом Загрузка, РАМ и по выходу элемента ИЛИ 38, или единичншл сигналом триггера 30, который устанавливается через элемент ИЛИ 28 сигналс№4и Загрузка СР Загрузка РОЙ и Синхронизация счетчика по входу 19. Устройство работает следующим образсш. Микрокоманда,выбираемая из блока памяти 1 по ащзесу, хранимому в регистре 7, засылается в регистр 2 по управляющему сигналу выхода 22 формирователя 12. Выбранная микрокоманда „расшифровывается в дешифраторе 5 формируя соответствующие сигналы по выходам 16 и 17, Микрокоманда состоит из поля управлёния .(выход 13) , поля кода команды (выход 1,4), поля функционалыюй выборки (выход 15). Адрес очередной микрокоманды формируется в регистре 7 адреса мик.рокоманды. При выполнений микрокоманд, кроме микрокоманд безусловного перехода и условного ветвления при наличии логического уело- ВИЯ, единичный сигнал Приращение по выходу 22 формирователя 22 перед выполнением текущей микрокоманды .разрешает формирование адреса следующей микрокоманды увеличением на единицу текущего адреса микрокоманды. Если выбрана микрокоманда Действие , то она через выходы 13 и 14 регистра 2 расшифровывается в дешифраторе 5, а выход 15 регистра 2, задавая код функции (действия), поступает iia вход дешифратора 10, на выходе которого формируется сигнал, соответствующий заданному коду. Дешифратор. 10 построен по мультиплексному принципу. Если выполняется микрокоманда-безусловного перехода, то в регистр 7 заносятся старшие разряды адреса следующей микрокоманды с выходом 15 регистра 2 микрокоманды, а младшие разряды через.коммутатор 8 из блока Г памяти при задании в поле управлен кода 10 (.выход 13) регистра 2 микрокоманд или блока оперативной памяти 4 - при задание кода 11. Причем, -младшие разряды адреса следующей -. микрокоманды выбираются из ячейки блока 4 оперативйой памяти, определяемой регистрбм 3, или из ячейки блока 1 -памяти,- адрес которой увели-на. единицу относительно адреса 1..якрокоманды б-езусловного перехода, Приэтом п-роиСХодит блокировка дешифрации кода адреса, занесенного и в регистр 2 сигналом по выходу 21 фор-мйрователя 12. При выполнении микрокоманды условного в.етвле«ия в поле функциональной выборки регистра 2 задается код условия, в Поле управления - знак условия и направление, По которому изйлекается адрес ветвления. Селектор 11 условий позволяет определить наличие или отсутствие в данный момент заданного условия выдачей соответственно единичного и нулевого сигнала на выходе селектора И,который подается на вход формирователя 12. 1юрмирователь 12, сравнивая сигт налы, поступившие из селектора 11 условий и дешифратора 5 по выходу 17, выдает по выходу 22 сигнал Приращеняе РАМ ., если произошло их несовпадение. Т.е. задано отсутствие условия а оно обнаружено., или сигнал Загрузка АМ, если заданное условие обнаружено. Сигнал Приращение РАМ . увеличивает содержимое регистра 7 на единицу, а сигнал Загрузка РАМ позволяет загружать его содержимым из блока 1 памяти или из блока оперативной памяти в зависимос ти от заданного кода в поле управления регистра 2. Причем, младшие разряды адреса следующей микрокоманды выбираются из ячейки блока 4 оперативной памяти, определяемом регистро 3, или .из ячейки блока 1 памяти, адрес которой увеличен на единицу отно ситёльно адреса микрокоманды условного ветвления. При этом происходит блокировка дешифратора кода адреса, занесенного и в регистр 2 сигналом по выходу 21 формирователя 12. Изменение содержимого регистра 3 осуществляется микрокомандой Выбо РОН, в которой в поле функциональной выборки задан код адреса оперативной памяти. По управляющему сигна лу по выходу 22 формирователя 12 это код запоминается в регистре 3 и поз(воляет считать информацию из выбранной ячейки. Управление работой счетчика, сдви гового регистра, блока оперативной памяти осуществляется с помощью микрокоманды Действие, в поле функциональной выборки регистра 2 которой задается код, соответствую11|;ий каждому функциональнрму элементу По сигналам из дешифратора 10 и выходов 17 дешифратора 5 формирователь 12 управляющих сигналов выдает соответствующие сигналы: Загрузка,приращение счетчика , Загрузка, Сдвиг СР , Загрузка РОН. Направление потока информации при выполнении микрокоманд Действие задается кодом поля управления и кодом поля функциональной выборки ре гистра 2. При этом кодом поля управления задается источник информации: 00 -счетчик, 01-сдвиговый регистр, 10 - блок памяти, 11 - блок оператив ной памяти, а кодом поля информационной выборки - приемник. Таким образом, для сдвигового регистра, счет чика, блока пгшяти микрокоманд,блока оперативной Пс1мяти микропрограммио доступным является информация с трех направлений. При задании константы из блока 1 памяти информация выбирается из ячейки блока 1 памяти,адрес которой увеличен на единицу относительно адреса текущей микрокоманды. Если-в текущем цикле считывается микрокоманда, в которой задан режим ожидания, то код в поле функциональной выборки регистра 2 задает логическое условие, наличие которого необходимо для перехода к следуккцей миКроксжанде, т.е. для выхода из ре жима ожидания. При выполнении микрокоманды Ожидание изменения адрес микрокоманды при отсутствии логического условия не происходит, блокяруется занесение информации в регйстр микрокоманд, но в каждом микропрограммном цикле в четвертом такте в счетчик б прибавляется единица к коду, который занесен предварительно перед выполнением микрокоманды Ожидание. При этом формирователь 12 выдает соответствующие управляющие сигналы. При обнаружении заданного условия ожидания последовательность действий по формированию адреса следующей.микрокоманды такая же, как и при выполнении микрокоманды условного ветвления при наличии логического условия. При отсутствии логического условия и появлении сигнала Перевыполнение счетчика . на выходе счетчика 6 (не показан) формирователь 12 по выходу 22 изменяет на единицу содержимое реги.стра 7. Таким образом, обнаруживается длительное (больше заданного) отсутствие логического условия. При необходимости микропрограммной организации временной задержки в поле функциональной вь:борки микрокоманды Ожидание задается код условия сигнала Переполнение счетчика . Перед вь-полнением микрокоманды Ожидание в счетчик 6 заносится код, соответствующий необходимой временной задержки. Появление сигнала Переполнение счетчика на выходе счетчика 6 означает окончание временной задержки. Он обнаруживается;селектором условий,. Единичный сигнал селектора 11 условий разрешает формирователю 12 произвести загрузку младших разрядов ад реса следующей микрокоманды из ячейки, следующей за микрокомандой Ожидание . При построении микропрограмм для реализации возврата из микроподпрограмм используются ячейки блока 4 оперативной памяти. При необходимости обратиться к микро.подпрограмме - j-ro ранга непосредственно перед микроподпрограммой выполняются микрокома тда Выбор РОИ , стробирующая занесение информации с выхода 15 регистра 2 в регистр 3 и микрокоманда Загрузка РОН, формирующая импулье разрешения записи по .информационным входам в ячейку блока оперативной памяти, определяемой регистре 3, кода адреса возврата, поступающего из ячейки блока 1 памяти, адрес которой увеличен на единицу относительно адреса микрокоманды Загрузка РОН .. Для выхода из микроподпрограммы после выполнения последней микрокоманда микропрдпрограммы должнывыполняться микрокоманда Выбор.РОИ , стробирукяцая занесение информации с выхода 15 регистра 2 в регистр 3 и икрокоманда безусловного перехода. В рехйстр 7 заносятся старшие разряды адреса следующей микрокоманда с выхода 15 регистра 2, а младшие разряды через коммутатор 8 из ячейки блока 4 оперативной памяти. Таким образом, в регистре 7 сформирован адрес микрокоманды, к которо необходимо вернуться. Управление работой сдвигового регистра в режиме загрузки осуществляется с помощью микрокоманды Действие , -в поле управления которой задается код источника (00 - счетчик, 10 - блок памяти микрокоманд, 11 блок оперативной памяти), а в поле функциональной выборки - код, Соотве ствующий формированию управляющей сигнала Загрузки СР на выходе 22 формирователя 12 ... Управление работой сдвигового регистра в режиме сдвига осуществляется с помощью микрокоманДействиев поле управления которой задается вид сдвига,а в поле функциональной выборки - код, соответствующий, формированию управляющег сигнала Сдвиг СР на выходе 22 формирователя 12. Сдвиг в сдвиговом регистре осущес вляется в направлении старших разрядов. Код в поле управления микрокоманды в режиме сдвига определяет вид сдвига: 00 - сдвиг с установкой О в младшем разряде сдвигового регистра, 10 - сдвиг с установкой в младшем разряде, 01 - циклический сдвиг, 11 - преобразование последова тельной информации в параллельную. Изобретение позволяет расширить функциональные возможности и получит существенный выигрыш в аппаратуре для устройств, в которых есть необхо димость формирования последовательны управляющих воздействий/ последовательно-параллельного преобразования информации, формирования различных временных задержек и временного отсчета отсутствия логического условия, построений управляющей микропрограммы внешними запоминающими устройствами в реальном масштабе вре мени. Формула изобретения 1.Микропрограммное устройство уп равления, содержащее блок памяти мик рокоманд, выход которого соединен с информационным входом регистра микро команд и с первым информационным вхо дом коммутатора, второй инфориацион.ный .вход которого соед1 нен с выходом .блока оперативной памяти, адресный вход которого соединен с выходом рвгистра адреса оперативной памяти, управляющий вход коммутатора соедине с выходом управления регистра микрокоманд и с первым входом, дешифратора микрокоманд, второй вход которого сое динен с выходом кода команды регистрамикрокоманд, выход функциональной выборки которого соединен с первым информационным входом регистра с1дрёса микрокоманд и с информационным входом регистра ащреса оперативной памяти, выход коммутатора .соединен с информационным входом блока оперативной памяти иСО вторым информационным входом регистра .адреса микрокоманд, выход которого соединен со входом блока памяти микрокоманд, отличающееся тем, что, с целью расширение функциональных возможностей за счет возможности организации разветвления и циклов Микропрограммы, в него введены сдвиговый регистр,, счетчик, дешифратор функциональных сигналов, селектор условий и формирователь управляющих сигналов, причем выходы сдвигового регистра и счетчика соединены соответственно с третьим и четвертым . информационными входами коммутатора, управляющие входы сдвигового регистра, счетчика, блока оперативной памяти, регистра адреса оперативной памяти, регистра адреса микрокоманд, регистра микрокоманд соединены с управляющим выходом формирователя управляющих сигналов выход блокировки которого соединен с третьим входом .дешифратора микрокоманд, первый и второй выходы которого соединены соответственно с информационным входом дешифратора функциональных сигналов и с первым входом формирователя уйравляющих сигналов, второй вход которого соединен с выходом селектора, условий, группа информационных входов которого является группой условий устройства; выход дешифратора функциональных сигналов соединен с третьим входом формирователя управляющих сигналов и является рыходом устройства, разрешающие входы селектора условий и дешифратора Функциональных сигналов соединены с выходом функциональной выборки регистра микрокоманд, информационные входы сдвигового регистра и счетчика соединены с выходом коммутатора. 2.Устройство по п.1, отличающее с я тем,, что селектор условий содержит коммутатор и триггер, причем группа информационных входов селектора соединена с группой входов коммутатора, выход и вход koT6pOt6 соединены соответственно со входом триггера и с разрешающим входом селектора, выход триггера соединен с выхрдом селектора. 3.Устройство по П.1, о т л и ч аю щ ее с я .тем, что формирователь управляющих сигналов содержит элементы И, ИЛИ НЕ и два триггера, причем первый вход формирователя соединен с первыми входами первого, второго и третьего элементов И, спервым и вторым входгиш четвертого элемента И с

первым входом первого элемента ИЛИ, через первый элемент НЕ с первым входом пятого элемента И, через второй элемент НЕ с первым иродом второго элемента ИЛИ, второй вход формирователя соединен со вторыми входами второго н третьего элементов И, третий вход формироватег-я соединен с первым и вторым входами третьего элемента ИЛИ, с первым, вторым и третьим входами четвертого элемента ИЛИ,со вторыми входами первого и пятого элементов И, с управляющим выходом Формирователя и через формирователь импульсов с управляющим выходом формирователя, выход четвертого элемента ИЛИ соединен с первым входом первого триггера, выход которого соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом первого элемента ИЛИ, с управляющим выходом формирователя и через третий элемент НЕ с первым входом шестого элем€ нта И, выход пятого

элемента ИЛИ соединен с входом второго триггера, первый выход которого соединен со вторым входом первого триггера, выход второго .элемента И соединен со вторыми входами первого и второго элементов ИЛИ, третьи входы которых соединены с выходом третьего элемента И, второй вход шестого элемента И соединен с выхо-, дом второго элемента НЕ, выходы перBOto, второго и третьего элементов ИЛИ, первого, четвертого, пятого и шестого элементов И соединены с управляющим выходом формирователя, выход блокировки которого соединен со вторым выходом второго триггера.

Источники информации, принятые во внима:ние при экспертизе

1.Авторское свидетельство СССР 503240, кл. G 06 F 9/16, 1976.

2.Авторское свидетельство СССР

по заявке 2658913/24,кп.СОб F 9/1 1978 (прототип).

у у V ф W

I Л сдбигоВому } регистру 9

, К B/f оку оперативной панйти

X deu/uq pafn(y5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

| Устройство для отладки программ | 1988 |

|

SU1661771A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

f cvemi uf(y 6

jk К регистру S

К регистру 7

Kp fiucm/H/

Авторы

Даты

1981-06-30—Публикация

1979-08-27—Подача