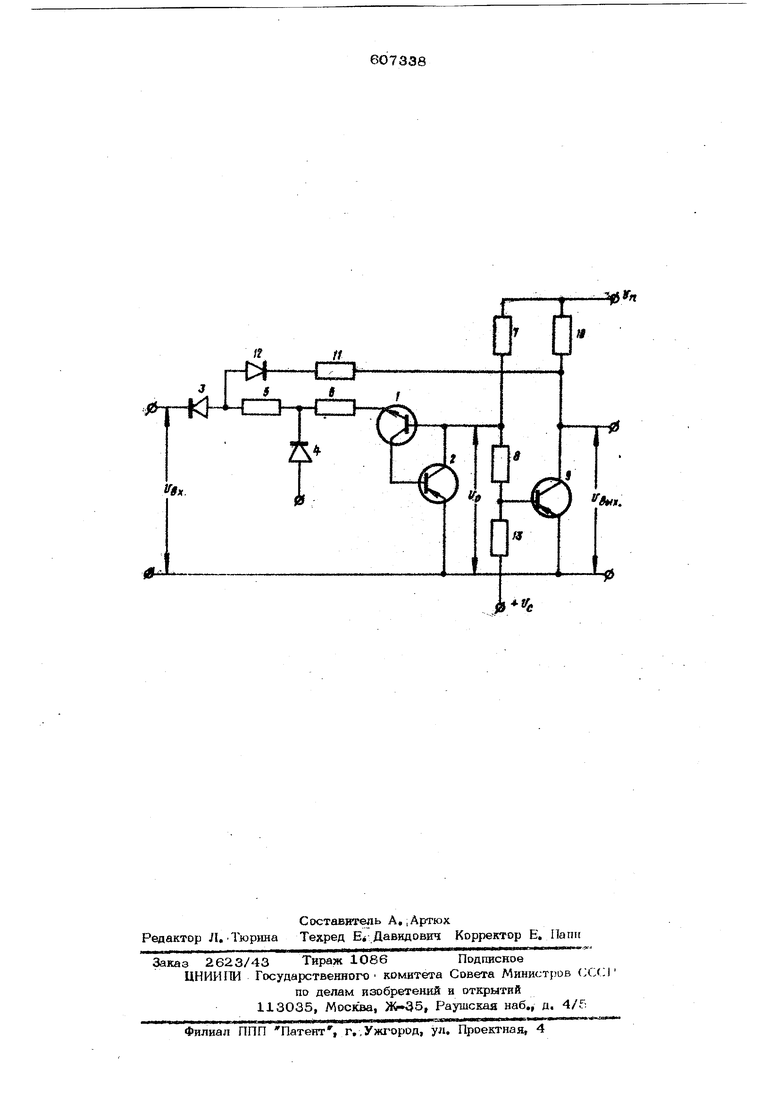

(54) ПОРОГСеЫЙ ЭЛЕМЕНТ подое ся положительное напряжение смещения Ijg.: При входном напряжении U , равном нугао, tpaHatffiTopb 1 и 2 нахоцятся в закрытом состоянии, при этом транзистор 9 открыт и выходное напряжение равно О. Точка соединения резисторов 8 и 13 че реэ базу транэистора 9 оказывается соедн™ ненной с эмиттерами травзнсгоров 2 и 9, Таким образом, точка соединения базы транзистора 1 и коллектора транзистора 2 оказывается под напряжением, снимаемым с резисторов Т и 8/ Точка соединения резисторов 10 и 11 через коллекторно-базовый переход транзистора 9 оказывается coe йшенной с эмиттерами транзисторов 2 и 9 Когда входное напряжение достигает уровня, раецого наиряженшо на резисторах 7-й 8, S цепи эыиттера траванстора I течет ток, который открьт 5ает транзистор 2, тем сак1ым увеличивая ток в эмиттерной цепи транзистора 1, Транзисторы 1 и 2 открываютсй лазинообразно. Точка соеди .нения резисторов 7 н 8 оказывается замкнутой через цепь коллектора транзистора 2 с эмиттерами транзисторов 2 и 9, На базе транзистора 9 действует нап.яжеиие смеше ния Т1 , которое ;3акрывает. транзистор 9, На выходе порогового элемента появляется йапряжеиие, равное напряжению питания, Пр этом через цепь обратной связи выходное напряжение подается на вход порогового элемента через резистор 11 и дион 12, Эт еше больше увеличивает ток в эмнттерной цепи транзистора 1 и блокирует пороговый елемепт. Так как выходное напряжение значительно выше вхопного напряжения, то диод 3 оказывае:1«я закрыт, и вход порогового элемента скс.нгоче-п от источника входного напряжения. Пороговый элемент запоминает достигнутый уровень входного напряжения и отключается от источника измеряе-мого напряжения. Для возвращения порогового элемента в исходное состояние необходимо на вход диода 4 подать положительное напряжение или соединить его на короткое время с эмиттером транзистора 2 , Формула изобретения Пороговый элемент, содержащий усилитель постоянного тока с репейной характеристикой, сослгошаий на двухтранзисторного эквивалента двухбазового диода, и выходного каскада на транзисторе, база которого через резйстивный делитель напряжения соединена с коллектором второго транзистора двухтранаисторного эквивалента двухбазового диода, эмиттер перового транзистора которого через псжледовательно соединенные резнстор и аиоц подключен ко входу пороговотго элемента, отличающийся тем, что, с целью уменыцения потребления тока от источника входных импульсов после сра батывания, в него введены дополнительные диод и резистор, включенные последовательно между коллектором транзистора выходного каскада и точкой соединения упомя нутых диода и резистора. Источники информации, принятые во вниманне при экспертизе: 1,Патент Японии № 31783., кл, 97/08 В 82, 1976, 2,Патент Великобр№гании № 12О2091, кл. Н 3 Т, 1970. --км

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговое устройство | 1974 |

|

SU526855A1 |

| Электронное реле времени | 1973 |

|

SU748558A1 |

| Генератор импульсов | 1978 |

|

SU790109A1 |

| Генератор импульсов | 1975 |

|

SU566313A1 |

| Генератор прямоугольных импульсов | 1979 |

|

SU855949A1 |

| Логический элемент задержки | 1973 |

|

SU470067A1 |

| Ключевой стабилизатор напряжения постоян-НОгО TOKA | 1978 |

|

SU845146A1 |

| Низковольтный стабилизатор постоянного напряжения "транзостаб 2 | 1977 |

|

SU746468A1 |

| БЕСКОНТАКТНОЕ РЕЛЕ ВРЕМЕНИ | 1973 |

|

SU374673A1 |

| Стабилизатор постоянного напряжения | 1978 |

|

SU736077A1 |

Авторы

Даты

1978-05-15—Публикация

1974-04-08—Подача