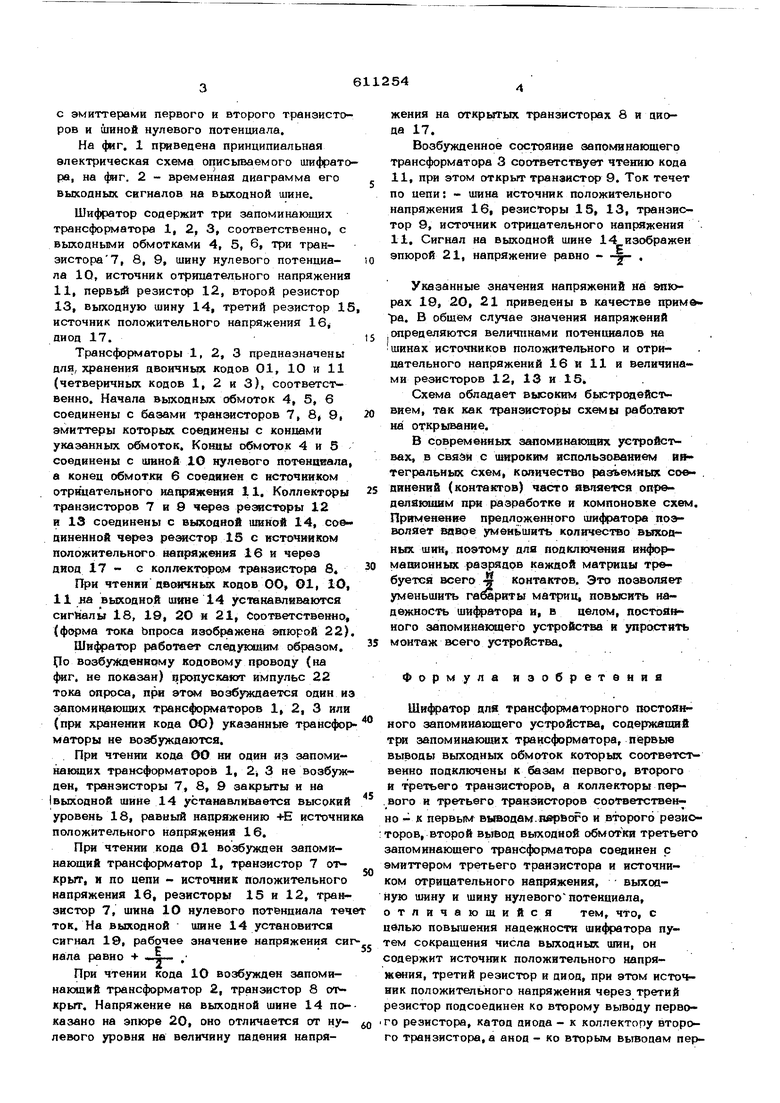

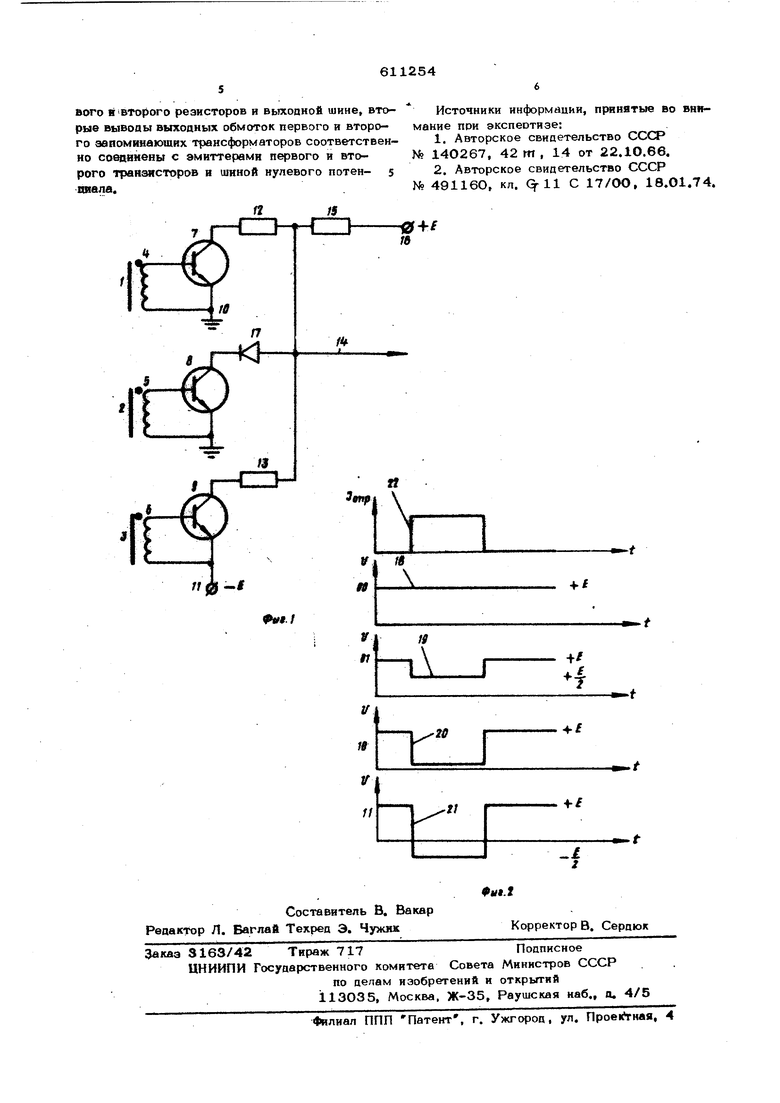

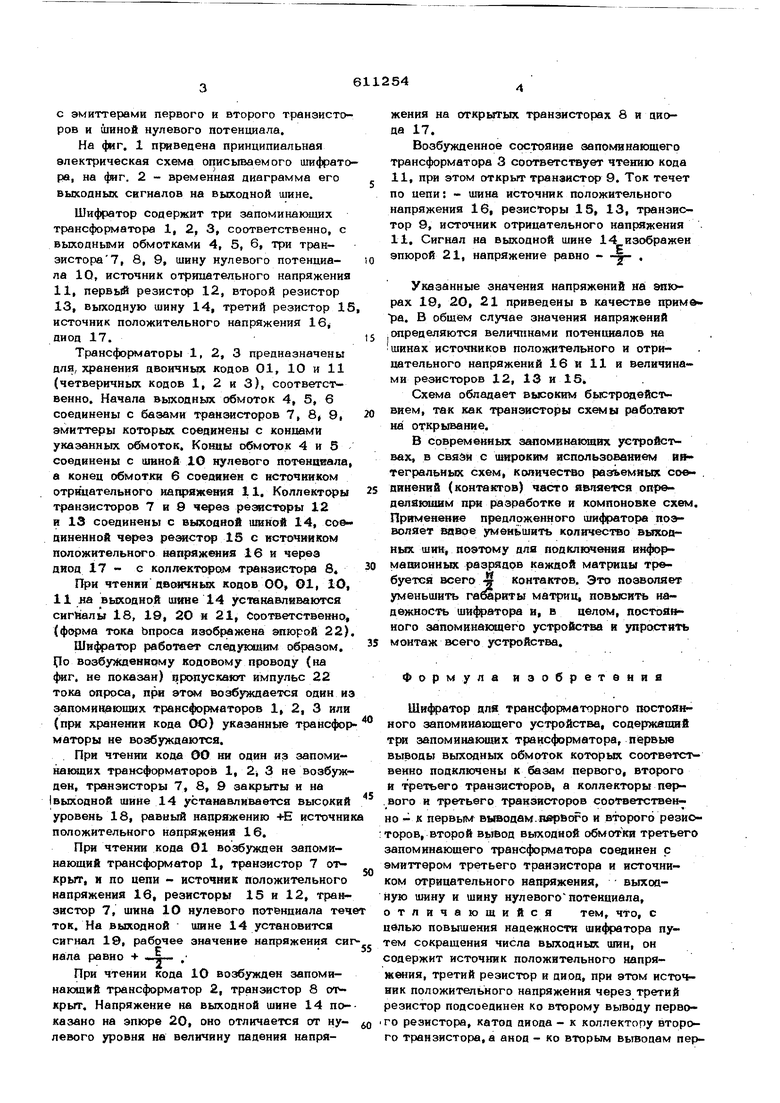

с эмиттерами первого и второго транзисторов и шиной нулевого потенциала. На фиг, 1 п|вдвеаена принципиальная электркческая схема описываемого шифрато ра, на фиг. 2 - временная диаграмма его выходных сигналов на выходной шине. Шифратор содержит три запоминающих трансформатора 1, 2, 3, соответственно, с выходными обмотками 4, 5, 6, три транэистора7, 8, 9, шину нулевого потенциала 10, источник отрицательного напряжения 11, первьй резистор 12, второй резистор 13, вькодную шину 14, третий резистор 15 источник положительного напряжения 16 диод 17. Трансформаторы 1, 2, 3 предназначены для, хранения двоичных кодов 01, 10 и 11 (четверичных кодов 1, 2 и 3), соответственно. Начала выходных обмоток 4, 5, 6 соединены с базами транзисторов 7, 8, 9, эмиттеры которых соединены с концами указанных обмоток. Концы обмоток 4 и 5 соединены с шиной 1О нулевого потенавала, а конец обмотки 6 соеоииен с источииком отрадательного напряжения 11. Коллекторы транзисторов 7 и 9 через ре сторы 12 и 13 соединены с выхоаной шиной 14, сое аиненной через рееткгтор 15 с источником положительного напряжения 16 и через диод 17 - с коллектором транзистора 8. При чтении двоичиьнс кодов 00, О1, iO, 11 ла выхоакой Ш1{ве 14 устанавливаются сигналы 18, 19, 20 и 21, Соответственно, (форма тока Ьпроса изображена ет1юрой 22) Шифратор работает следукяиим образом, flo возбужденному кодовому проводу (на фиг. не показан) пропускают импульс 22 тока опроса, при этом возбужоается один из запоминающих трансформаторов 1, 2, 3 или (при хранении кода ОС) указанные трансфор маторы не возбуждаются. При чтении кода ОС ки один из запоминакнпих трансформаторов 1, 2j 3 не возбуж дан, транзисторы 7, 8, 9 закрыты и на {выходной шине 14 устанавливается высокий уровень 18, равный напряжению +Е источни положительного напряжения 16. При чтении кода 01 возбужден запоминающий трансформатор 1, транзистор 7 открыт, и по цепи - источник положительного напряжения 16, резисторы 15 и 12, тракзистор 7, шина 10 нулевого потенциала теч ток. На выходной шине 14 установится сигнал 19, рабочее значение напряжения си нала равно - , При чтении кода 1О возбужден запоминающий трансформатор 2, транэд1стор 8 открыт. Напряжение на выходной шине 14 показано на дпюре 20, оно отличается от нулевого уровня на величину падения напряжения на открытых транзисторах 8 и диода 17, Возб5гжаенное состояние запоминающего трансформатора 3 соответс-пвует чтению кода 11, при этом открыт транзистор 9. Ток течет по цепи: - шина источник положительного напряжения 16, резисторы 15, 13, транзистор 9, источник отрицательного напряжения . 11, Сигнал на выходной шине 14 изображен эпюрой 21, напряжение равно - -§- , Указанные значения напряжений на эпюрах 19, 2О, 21 приведены в качестве приме ра, В общем случае значения напряжений сотрвдеяяются величинами потенциалов на шинах источников положительного и отрицательного напряжений 16 и 11 и величинами резисторов 12, 13 и 15i Схема обладает высоким быстрсадейст вием, так как транзисторы схемы работают на открывание. В современных запоминающих устройствах, в СВЯЗИ с широким использованием йй тегральиых схем, ксличес-гео раагьемйых сое- . оинений (контактов) часто является определакнонм при разработке и компоновке схем. Применение предложенного поэволяет вявое уменьшить количество выховных шии, поэтому дла подклю чения инфо ьмашюниьк разрядов каждой матрицы тробуетса всего § контактов. Это поселяет уменьшить гаадриты матриц, повысить надежность ши4 атора и, в целом, постоянного запоминаклаего устройства и упростить монтаж всего устройства. Формула изобретения для траисформа торного постоянного запоминающего устройства, содергжвший три запоминающих трансформатора, первые выводы выходных обмоток которых соответственно подключены к базам первого, второго и третьего транзисторов, а коллекторы пе вого и третьего транзисторов соответственно - к первым выводам.нового и второго резисоров, второй вывод выходной обмотки третьего запоминающего трансформатора соединен с миттером третьего транзистора и источником отрицательного напряжения, выхоаую шину и шину нулевогопотенциала, тличающийся тем, чТо, с елью повышения надежности шифратора пуем сокращения числа выходных шин, он одержит источник положительного напряжения, третий резистор и диод, при этом источиик положительного напряжения через третий резистор подсоединен ко второму выводу первого резистора, катод диода - к коллектору второго транзистора, а анод - ко вторым вьшодам первого liiBToporo резисторов и вьпсоаной шине, вторые вывоаы выходных обмоток первого и второ го ааноминающих трансформаторов соответственно совцинены с эмиттерами первого и второго транзисторов в шиной нулевого потен- 5 виала.

Источники информации, принятые во внимание ПРИ экспертизе:

1.Авторское свицетельство СССР № 140267, 42т , 14 от 22.10.66.

2.Авторское свидетельство СССР

№ 49116О, кл. Q-11 С 17/ОО, 18.01.74.

iZf+f

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор для трансформаторного постоянного запоминающего устройства | 1976 |

|

SU613399A1 |

| Генератор импульсов для электроэрозионной обработки | 1988 |

|

SU1599163A1 |

| ФОРМИРОВАТЕЛЬ ТОКА ЗАПРЕТА | 1969 |

|

SU233747A1 |

| Устройство для управления силовым транзисторным ключом | 1983 |

|

SU1133663A1 |

| Транзисторный ключ | 1987 |

|

SU1506536A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU637870A1 |

| ВЫСОКОВОЛЬТНЫЙ ИСТОЧНИК ПИТАНИЯ ДЛЯ ЭЛЕКТРОННО-ЛУЧЕВОГО ОБОРУДОВАНИЯ | 2007 |

|

RU2349020C1 |

| Преобразователь двоичного кода в биполярный код | 1984 |

|

SU1249706A1 |

| Шифратор для трансформаторного постоянного запоминающего устройства | 1976 |

|

SU637868A1 |

| УСТРОЙСТВО ПРОПОРЦИОНАЛЬНО-ТОКОВОГО УПРАВЛЕНИЯ ТРАНЗИСТОРНЫМ КЛЮЧОМ | 2003 |

|

RU2248091C1 |

Авторы

Даты

1978-06-15—Публикация

1976-10-27—Подача