I

Изобретение относится к автоматике и вычислительной технике.

Известно постоянное запоминающее устройство, содержащее адресные шины коммутационные матрицы и шифраторы. При общем числе разрядов п устройство содержит m шифраторов -разрядного кода. Выходные разрядные шины подключены к входам усилителей считывания и к первым выводам резисторов, другие концы которых соединены с шиной нулевого потенциала (1J. Наиболее близким к изобретению техническим решением является постоянное запоминающее устройство, содержащее дешифратор, выходы которого соединены с накопителем, разрядные шины которого соедииены с входами усилителей считывания и с соответствующими разделительными элементами, адресные, информационные шины и шину питания }2. Однако известные устройства имеют низкое быстродействие.

Целью изобретения является повышение быстродействия. В описываемом устройстве это достигается тем, что оно содержит ключевой элемент, выполненный на транзисторе, эмиттер которого подключен к разделительным элементам, а .1ектор - к шине питания.

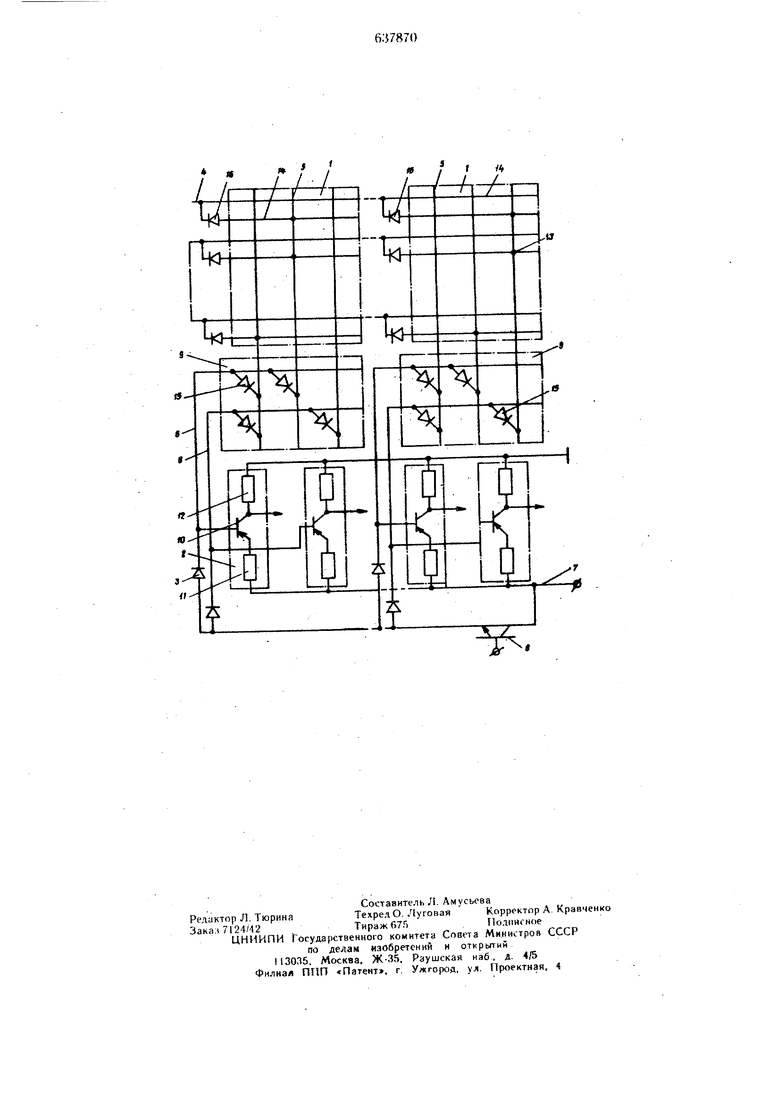

На чертеже представлена схема описы ваемого устройства.

Оно содержит накопители I, усилители 2 считывания, разделительные элементы (диоды) 3, адресные шины 4, информа ционные шины 5, разрядные шины 6, щину 7 питания, ключевой элемент (транзистор) 8, шифраторы 9 и дешифратор (на чертеже не показан).

При общем количестве ра..1рядов п устройства число шифраторов 9 и накопителей 1 равно т, при этом каждый шифратор 9 содержит разрядных шин 6 и формирует 7 -разрядный код.

На чертеже в качестве примера принято 2 и показано два шифратора 9.

Усилители считывания 2 содержат транзисторы 10, эмиттеры которых через ре.чисторы 1I соединены с шиной 7 питания, а коллекторы - через резисторы 12 соединены с шиной нулевого потенциала. Сопротивление резистора 12 в несколько раз больше сопротивления резистора И. Коллектор транзистора 8 соединен с шиной 7 питания, а эмиттер через разделительные элементы (диодм) 3 соединен с разрядными ижнами Ti и Г)азами (вход-чми) транзисторов 10 Количество диодов 3 равно количеству разрядов п. Точки 13 на пересечениях числовых шин 14 означают электрическое соединение указанных шин. На одной числовой шине 14 каждого накопителя 1 может быть не более одной точки 13, а на каждой информационной шине 5 количество точек колеблется от нуля до V. Электрическое соединение в точках 13 осуществляется в соответствии с запоминаемым кодом. Шифраторы 9 содержат диоды 15, установленные так, что при возбуждении одной из информационных шин 5 на разрядных шинах 6 шифратора 9 появляется соответствующий этой шине 5 двоичный код; при этом коду «1 соответствует отрицательный сигнал, а коду «О - отсутствие сигнала. На выбранную адресную шину 4, например шину с номером «О, подается отрицательный сигнал, на остальных шинах -- высокий уровень. На разрядных шинах 6 устанавливается код JO...O. Положительные сигналы на коллекторах открытых транзисторов 10 устанавливаются в первом и п-ом разрядах. Во втором и (п-1)-м разрядах на коллекторах закрытых транзисторов 10 сохраняется нулевой потенциал. Транзистор 8 при этом закрыт. Коллекторы транзисторов Ш подключаются к входам ТТЛ интегральных схем. После окончания действия отрицательного сигнала на адресной шине 4 на всех адресных шинах устанавливаются высокие УРОВНИ; запирающие диоды 16. Одновременно с окончанием отрицательного сигнала на шине 4 открывается транзистор 8, передавая через диоды 3 положительное запирающее напряжение на базы транзисторов 10; при этом диоды 15 и 16 закрыты. После окончания процесса запирания транзисторов 10 закрывается транзистор. 8, и схема устройства готова к вМбору любой адресной шины 4. Отсутствие шунтирующего вход усилителя считывания резистора обеспечивает высокое входное сопротивление усилителя, причем схема собственно усилителя достаточно проста и содержит один транзистор 10 и два резистора 11 и 12. По выбранной адресной шине 4 протекают базовые токи транзисторов 10, суммарный ток адресной шины 4 при п 40-50 может коммутироваться обычной ТТЛ-микросхемой (например, серии К155). Этим достигается существенное упрощение устройства, так как в адресных формирователях работают маломощные схемы, например микросхемы ИДЗ серии KI55. Кроме того, существенно снижается количество диодов 3, по сравнению с известным устройством (п диодов, вместо V диодов, причем п v). В описываемом устройстве обеспечивается высокое быстродействие при малой потребляемой мощности в адресных цепях и в адресных форр ирователях. Формула изобретения Постоянное запоминающее устройство, содержащее дешифратор, выходы которого соединены с накопителем, разрядные щииы которого соединены с входами усилителей считывания и с соответствующими разделительными элементами, адресные, информационные шины и шииу питания, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит ключевой элемент, выполненный на транзисторе, эмиттер которого подключен к разделительным элементам, а коллектор - к шине питания Источники информации, приняты1е во ан манне при экспертизе: 1.Патент Великобритании № 1193330 кл. С4А, С4Н, 1970. 2.Авторское свидетельство СССР № 344506, кл. G И С 17/00, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Запоминающее устройство | 1976 |

|

SU608197A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU763969A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1305775A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Запоминающее устройство | 1977 |

|

SU769627A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1101890A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

Авторы

Даты

1978-12-15—Публикация

1977-03-17—Подача