(54) РЕГИСТР СДВИГА

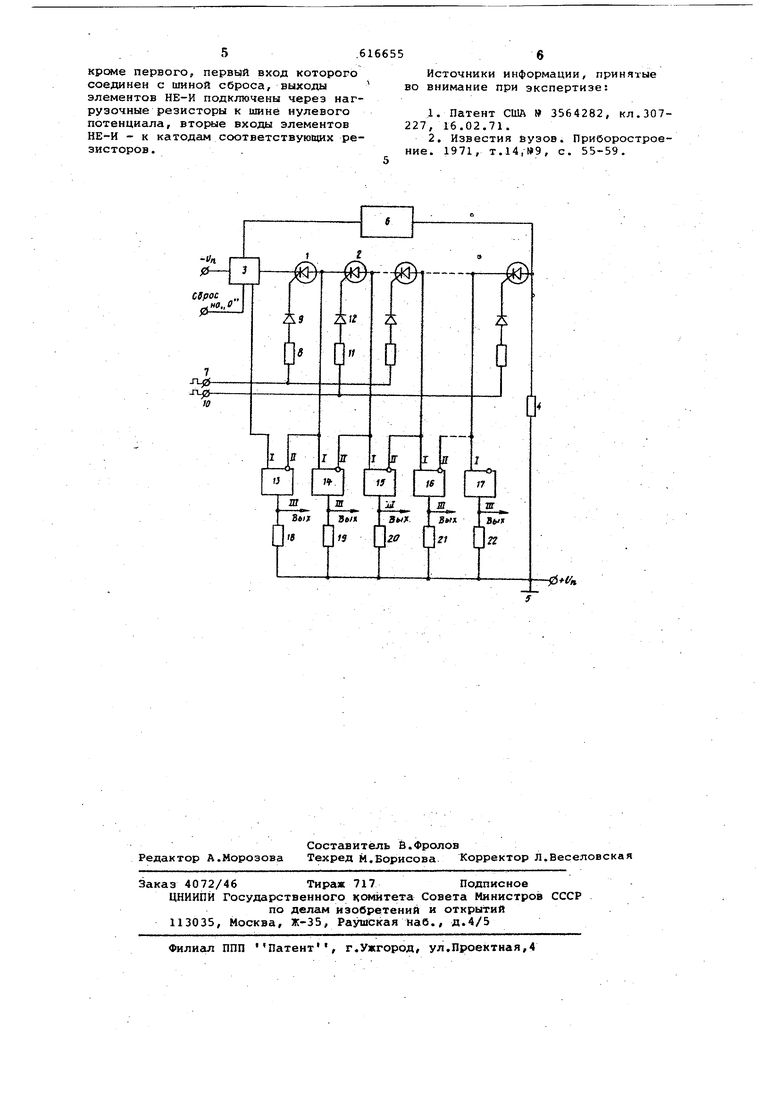

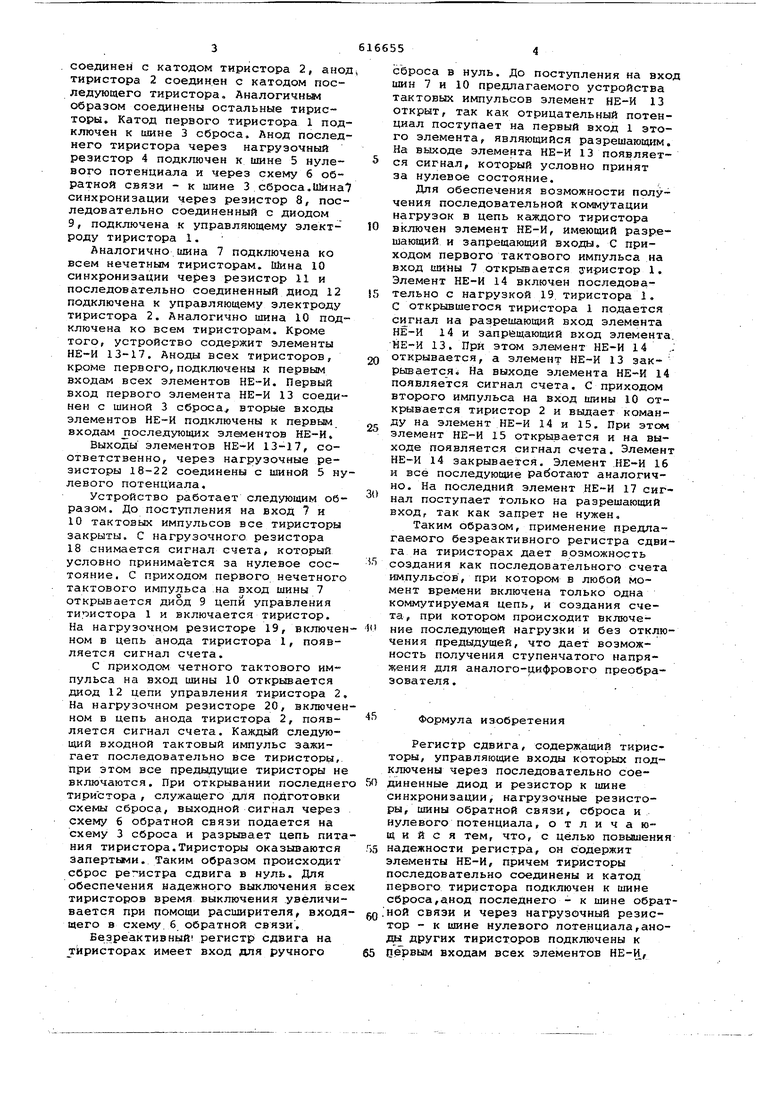

соединен с катодом тиристора 2, анод тиристора 2 соединен с катодом последующего тиристора, Аналогичньаи образом соединены остальные тиристоры. Катод первого тиристора 1 подключен к шине 3 сброса. Анод последнего тиристора через нагрузочный резистор 4 подключен к шине 5 нулевого потенциала и через схему б обратной связи - к шине 3 сброса,Шина7 синхронизации через резистор 8, последовательно соединенный с диодом 9, подключена к управляющему электроду тиристора 1,

Аналогично шина 7 подключена ко всем нечетным тиристорам. Шина 10 синхронизации через резистор 11 и последовательно соединенный диод 12 подключена к управляющему электроду тиристора 2. Аналогично шина 10 подключена ко всем тиристорам. Кроме того, устройство содержит элементы НЕ-И 13-17. Аноды всех тиристоров, кроме первого,подключены к первым входам всех элементов НЁ-И. Первый вход первого элемента НЕ-И 13 соединен с шиной 3 сброса вторые входы элементов НЕ-И подключены к первым входам последую1цик элементов НЕ-И.

Выходы элементов НЕ-И 13-17, соответственно, через нагрузочные резисторы 18-22 соединены с шиной 5 нулевого потенциала.

Устройство работает следующим образом. До поступления на вход 7 и 10 тактовых импульсов все тиристоры закрыты. С нагрузочного резистора 18 снимается сигнал счета, который условно принимается за нулевое состояние, С приходом первого нечетного тактового импульса .на вход шины 7 открывается диод 9 цепи управления тиристора 1 и включается тиристор. На нагрузочном резисторе 19, включенном в цепь анода тиристора 1, появляется сигнал счета.

С приходом четного тактового импульса на вход шины 10 открывается диод 12 цепи управления тиристора 2, На нагрузочном резисторе 20, включенном в цепь анода тиристора 2, появляется сигнал счета, Каждь1й следующий входной тактовый импульс зажигает последовательно все тиристоры при этом все предыдущие тиристоры не включаются. При открывании последнег тиристора , служащего для подготовки схемы сброса, выходной сигнал через схему б обратной связи подается на схему 3 сброса и разрывает цепь питания тиристора.Тиристоры оказываются Эаперты«1и. Таким образом происходит сброс регистра сдвига в нуль. Для обеспечения надежного выключения все тиристоров время выключения увеличивается при помощи расширителя, входящего в схему 6 обратной связи.

Веэреактивный регистр сдвига на тиристорах имеет вход для ручного

сброса в нуль. До поступления на вхо шин 7 и 10 предлагаемого устройства тактовых импульсов элемент НЕ-И 13 открыт, так как отрицательный потенциал поступает на первый вход 1 этого элемента, являющийся разрешающим. На выходе элемента НЕ-И 13 появляется сигнал, который условно принят за нулевое состояние.

Для обеспечения возможности получения последовательной коммутации нагрузок в цепь каждого тиристора включен элемент НЕ-И, имеющий разрешающий и запрещающий входы. С приходом первого тактового импульса на вход шины 7 открывается уиристор 1. Элемент НЕ-И 14 включен последовательно с нагрузкой 19. тиристора 1. С открывшегося тиристора 1 подается сигнал на разрешающий вход элемента НЕ-И 14 и запрещающий вход элемента НЕ-И 13. При ЭТОМ элемент НЕ-И 14 открывается, а элемент НЕ-И 13 эакрывается На выходе элемента НЕ-И 14 появляется сигнал счета. С приходом второго импульса на вход шины 10 открывается тиристор 2 и выдает команду на элемент НЕ-И 14 и 15. При этом элемент НЕ-И 15 открывается и на выходе появляется сигнал счета. Элемен НЕ-И 14 закрывается. Элемент НЕ-И 16 и всё последующие работают аналогично. На последний элемент 17 сигнал поступает только на разрешающий вход, так как запрет не нужен.

Таким образом, применение предлагаемого безреактивного регистра сдвига на тиристорах дает возможность создания как последовательного счета импульсов, при котором в любой момент времени включена только одна коммутируемая цепь, и создания счета, при котором происходит включение последующей нагрузки и без отключения предыдущей, что дает возможность получения ступенчатого напряжения для аналого-гдифрового преобразователя.

45 Формула изобретения

Регистр сдвига, содержащий тиристоры, управляющие входы которых подключены через последовательно сое5) диненные диод и резистор к шине

синхронизации, нагрузочные резисторы, шины обратной связи, сброса и нулевого потенциала, отличающийся тем, что, с целью повышения

55 надежности регистра, он содержит элементы НЕ-И, причем тиристоры последовательно соединены и катод первого тиристора подключен к шине сброса,анод последнего - к шине обратgQ.Hoa связи и через нагрузочный резистор - к шине нулевого потенциала,аноды других тиристоров подключены к

65 первым входам всех элементов НЕ-И,

креме первого, первый вход которого соединен с шиной сброса, выходы элементов НЕ-И подключены через нагрузочные резисторы к шине нулевого потенциала, вторые входы элементов НЕ-И - к катодам соответствующих резисторов..

Источники информации, принятые во внимание при экспертизе:

1.Патент США 3564282, кл.307227, 16.02,71.

2.Известия вузов. Приборостроение. 1971, т.14,9, с. 55-59.

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр сдвига | 1982 |

|

SU1049979A1 |

| Трехтактный регистр сдвига | 1973 |

|

SU454693A2 |

| Устройство для автоматического контроля печатных плат | 1985 |

|

SU1291902A1 |

| ТРЕХТАКТНЫЙ РЕГИСТР СДВИГА | 1971 |

|

SU298070A1 |

| Устройство контроля исправности генераторов импульсов | 1979 |

|

SU785959A1 |

| Элемент памяти | 1973 |

|

SU521604A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В БИПОЛЯРНЫЙ КОД | 2002 |

|

RU2218660C2 |

| Электронные часы с псевдострелочной индикацией | 1989 |

|

SU1653157A1 |

| Устройство для измерения амплитуды высокочастотных сигналов | 1981 |

|

SU999155A1 |

| Оптоэлектронное устройство для преобразования изображения | 1989 |

|

SU1718389A1 |

Ш I лгI if

I I Suf

8 1S I 2в

,

Авторы

Даты

1978-07-25—Публикация

1975-07-01—Подача