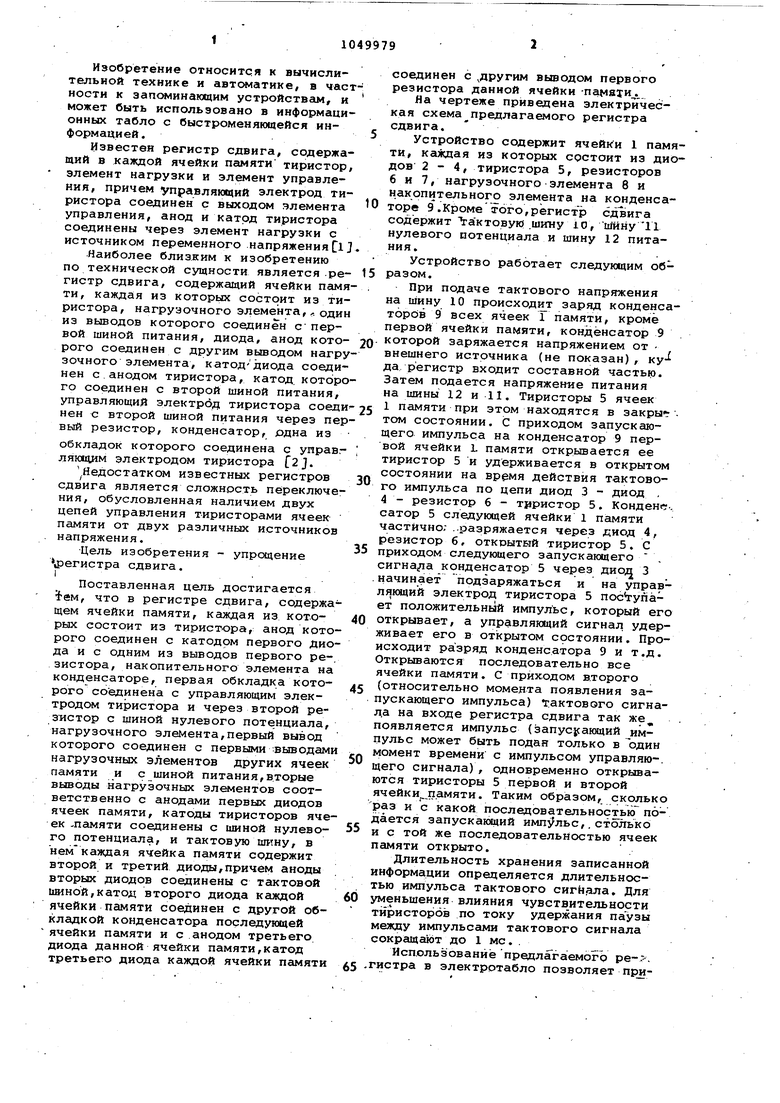

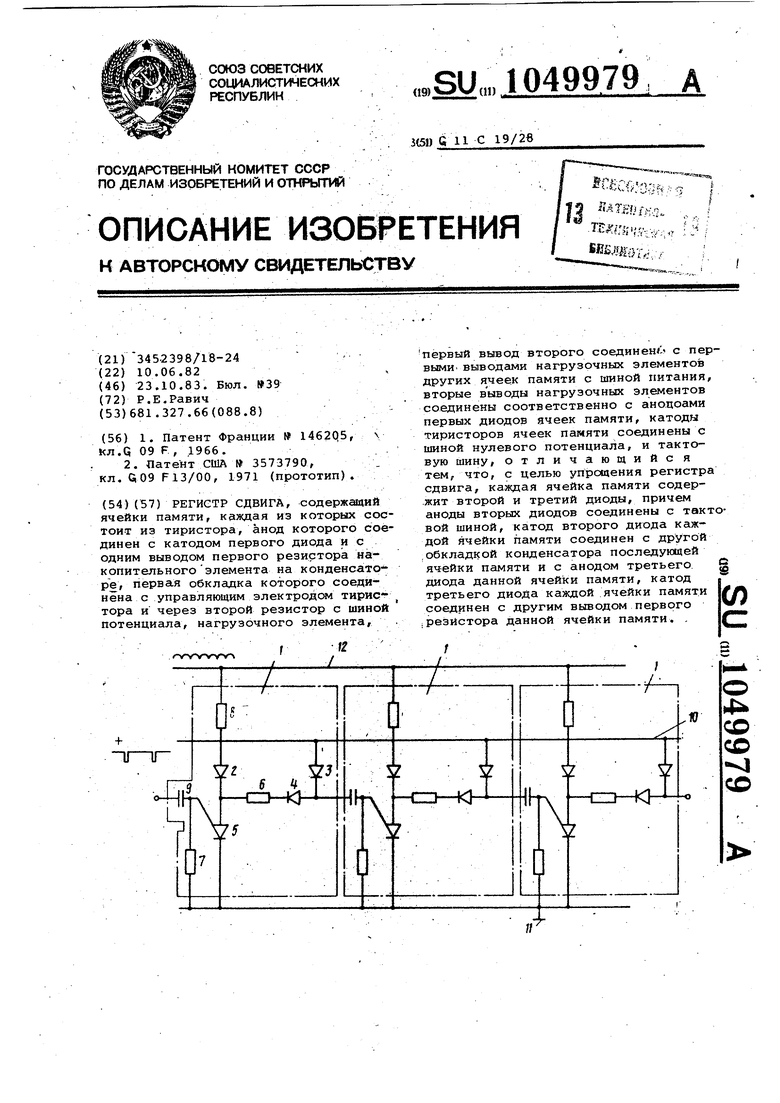

Изобретение относится к вычислительной технике и автоматике, в час ности к эапсмиинаксцим устройствам, и может быть использовано в информаци онных табло с быстрюменяюадейся информацией. Известен регистр сдвига, содержащий в каждой ячейки памяти тиристор элемент нагрузки и элемент управления, причем управляющий электрод тиристора соединен с выходом элемента управления, анод и катод тиристора соединены через элемент нагрузки с источником переменного напряженияCl Наиболее близким к изобретению по технической сущности является-регистр сдвига, содержащий ячейки памя ти, каждая из которых состоит из тиристора, нагрузочного элемента,,. оди из выводов которого соединен с первой шиной питания, диода, анод которого соединен с другим выводом нагру зочного элемента, катоддиода соединен с.анодом тиристора, катод, которо го соединен с второй шиной питания, управляющий электрод тиристора соеди нен с второй шиной питания через пер вый резистор, конденсатор, одна из обкладок которого соединена с управ.ляющим электродом тиристора f2J. Недостатком известных регистров сдвига является сложность переключения, обусловленная наличием двух цепей управления тиристорами ячеек памяти от двух различных источников напряжения. Цель изобретения - упрощение Лрегистра сдвига. Поставленная цель достигается ем, что в регистре сдвига, содержащем ячейки памяти, каждая из которых состоит из тиристора, анод которого соединен с катодом первого диода и с одним из выводов первого ре-, зистора, накопительного элемента на конденсаторе, первая обкладка которого соединена с управляющим электродом тиристора и через второй резистор с шиной нулевого потенциала, нагрузочного элемента,первый вывод которого соединен с первыми вьшодами нагрузочных элементов других ячеек памяти и с шиной питания,вторые выводы нагрузочных элементов соответственно с анодами первых диодов ячеек памяти, катоды тиристоров ячеек -памяти соединены с шиной нулевого потенциала, и тактовую , в немкаждая ячейка памяти содержит второй и третий диоды,причем аноды вторых диодов соединены с тактовой ишной,катод второго диода каждой ячейки памяти соединен с другой обкладкой конденсатора последующей ячейки памяти и с.анодом третьего, диода данной ячейки памяти,катод третьего диода каждой ячейки памяти соединен с .другим выводом первого резистора данной ячейки -памахи. Яа чертеже приведена электрическая схема предлагаемого регистра сдвига. Устройство содержит ячейки 1 памяти, каждая из которых состоит из диодов 2-4, тиристора 5, резисторов 6 и 7, нагрузочного элемента 8 и накопительного элемента на конденсаторе 9.Кроме того,регистр сдвига содержит IraKTOByw .шику 10, uftiriy 11 нулевого потенциала и шину 12 питания.. Устройство работает следующим образом. При подаче тактового напряжения на шину 10 происходит заряд конденсаторов 9 всех ячеек 1 памяти, кроме первой ячейки памяти, конденсатор 9 которой заряжается напряжением от внешнего источника (не показан) , куда регистр входит составной частью. Затем подается напряжение питания на шины 12 и 11. Тиристоры 5 ячеек 1 памяти при этом находятся в закрыв, том состоянии. С приходом запускающего импульса на конденсатор 9 первой ячейки L памяти открывается ее тиристор 5 и удерживается в открытом состоянии на врэмя действия тактового импульса по цепи диод 3 - диод , 4 - резистор 6 - трристор 5. Конденс-. сатор 5 следующей ячейки 1 памяти частично; .-хзазряжается через диод 4, резистор 6, ОТКРЫТБ1Й тиристор 5, С приходом следующего запускающего , сигна71а конденсатор 5 через дио; 3 начинает подзаряжаться и на управляющий электрод тиристора 5 поступает положительный импульс, который его открывает, а управляющий сигнал удерживает его в открытом состоянии. Происходит разряд конденсатора 9 и т.д. Открываются последовательно все ячейки памяти. С приходом в.торого (относительно момента появления запускающего импульса) тактового сигнала на входе регистра сдвига так же появляется импульс (запускеающий импульс может быть подан только в Ъдин момент времени с импульсом управляю-, щего сигнала), одновременно открываются тиристоры 5 первой и второй ячейки памяти. Таким образом, сколько раз и с какой последовательностью подается запускающий ,. столько и с той же последовательностью ячеек памяти открыто. Длительность хранения записанной информации определяется длительностью импульса тактового сигнала. Для уменьшения влияния чувствительности тиристоров по току удержания паузы между импульсами тактового сигнала сокращак)т до 1 мс. . Исп.ользованйё предлагаемого ре-. гистра в электротабло позволяет при3,10499794

менять лампы общего назначения 6 При этом надёжность предлагаемого

высвечиванием поля больших размеров,регистра сдвига по сравнению с изчто сокращает общее i количество ис .вестным, принятым за базовый объект,

точниквв света и ячеек управления ...повышается более чем в два раза за счет

ими. в несколько раз, упрощения управления его тиристорами.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕХТАКТНЫЙ РЕГИСТР СДВИГА | 1971 |

|

SU298070A1 |

| Трехтактный регистр сдвига | 1973 |

|

SU454693A2 |

| Двухтактный распределитель | 1983 |

|

SU1116449A1 |

| Кольцевой распределитель-формирователь управляющих импульсов | 1983 |

|

SU1088124A1 |

| Устройство для многоточечной сигнализации | 1983 |

|

SU1121690A1 |

| Регистр сдвига | 1984 |

|

SU1221681A1 |

| Ячейка памяти для регистра сдвига | 1974 |

|

SU1327186A1 |

| Реверсивный распределитель | 1974 |

|

SU734880A1 |

| Двухтактный распределитель | 1982 |

|

SU1051718A1 |

| Двухтактный распределитель | 1977 |

|

SU699675A2 |

РЕГИСТР СДВИГА, содержшдий ячейки памяти, каждая из которых состоит из тиристора, анод которого соединен с катодом первого диода и с одним выводом первого резистора накопительного элемента на конденсате pV, первая обкладка которого соединена с управляющим электродом тирис- , тора и через второй резистор с шиной потенциала, нагрузочного элемента. rVW первый вывод второго соединеш1 с первымИ выводгили нагрузочных элементов других ячеек памяти с шиной питания, вторые выводы нагрузочных элементов соединены соответственно с аноцоами первых диодов ячеек памяти, катоды тиристоров ячеек памяти соединены с шиной нулевого потенциала, и тактовую шину, отличающийся тем, что, с целью упрощения регистра сдвига, каждая ячейка памяти содер.жит второй и третий диоды, причем аноды вторых диодов соединены с тактовой шиной, катод второго диода каждой ячейки памяти соединен с другой .обкладкой конденсатора последующей ячейки памяти и с анодом третьего. § диода данной ячейки памяти, катод (Л третьего диода каждой ячейки памяти соединен с другим выводом первого ,резистора данной ячейки памяти. , СО со со VVV

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для изготовления адресных бандеролей из бумажной ленты в адресопечатающей машине | 1924 |

|

SU1462A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США 3573790, кл | |||

Авторы

Даты

1983-10-23—Публикация

1982-06-10—Подача